FPGA 入门 —— D 触发器仿真

FPGA 入门 —— D 触发器仿真

实验目的

-

在 Quartus 中自己用门电路设计一个 D 触发器,并进行仿真,时序波形验证

-

在 Quartus 中直接调用一个 D 触发器电路,进行仿真,时序波形验证,与 1 做比较

-

在 Quartus 中用 Verilog 语言写一个 D 触发器,进行仿真验证,与 2 做比较

实验原理

前面我们已经介绍了 D 触发器和一些相关的原理,如果还不知道什么是 D 触发器的可以看我的前一篇博客:FPGA 入门 —— D 触发器入门

新建项目

这里我们选择新建项目的路径:

注意:这里的名称要与 Module 的名称一致,不然要报错

这里我们选择新建空项目:

我们选择先不添加文件,后面再进行添加:

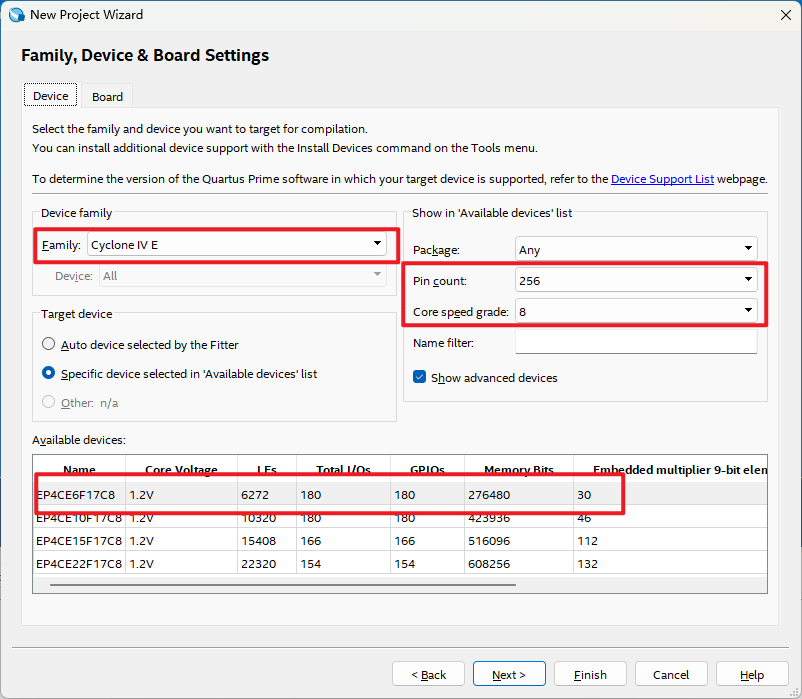

这里我们使用的型号是 EP4CE6F17C8 ,属于 Cyclone IV 系列,Core speed grade(堆芯速度等级)为 8 ,Pin count(引脚数量)为 256 ,我们可以先确定这两个参数,然后下面出现的第一个型号就是我们需要的:

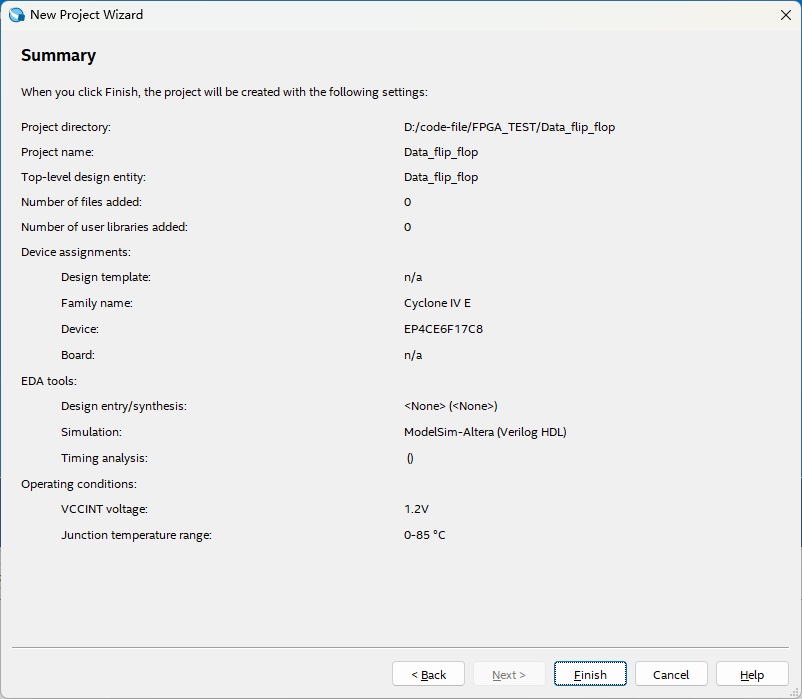

由于我们使用的是 Altera 的开发板,所以这里需要使用 ModelSim-Altera ,开发语言选择 Verilog HDL 语言:

下图页面是一些数据和配置信息:

门电路设计 D 触发器

D 触发器设计

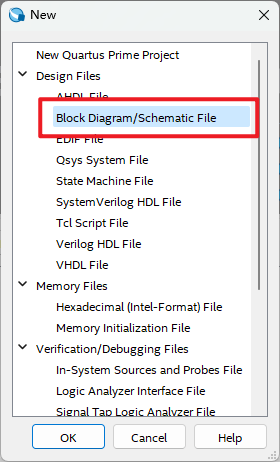

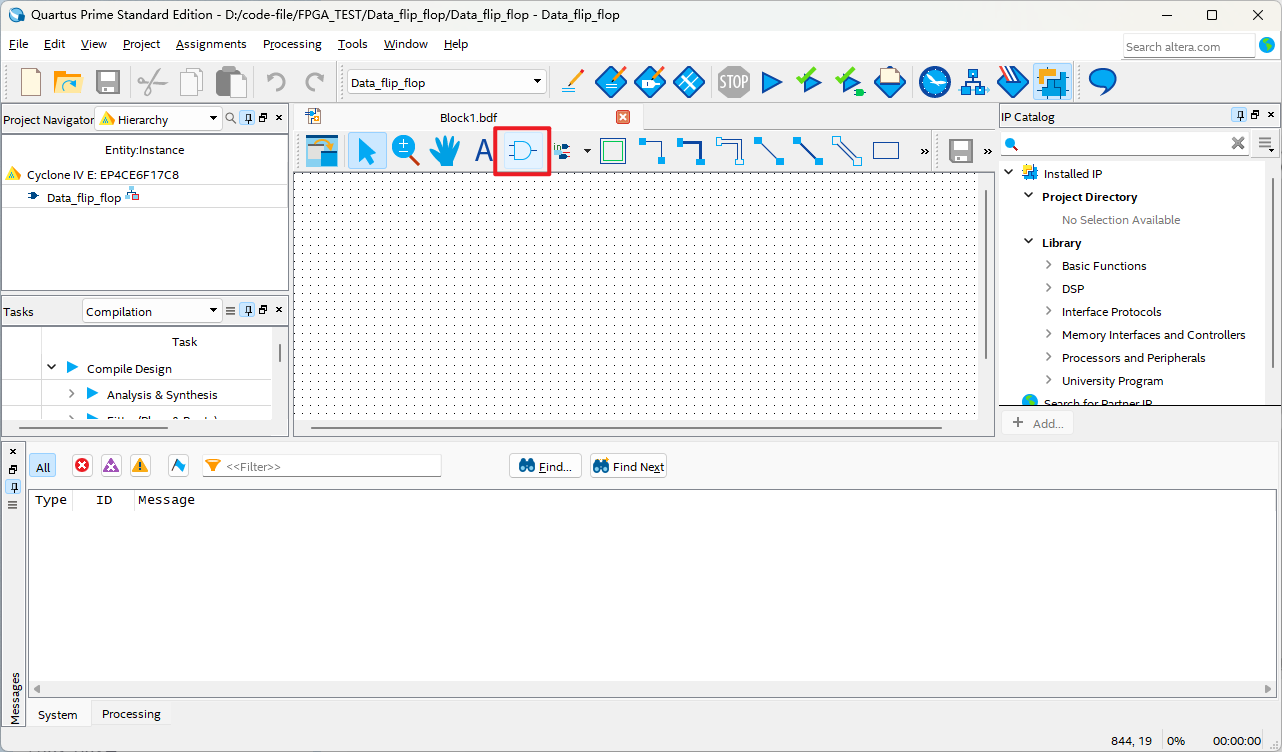

首先我们需要新建原理图文件:

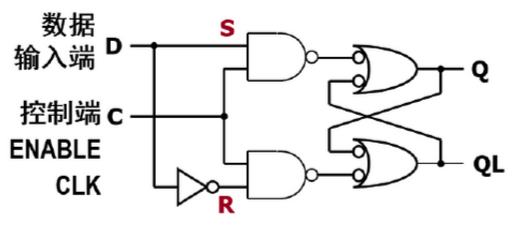

这里我们需要知道 D 触发器的原理图:

然后我们需要添加

我们可以直接查找对应的元器件或者输入元器件名称直接查找:

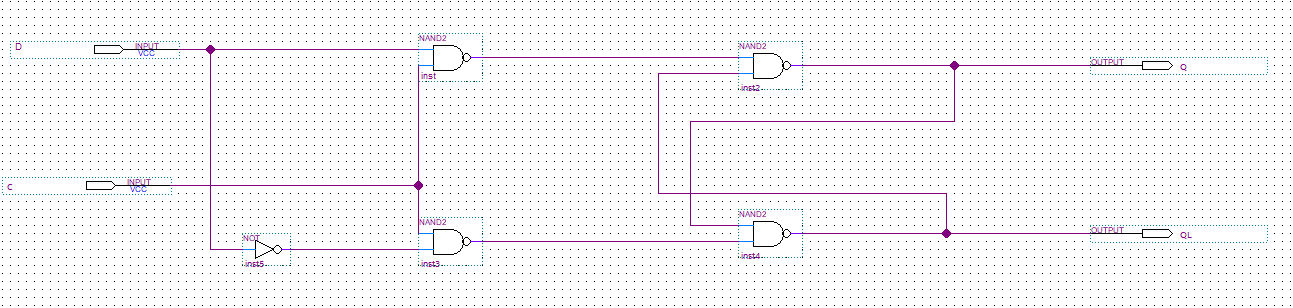

D 触发器需要 4 个 nand2 与非门,1 个 not 非门,2 个输入管脚和 2 个输出管脚,并连线,最终如下图:

编译

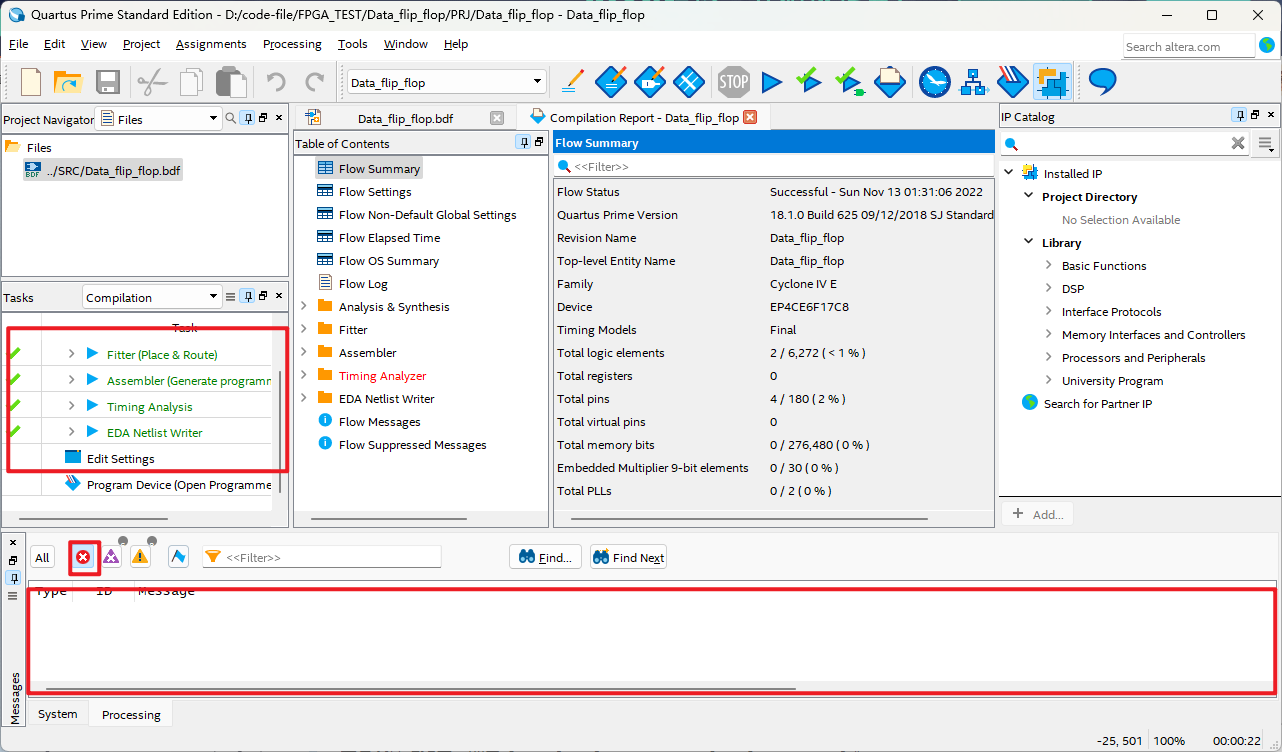

我们已经设计了 D 触发器的原型,这里要进行编译,无报错可以进行下一步:

这里我们点击报错信息,这里没有报错就说明可以进行下一步

查看硬件电路图

这里我们需要查看硬件电路图,看是否合理,不合理就要进行修改:

这里我的硬件电路图如下:

波形仿真

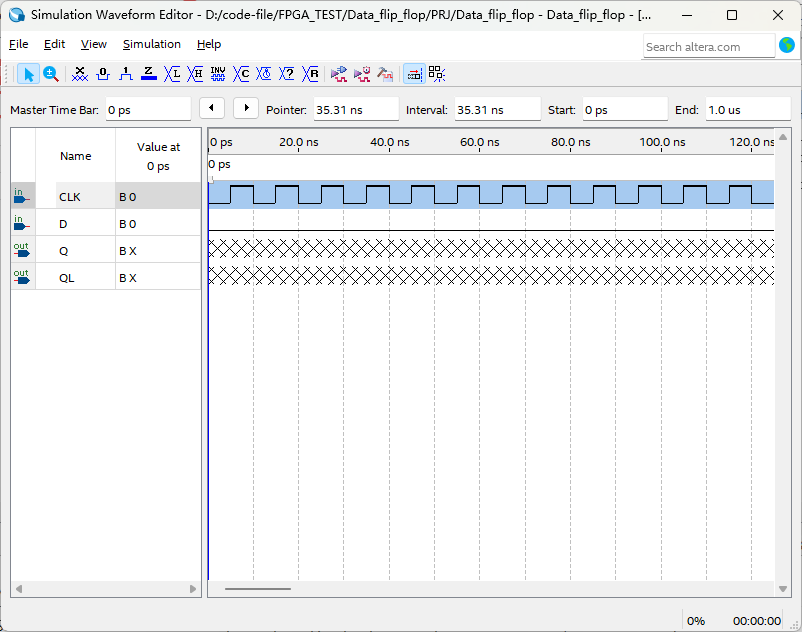

新建波形图文件:

选择要输入的波形:

然后点击 OK 即可看到如下波形:

编辑输入 CLK ,产生时钟信号:

输入 D 中随机选取几段设置高/低电平:

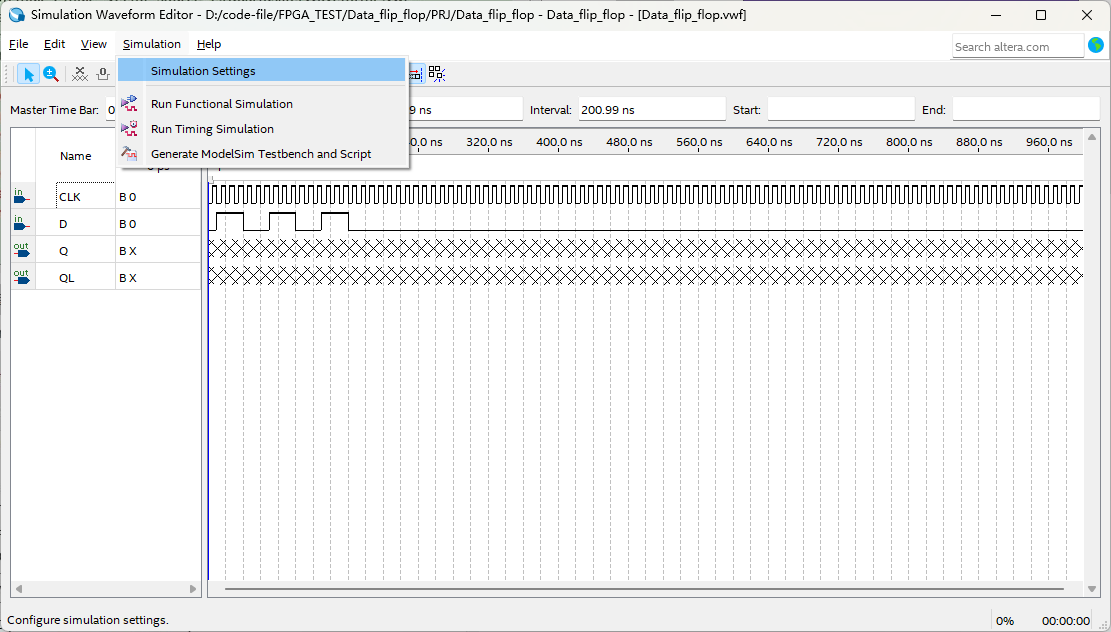

功能仿真

点击进行仿真:

调用 D 触发器

这里我们需要重新创建项目

前面的步骤均相同,这里我们选择直接添加 D 触发器进行仿真,元件名为 dff :

编译

波形仿真

这里我们波形仿真的方法和上面的仿真方法一样,就不进行过多介绍了

Verilog HDL 实现 D 触发器

代码设计

D 触发器代码:

module Delayff(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号

begin

Q <= D;//上升沿有效的时候,把d捕获到q

end

endmodule

仿真测试代码:

`timescale 1ns / 1ns

module Delayff_tb;

reg CLK,D;

wire Q;

Delayff u1(.D(D),.CLK(CLK),.Q(Q));

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;//人为生成毛刺

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #20 CLK <= ~CLK;//半周期为20ns,全周期为40ns的一个信号

endmodule

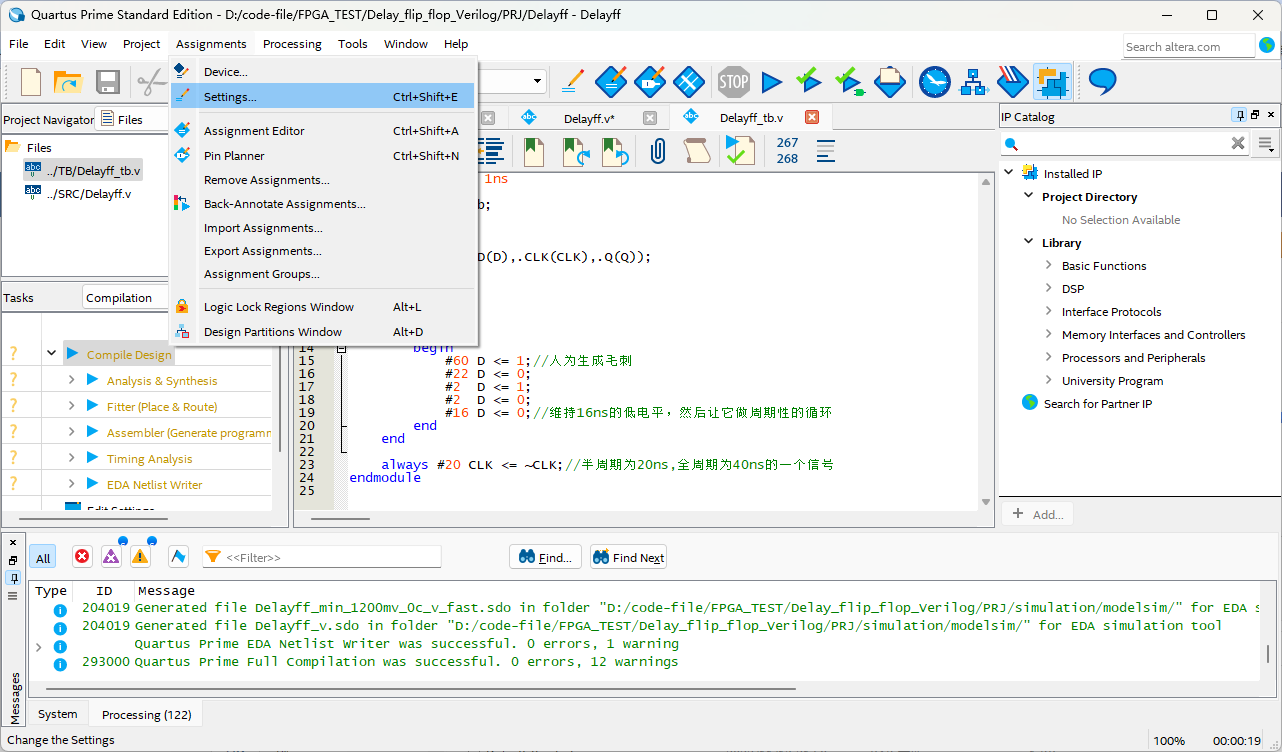

绑定仿真项

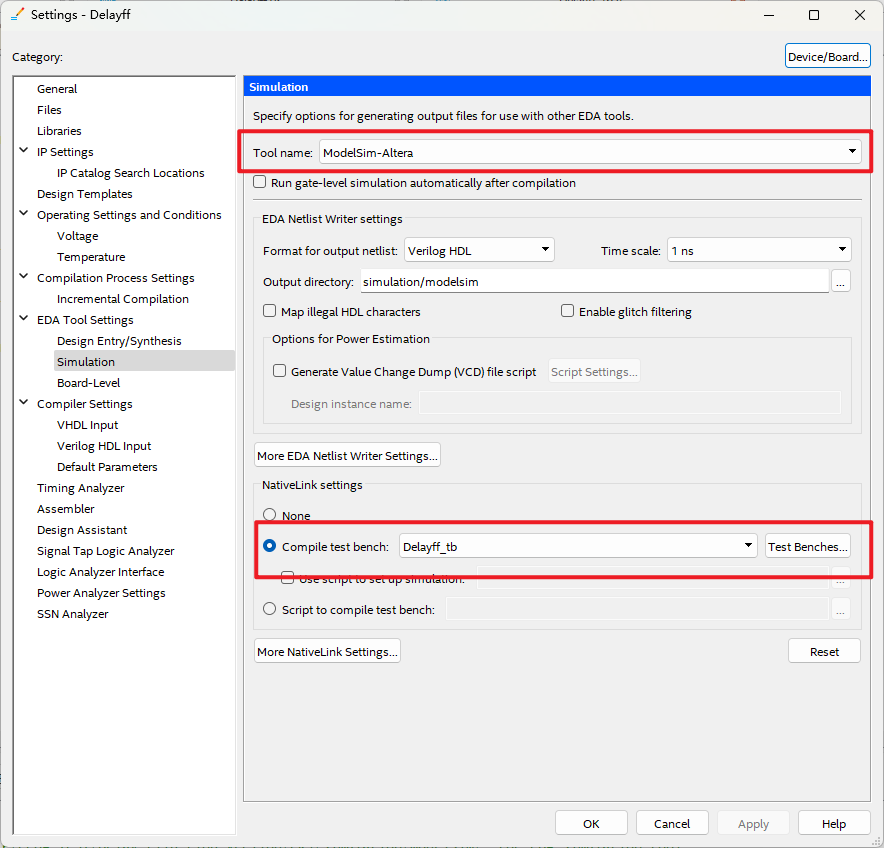

我们需要在这里绑定我们的仿真的源代码文件:

这里仿真软件需要选择 Model-Altera ,然后 Test Benches 文件选择我们的仿真代码文件:

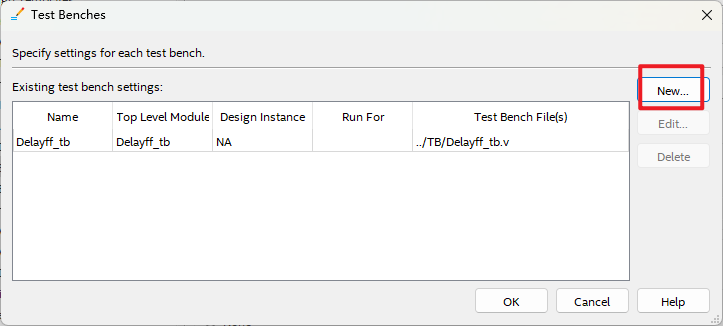

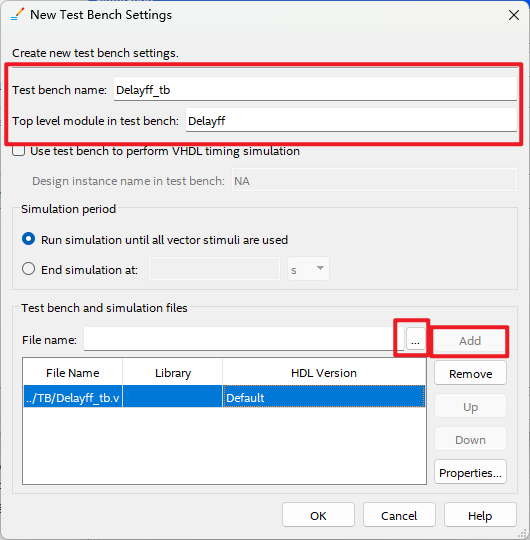

这里选择新建:

这里需要先点击 add 再点 ok

最后添加完成就可以进行仿真了

运行仿真

这里不采用通过代码仿真,采用和上述同样的仿真方式,就不过多介绍

运行测试

仿真结果

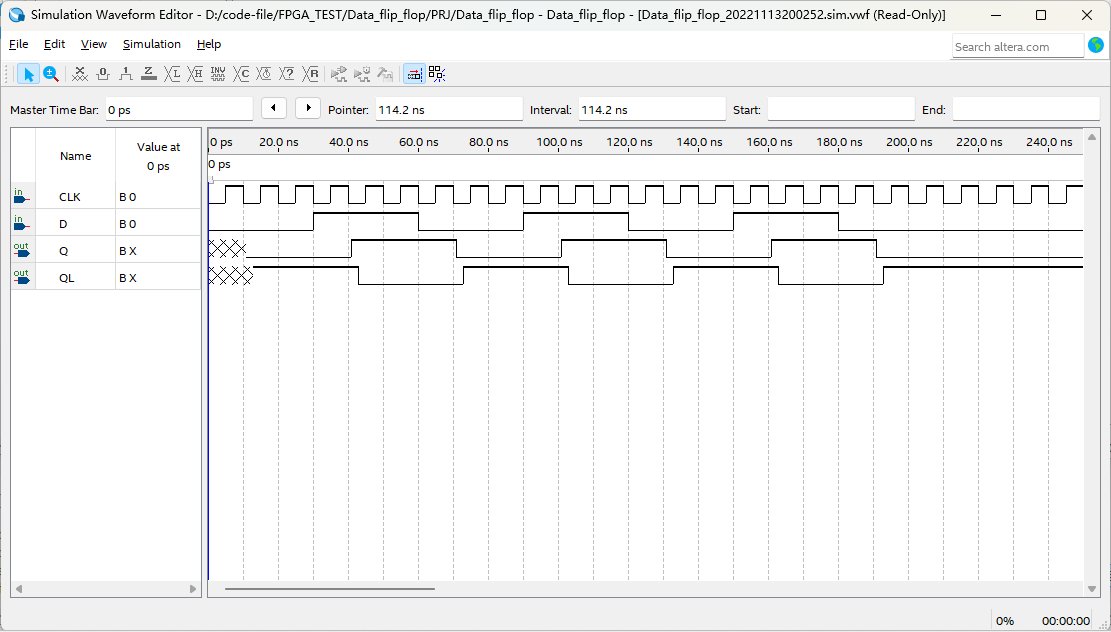

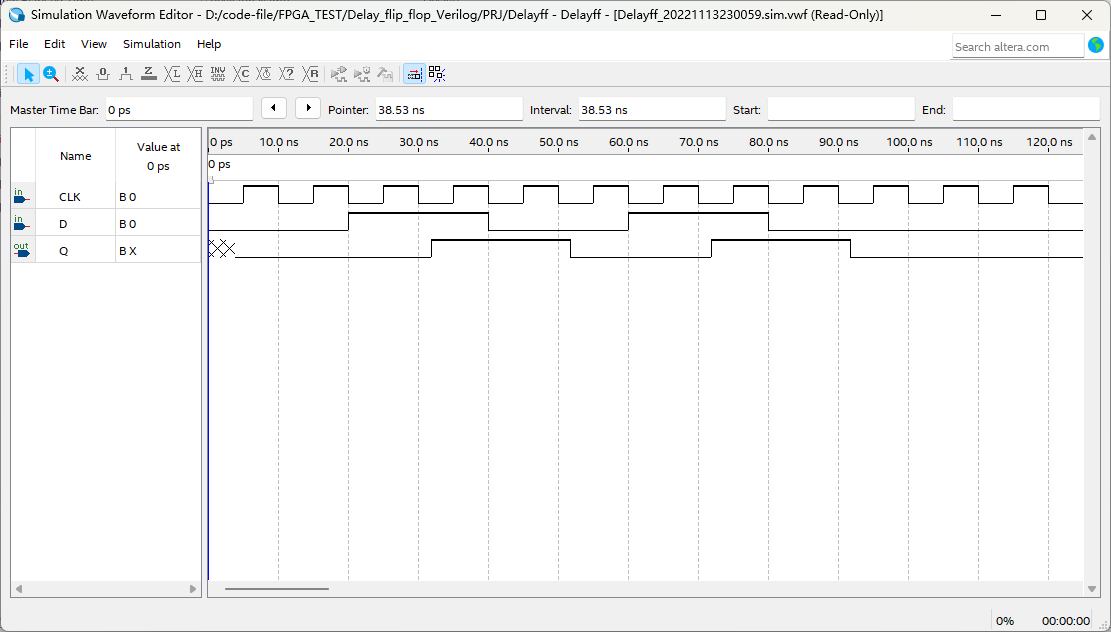

门电路设计 D 触发器仿真结果

时序仿真结果如下:

功能仿真结果如下:

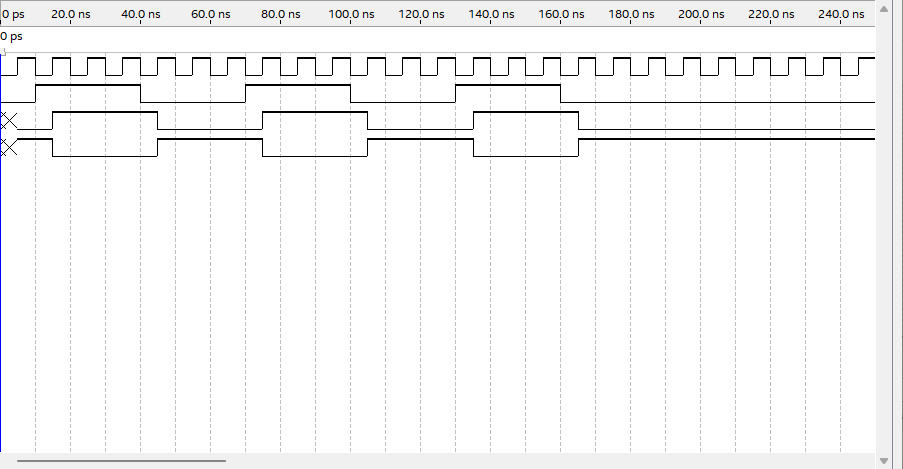

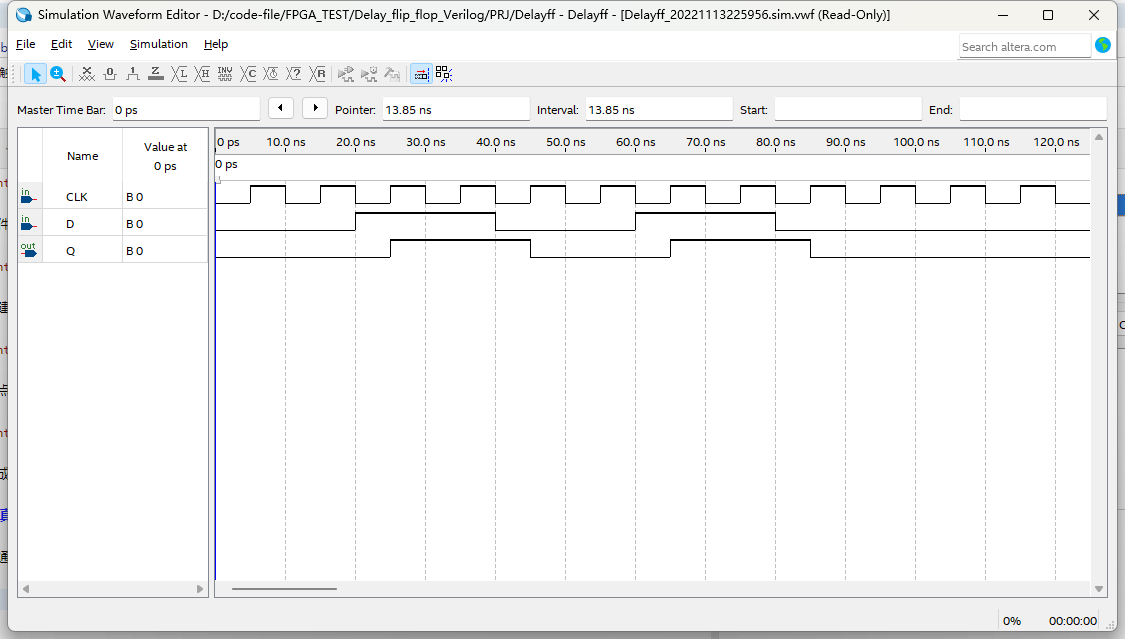

调用 D 触发器仿真结果

时序仿真结果如下:

功能仿真结果如下:

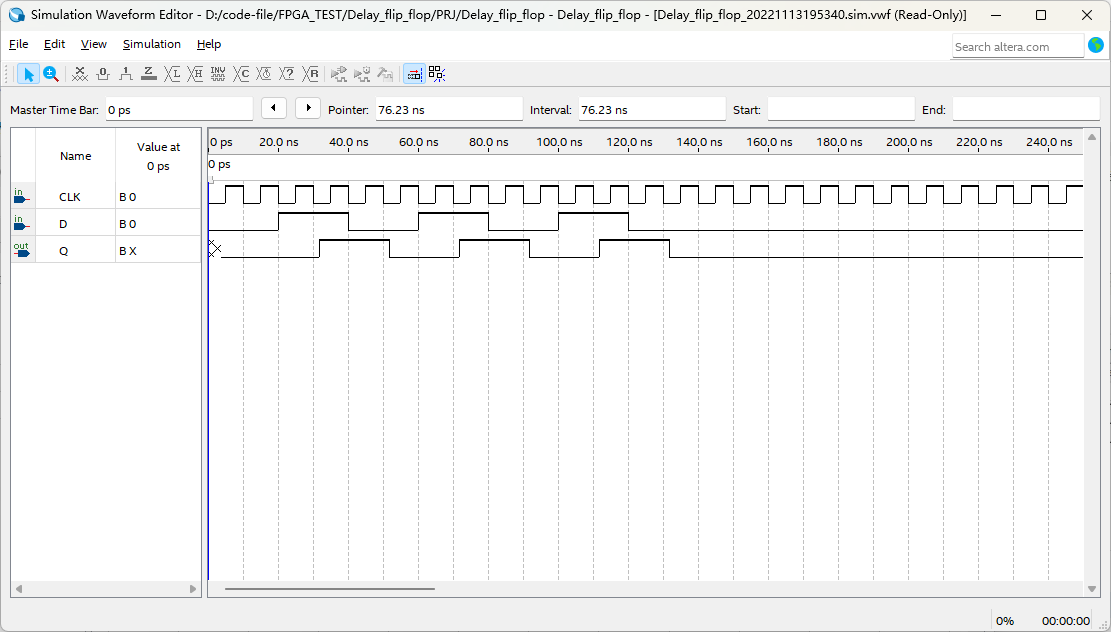

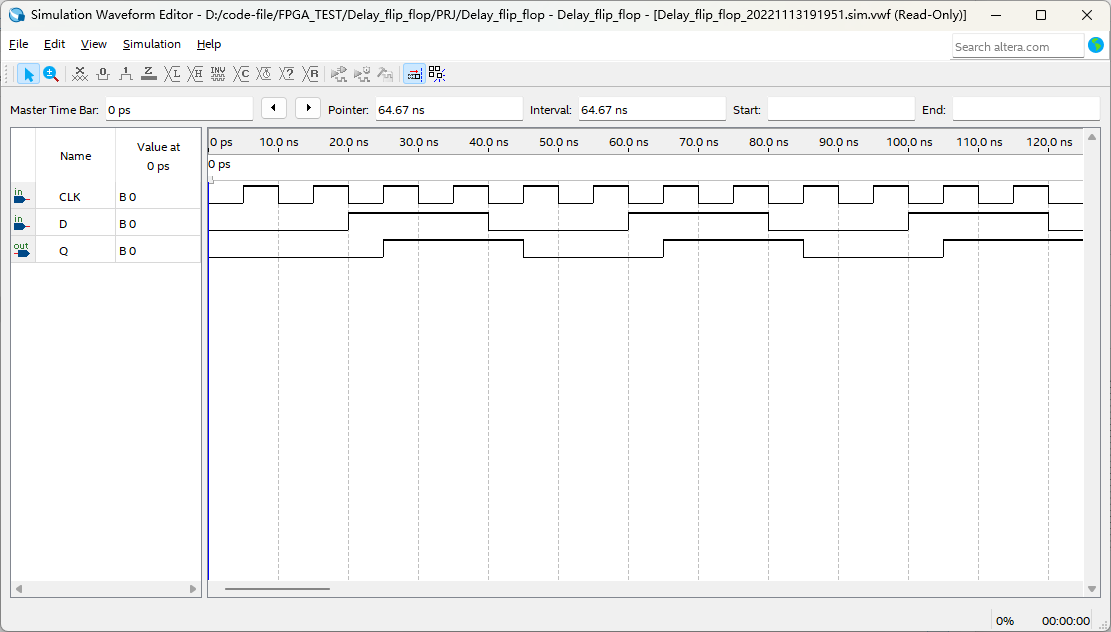

代码设计 D 触发器

时序仿真结果如下:

功能仿真结果如下:

结果分析

时序仿真结果与功能仿真结果相同,均为延迟了半个时钟周期,说明我们设计的 D 触发器没有问题

报错解决方案

报错如下:

解决方法如下:

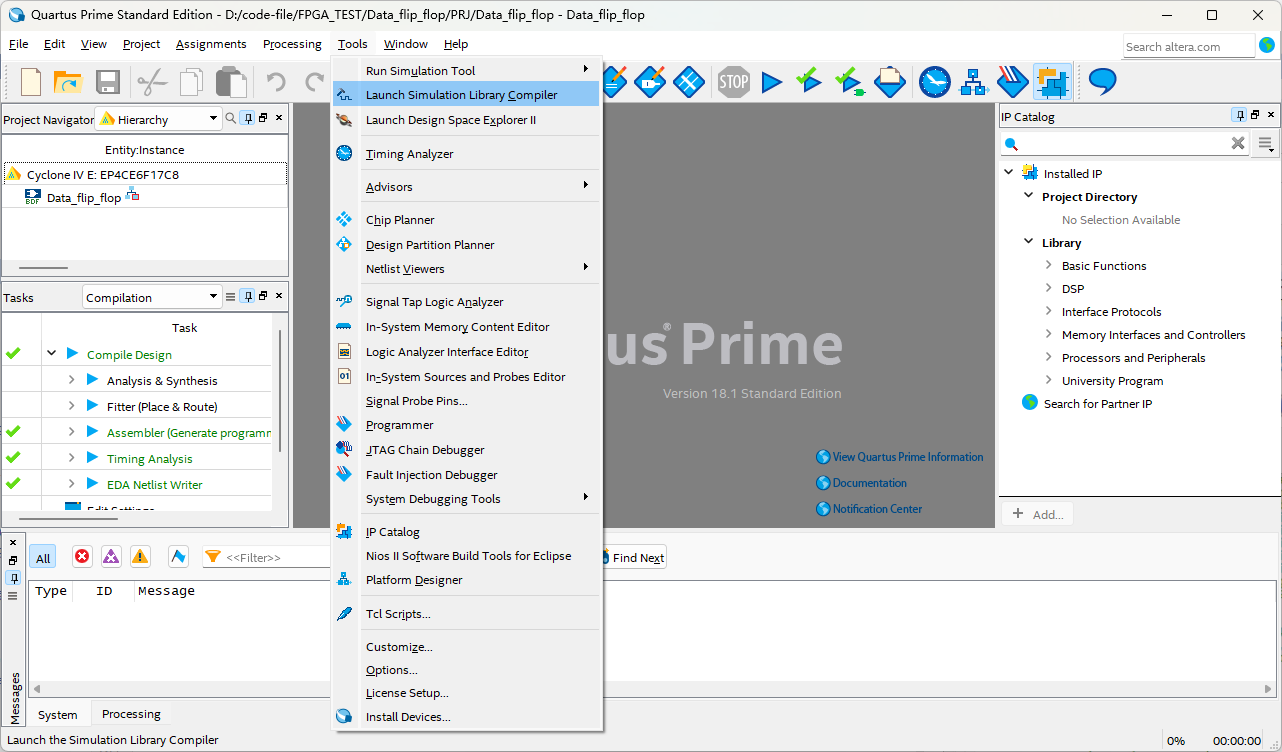

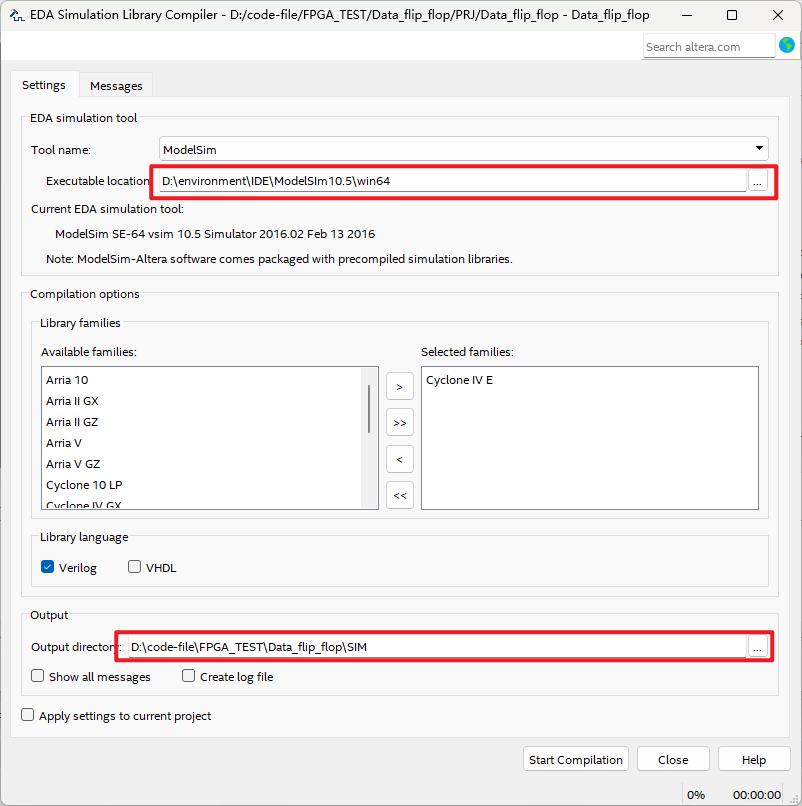

需要手动添加 ModelSim ,过程如下:

22.cnblogs.com/blog/2829072/202211/2829072-20221113154400352-558146278.png)

这里需要选择我们下载安装的 ModelSim 目录下的 Win64 文件夹,然后需要选择我们的目标输出文件夹:

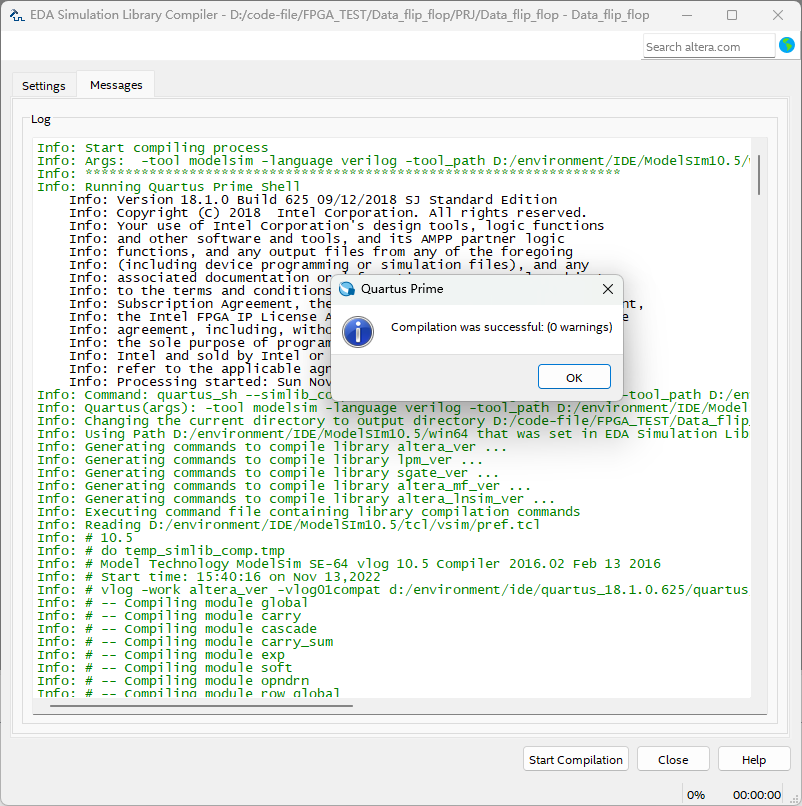

出现如下界面说明 ModelSim 添加成功:

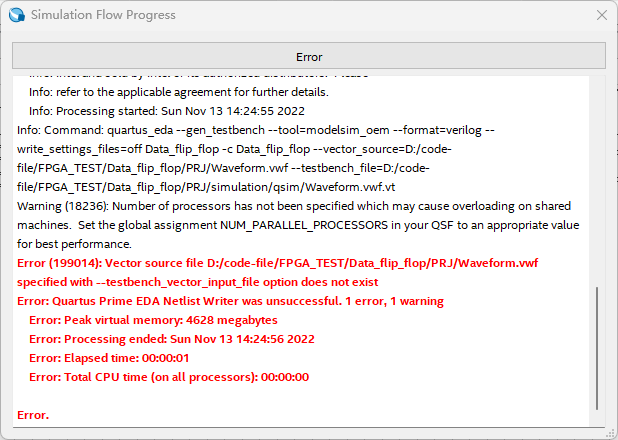

报错如下:

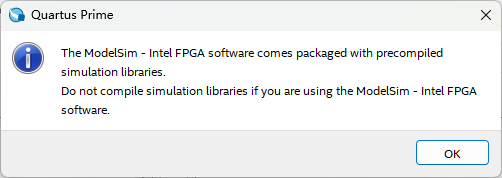

在添加 ModelSim 可能会中出现如下报错:

解决方法如下:

在下载安装 Quartus 时,我们安装的是 ModelSimilar-Altera 而不是通用的 ModelSim ,我们需要安装 ModelSim 再添加即可

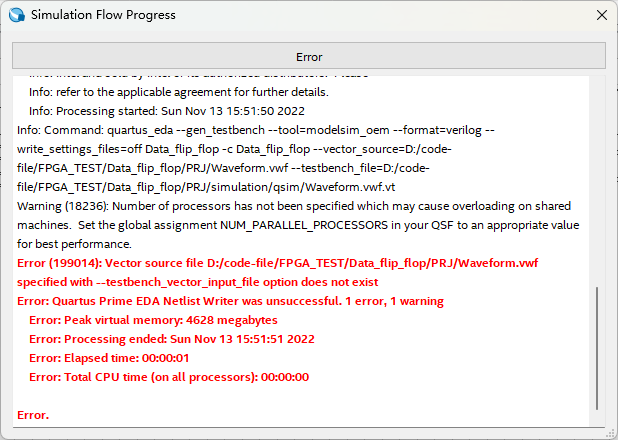

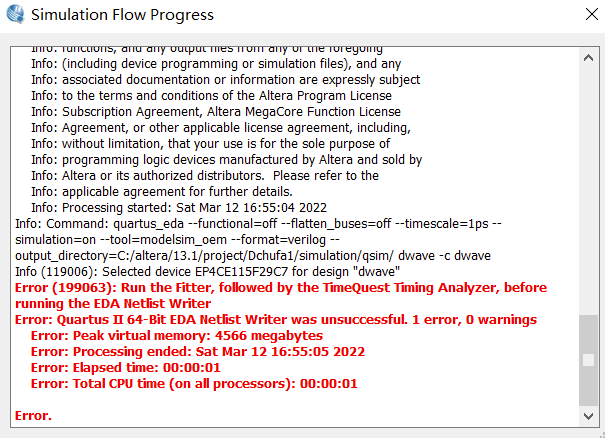

报错如下:

解决方法如下:

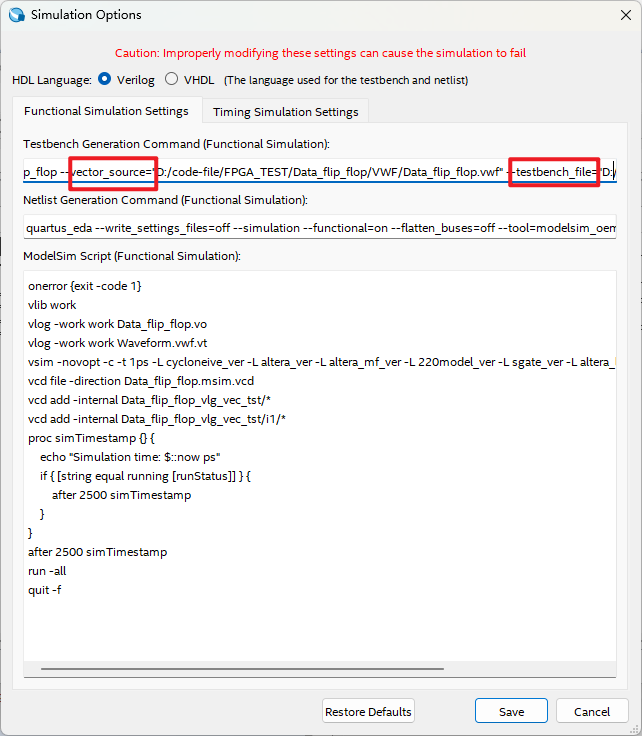

保存 vmf 文件时,保存在默认路径即可。或者在 vmf 文件里 Simulation 的配置中修改 testbench 文件的路径

修改 testbench 路径过程如下:

注意:这里两个的文件名要一致,不然会发生报错

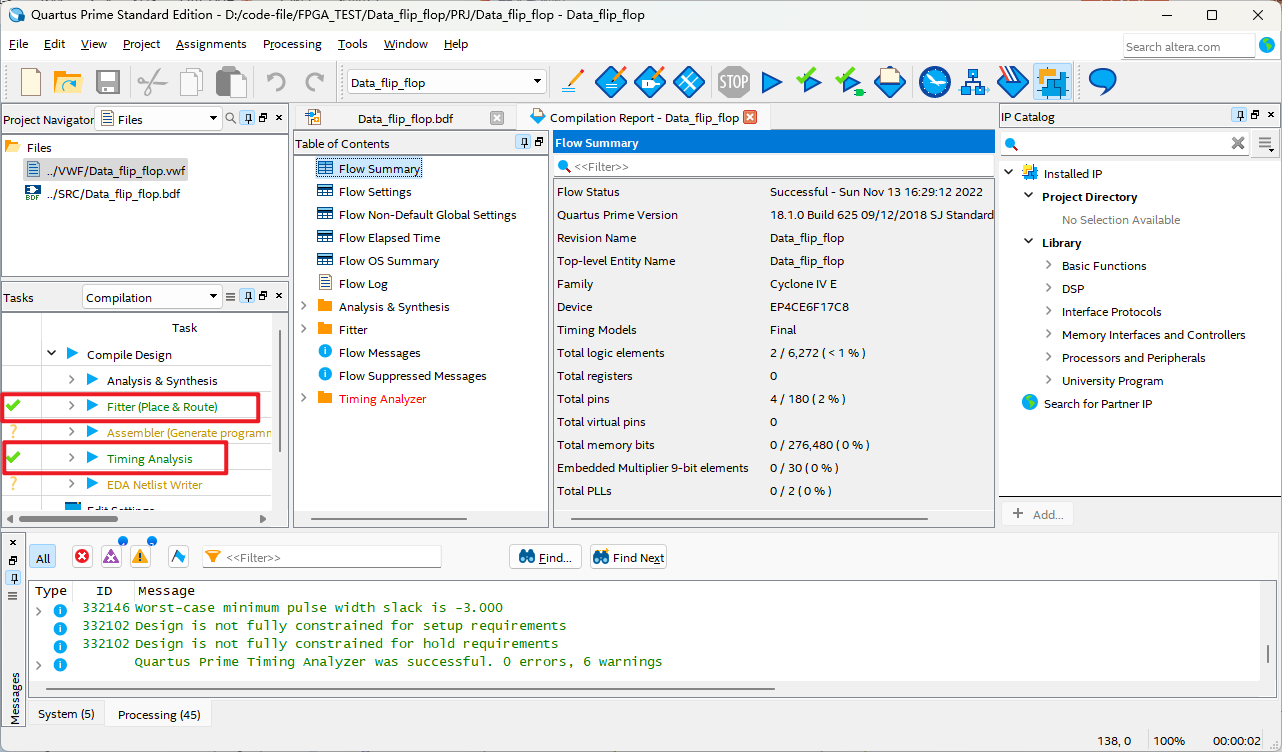

报错如下:

直接进行时序仿真会发生报错:

解决方法如下:

需要进行相关编译:

如果我们一开始就进行全部编译,就不会出现上述报错

浙公网安备 33010602011771号

浙公网安备 33010602011771号