FPGA 入门 —— D 触发器入门

FPGA 入门 —— D 触发器入门

触发器是时序逻辑电路的基本单元,用来存储1位2进制信息,具有记忆和存储功能,其信息由双稳态电路来保存。触发器位脉冲边缘敏感器间,分为上升沿敏感和下降沿敏感。触发器的种类很多,由D触发器,J-K 触发器,T 触发器等。并且根据运用场景的不同,触发器还会有置位,复位,使能和选择等功能

简介

D触发器,Data flip-flop / Delay flip-flop

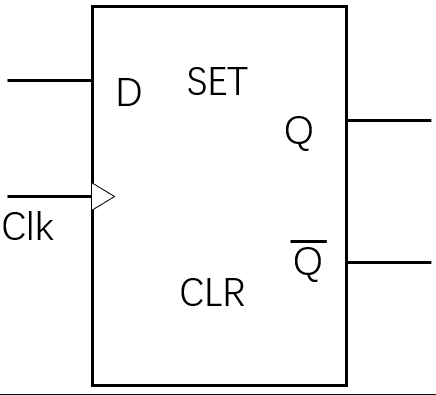

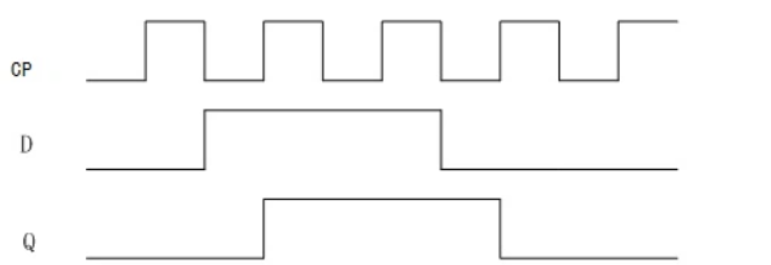

D 触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D 的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端 D 必须有足够的建立时间,保证信号稳定。D 触发器的逻辑符号如图:

电路结构

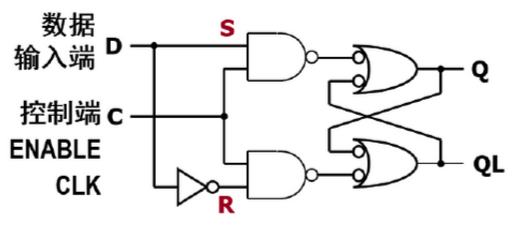

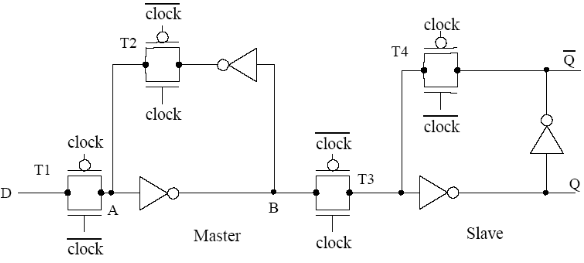

触发器主要有两种电路结构,CMOS 逻辑门如图,和传输门构成的 D 触发器

CMOS 逻辑门构成 D 触发器

传输门构成 D 触发器

两种电路结构实现的 D 触发器功能一模一样,我们主要使用的就是门电路,这里通过逻辑门电路对 D 触发器进行分析。如图所示:在clk 上升沿到来之前,D 输入端无论输入任何值触发器状态不会改变,次态等于现态。当时钟上升沿到来时,与时钟信号连接的非门产生的短暂延迟,使得触发器状态置成 D 输入端的状态

触发器特性

| D | CLK | Q | QN |

|---|---|---|---|

| 0 | \(\uparrow\)时钟上升沿 | 0 | 1 |

| 1 | \(\uparrow\)时钟上升沿 | 1 | 0 |

| X | 0 | Q | QN |

| X | 1 | Q | QN |

-

D:0,CP:0 , 触发器保持不变

CP 为 0,G4 输出为 1,G3 输出为 1

SR 输入均为 1,基本 RS 触发器输出保持不变

-

D:0,CP:1

有上一步知道,G5 输入为 1,而输出为 0,则 G3 输出为 1,S 为 1

D 为 0,G6 输出为 1,G4 输出为 0,则 R 为 0。则基本 RS 触发器输出为 0

-

D:1,CP:0

CP 为 0,G4 输出为 1,G3 输出为 1

SR 输入均为 1,基本 RS 触发器输出保持不变

-

D:1,CP:1

有上一步知道 G3 输出为 0,则 G5 输入为 0 而输出为 1,因为 CP 为 1,则 G3 输出仍然为 0,S 为 0

G3 输出为 0,G4 输入为 0,G4 输出为 1,R 为 1。基本 RS 触发器输出为 1。

所以,若 CP 为 0,G3 和 G4 输入为 0,则基本 RS 触发器的输入均为 1,输出保持不变。不会产生触发动作,并且 CP 为边沿触发,上升沿有效,下降沿无触发动作

CP 为 1 时,G3 输出为 0,则 G4 输入为 0 使输入 CP 为 1 的高电平无效, G4 输出为 1。G3 输出的 0 使 G4 输出一定为 1, 基本 RS 触发器输入不会同时置 0

在数据输入 Date 端,G5 受 G3 控制,也是受 CP 控制,G6 受 G4 控制,也是受 CP 控制。

输出状态波形图如下:

因为 D 触发器的基本单元有 6 个与门构成,与门输入端一旦有 0 则输出为 0,从而不会有内部循环电路出现。不论输入怎样变化,一旦输入端有 0 会使与非门固定,保持稳定输出为 1

浙公网安备 33010602011771号

浙公网安备 33010602011771号