ARM TrustZone白皮书部分阅读

嵌入式系统安全的一些解决方法及缺陷

- 外部硬件安全模块:在主SoC之外包含一个专用的硬件安全模块或可信元件,e.g. 手机的SIM卡。隔离仅限于可以从非易失性存储器运行的相对静态程序

- 内部硬件安全模块:管理加密操作和密钥存储的硬件模块;通用的处理引擎,放在主处理器旁边,它使用自定义硬件逻辑来防止对敏感资源的未经授权的访问。隔离仅限于加密密钥材料

- 软件虚拟化:高度可信的管理层(称为

hypervisor)以通用处理器的特权模式运行。hypervisor使用内存管理单元(MMU)分离运行在其上的多个独立软件平台,将每个平台放在由hypervisor软件控制的虚拟机中。隔离仅限于实现hypervisor的处理器

TrustZone硬件安全方案

- 解决问题:上述的其他安全方案只能保护系统中受限制部分的某些资产。

- 设计目标:一种在

整个系统设计中扩展安全基础设施的硬件架构。 - 架构特点:并未对某个专用硬件模块中的资产进行保护,而是使系统的任何部分都变得安全,从而实现了包括功能单元和调试基础框架在内的端到端安全解决方案。

TrustZone硬件架构

- 安全目标:构建一个可编程环境,使绝大多数资产的机密性和完整性都能免受特定攻击。

- 实现原理:

- 划分SoC的所有硬件和软件资源,使其存在于两个世界中的一个:安全子系统的安全世界,以及其他一切的正常世界。

AMBA3 AXI™ 总线提供的硬件逻辑确保正常世界组件不能访问任何安全世界的资源,从而在两者之间建立一个强大的安全边界。敏感资源放在安全世界,鲁棒性软件在安全世界处理器核上运行。 - 在一些ARM处理器核心中实现扩展。这些附加功能使单个物理处理器核心能够以时间切片的方式安全高效地执行来自正常世界和安全世界的代码。

- 具有安全意识的调试基础框架,它可以控制对安全世界调试的访问,而不影响正常世界的调试可见性。

- 划分SoC的所有硬件和软件资源,使其存在于两个世界中的一个:安全子系统的安全世界,以及其他一切的正常世界。

TrustZone系统架构

- AMBA3 AXI 系统总线:为主系统总线上的每个读写通道添加额外的控制信号(非安全位/NS位)。总线主设备设置这些信号

- AMBA3 APB外围设备总线:TrustZone体系结构最有用的特性之一是能够保护外围设备。

- 内存别名使用:主设备对从设备进行安全访问,非安全的slave接受安全事务,但slave将这些访问视为不安全的。在这种设计下,硬件必须支持

地址空间别名:相同的内存位置在地址映射中显示为两个不同的位置,一个安全,一个不安全。需要注意一致性问题

TrustZone处理器结构

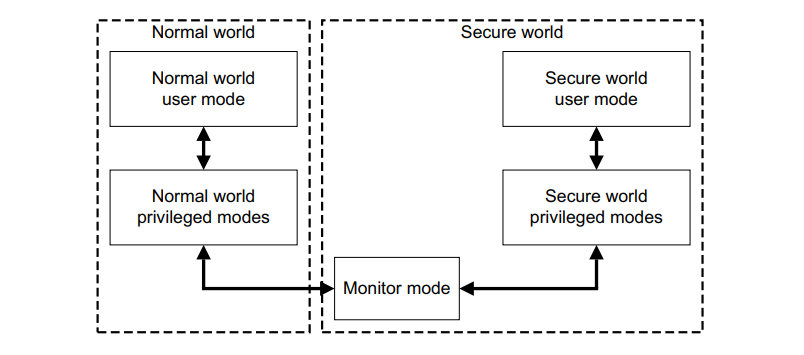

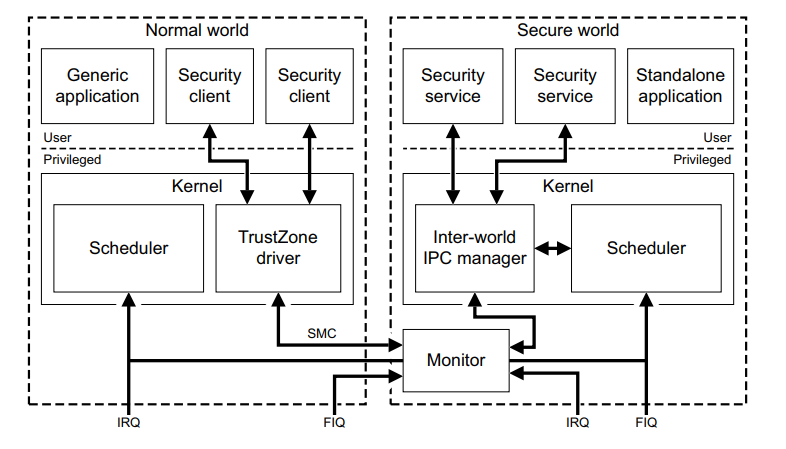

-

每个处理器核心都提供了两个虚拟核心,一个安全一个不安全,还有一个在他们之间进行上下文切换的 monitor mode:

![image-20221101141410351]()

发送到主系统总线上的

NS位的值是由执行指令或数据访问的虚拟内核的身份标识间接得出的。非安全的虚拟处理器只能访问非安全系统资源,但安全虚拟处理器可以看到所有资源。 -

world切换:这两个虚拟处理器以

时间切片的方式执行,在更改当前运行的虚拟处理器时,上下文将通过名为monitor mode的新核心模式进行切换。物理处理器进入monitor mode时可以通过执行特定指令的软件、SMC指令、硬件异常机制的子集进行触发。如果处理器不在监控模式下,它正在执行的世界由系统控制协处理器CP15中安全配置寄存器(SCR)中的NS位指示;如果处于监控模式下,无论SCR NS位的值是多少,处理器总是在安全的世界中执行;但是如果SCR NS位设置为1,则对banked CP15寄存器的操作将访问正常世界的副本。 -

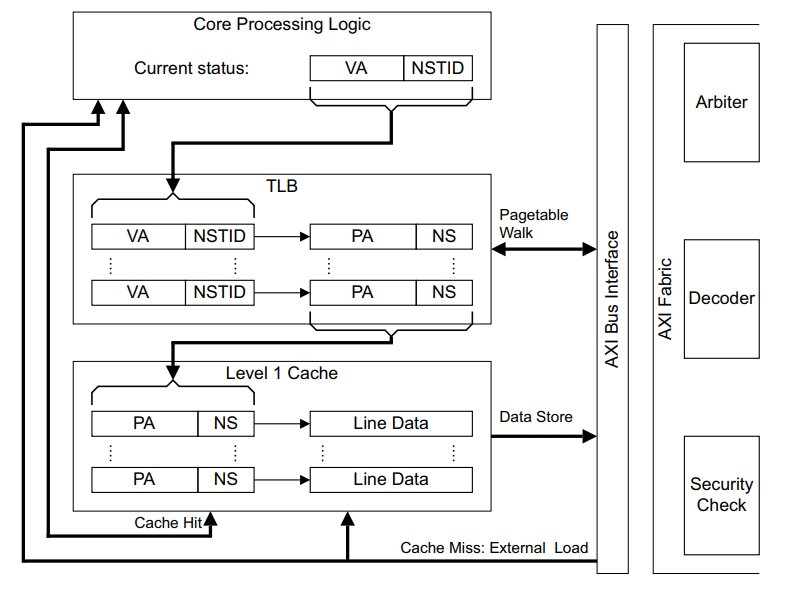

一级保护内存系统:

- MMU:TrsutZone中硬件提供

两个虚拟MMU,每个虚拟处理器一个。每个世界都有一组本地转换表,使它们能够独立地控制虚拟地址到物理地址的映射。为在两个世界之间实现高效的上下文切换,arm处理器会标记TLB中的条目,TLB缓存了地址转换表的遍历结果,并使用执行遍历的世界的标识,这允许非安全和安全条目在TLB中共存,从而加快切换,因为无需刷新TLB条目。 - cache:目标是实现支持缓存中两种安全状态的数据,这样可以消除切换世界的时候需要刷新缓存的需要。解决方法是处理器缓存扩展了

一个额外的标志位,该位录访问内存的事务的安全状态。

![image-20221101144637436]()

- 世界共享内存:允许安全世界直接访问非安全缓存。提供性能

- MMU:TrsutZone中硬件提供

-

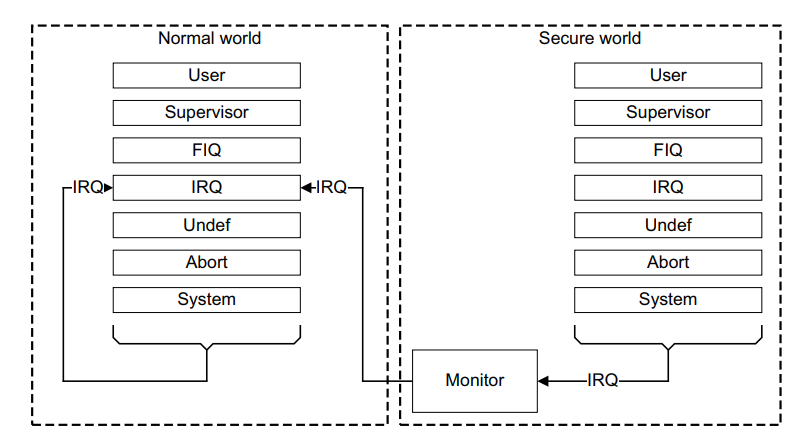

安全中断:直接向monitor捕获IRQ和FIQ的能力(不需要任何一个世界的代码干预)可以为安全中断源创建一个灵活的中断模型。ARM推荐的模型是使用IRQ作为非安全世界的中断源,FIQ作为安全世界的中断源。CPSR是存放的程序状态寄存器

![image-20221101150353962]()

启用TrustZone的处理器实现了三组异常向量表。其中一个表用于正常世界,一个用于安全世界,另一个用于监视模式。

-

安全处理器:协处理器CP15中的敏感的配置选项,或

全局应用于核心的配置选项,只能由安全世界软件编写,非安全世界可以读取。 -

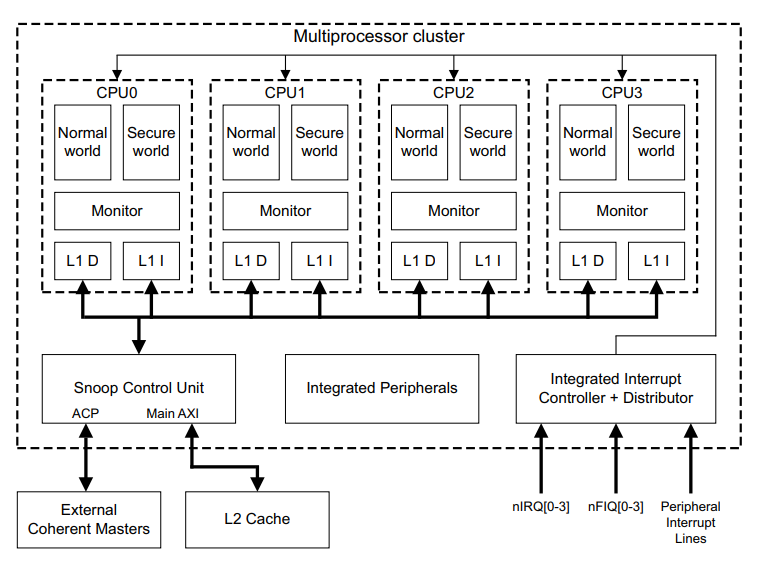

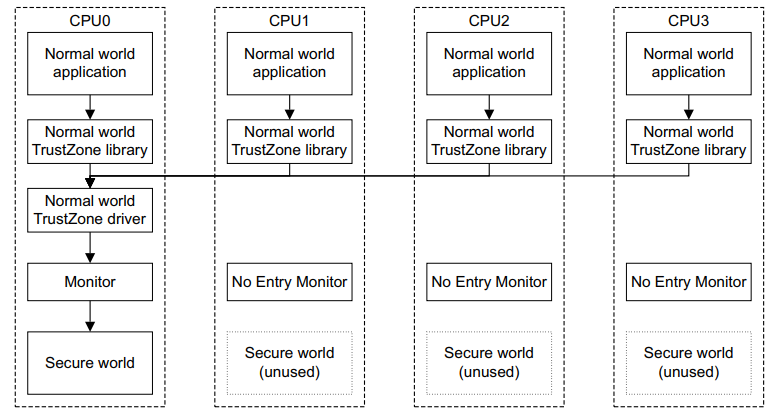

多处理器系统:集群中的处理器可以配置为以对称多处理(SMP)模式或非对称多处理(AMP)模式执行。当处理器以SMP模式执行时,集群的Snoop控制单(SCU)将透明地将跨SMP处理器共享的数据保存在L1数据缓存中。当处理器以AMP模式执行时,如果需要,执行软件必须手动保持内存一致性。多处理器集群中的每个处理器都有一个正常世界和一个安全世界。每个虚拟处理器都可以独立控制它们的MMU配置。

![image-20221101153158602]()

TrustZone调试架构

-

处理器调试:ARM处理器包含一个调试控制信号,全局启用或禁用对处理器的调试器访问。TrustZone调试扩展将调试访问控制分成四种独立可配置视图。

-

系统调试:ARM系统调试解决方案是ARM Coresight™片上调试和跟踪技术。它为整个SOC提供了调试和跟踪解决方案,支持对多个处理器和其他系统组件进行调试。可以从设备外工具和设备内组件访问Coresight调试基础结构。

TrustZone软件架构

-

软件架构:

- 安全操作系统:可以模拟多个独立的安全世界应用程序的并发执行,运行时下载新的安全应用程序,以及完全独立于正常世界环境的安全世界任务。使用MMU讲安全世界内存划分为多个用户空间沙盒,只要安全世界内核软件正确实现,多个安全任务可以不需要信任对方而同时运行。这种设计可以增强安全任务之间的逻辑隔离。

![image-20221101160534112]()

- 同步库:安全世界中的简单代码库可以解决很多应用的任务,这个代码库完全由

非安全世界操作系统的软件调用来进行调度和管理。 - 中间方法:在这两个极端之间有一系列的选择。例如,一个安全世界的多任务操作系统可以被设计成没有专门的中断源,因此可以由普通世界提供一个虚拟中断。

-

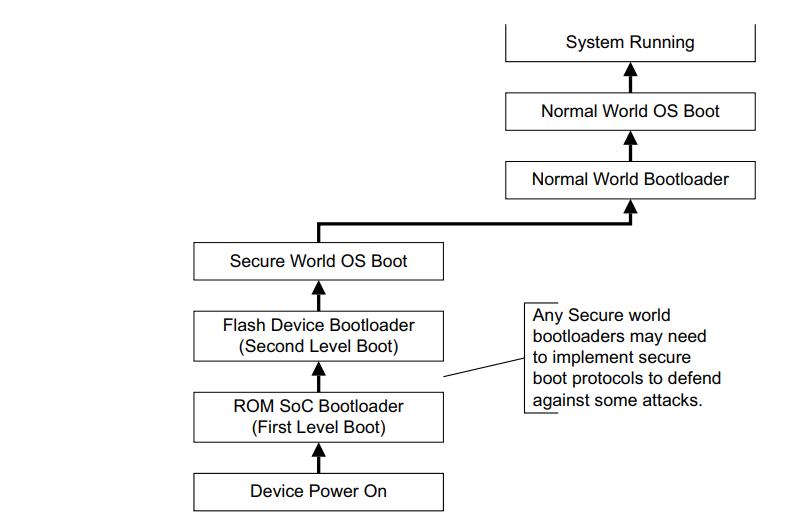

安全启动系统:所有

安全世界软件和潜在的正常世界软件生成一个信任链,该信任链是从不易被篡改的信任根建立的。- 启动流程:开机时启用TrustZone的处理器在安全环境中启动。这使得任何敏感的安全检查都能在普通软件有机会修改系统的任何方面之前运行。开机流程:执行基于ROM的引导加载程序 -> 闪存中的设备引导加载程序 -> 安全世界操作系统初始化 ->切换到非安全世界 -> 正常世界引导加载程序 -> 启动正常的操作系统 -> 系统运行。

![image-20221101161908782]()

- 安全方案:安全启动方案将

加密检查添加到安全世界启动进程的每个阶段。此过程旨在维护执行的所有安全世界软件映像的完整性,防止任何未经授权或恶意修改的软件运行。- 密码签名协议:基于公钥签名算法的协议。受信任的供应商使用他们的私钥(PrK)生成要部署的代码的签名,并将其与软件二进制文件一起推送到设备上。设备包含供应商的公钥(PuK),该公钥可用于验证二进制文件是否未被修改,以及该二进制文件是否由相关的受信任供应商提供。

- 信任链:从一个隐式可信组件开始,在执行之前,可以对每个其他组件进行身份验证。信任根位于ROM中,不容易被修改或替换。

- 片内/片外安全世界:最简单的防御shack攻击的方法是将任何安全世界资源的执行放在SoC片内内存位置。如果代码和数据从未暴露在SoC封装之外,则很难窥探或修改数据值。

-

监控模式软件:管理安全和非安全处理器状态之间的切换,类似于上下文切换。正常世界进入监控模式需通过以下异常实现:

中断、外部中止或通过SMC指令的显式调用;从安全世界进入监控模式除了通过正常世界可用的异常机制外,还可以通过直接写入CPSR来实现。- 上下文切换:监视器保存的任何安全状态都应该保存在安全内存的某个区域中,这样正常世界就不会对其进行篡改。可以通过过

SMC指令、惰性上下文切换(仅在必要时保存协处理器的上下文,而不是在每次操作系统上下文切换或TrustZone世界切换时都保存)来实现世界切换。

- 上下文切换:监视器保存的任何安全状态都应该保存在安全内存的某个区域中,这样正常世界就不会对其进行篡改。可以通过过

-

安全软件和多处理器系统:安全世界软件实现可以选择实现一个单处理器安全世界(不具备多处理能力)。

-

将安全世界的执行固定在一个特定的处理器上:在这种设计中,与安全世界通信的普通世界驱动程序通常需要使用处理器间通信将使用安全世界的请求路由到正确的处理器。此外,安全世界不使用的处理器上的监控软件必须防止普通世界造成恶意的世界切换。

![image-20221101172157955]()

-

让安全世界在系统的多个处理器上迁移:但通过限制它使其在任何单一时间只在一个处理器上执行。

-

TrustZone API

- 定义了一个软件接口,在富操作环境中运行的客户端应用可以使用该接口与安全环境交互。该API主要是一个通信API,使客户端能够向安全服务发送命令请求,并使客户端能够有效地与所连接的服务交换数据。

浙公网安备 33010602011771号

浙公网安备 33010602011771号