读书笔记 计算机系统--系统架构与操作系统的高度集成 第三章处理器实现

处理器设计所围绕的两个问题:

指令集设计(软件)

机器结构设计(硬件)

第三章为处理器设计。

处理器设计所受影响:

电子部件(ALU,总线,寄存器)的组成如何满足性能和价位。

散热,主板的物理几何学。

多处理器考虑电路板,背板,连接器,底盘设计。

本章讲单处理器的数据通路和控制。

处理器如何设计:

硬件基础概念。--------------------------------一

数据通路设计。--------------------------------二

控制单元。--------------------------------------三

一:硬件基础概念

电路:

组合电路,没有记忆,由基本的逻辑门组成。

时序逻辑,在组合电路的基础上添加触发器的记忆元件。

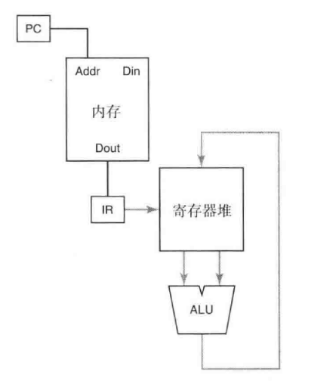

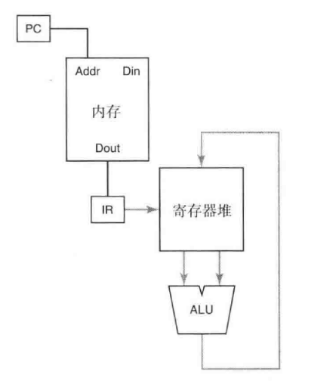

数据通路的硬件资源:

内存,保存指令和操作数。

算术/逻辑单元(ALU),执行算数/逻辑指令。

寄存器堆,绝大部分指令使用寄存器堆。

双端口寄存器堆(DPRF),允许同时读取两个寄存器

程序计数器(PC),指向当前指令以及分支跳转指令。

指令寄存器(IR),用来存储从内存中取出的指令。

边沿触发逻辑:

电平逻辑,高电平触发。

边沿触发逻辑,只发生在时钟的上升沿(正)和下降沿(负)。

连接数据通路的元件:

1、PC指明指令的地址

2、指令从内从中取出到IR

3、IR中指令从寄存器堆中读对应的寄存器,并将结果协会到寄存器堆对应的寄存器。

假设为正边沿触发,在一个时钟周期内可以将信息从一个存储元件传送到另一个存储元件,

1、2步骤可以在一个时钟周期内完成。到下一个时钟周期IR中指令才可用。

上述过程中,决定时钟周期的:

PC等待稳定到可以读取的时间

PC到内存的线延迟

内存访问时间

内存到IR的线延迟

第二个时钟上升沿前,IR等待达到稳定的时间,也叫建立时间

第二个时钟上升沿后,IR保持输出,也叫保持时间

延迟最大的那个时钟周期的用时,就是时钟宽度。

线延迟占主要地位。

基于总线的设计:

单总线:

元件和总线见有一个驱动器(三态缓冲器),一个时钟周期只有一个开。

双总线设计:

依旧驱动器,总线分为地址总线和数据总线。

在有地址总线和数据总线的数据通路中加入控制单元。

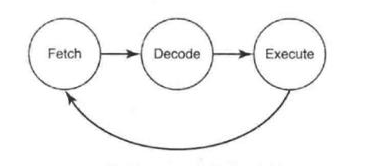

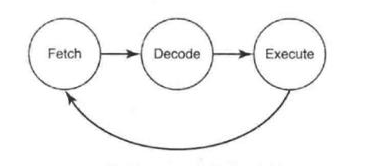

有限状态机FSM:

将数据通路通过状态切换来完成指令。

Fetch:这个状态将指令从内存中取出。

Decode:对读出的指令进行解释,确定操作。

Excute:执行指令。

二:数据通路设计

指令系统架构ISA与数据通路宽度:

总线窄,牺牲性能,价格更低。

总线宽,性能强,价格高。

时钟脉冲宽度:

类似之前时钟周期宽度的计算,就是计算最坏情况的延迟。

三:控制单元

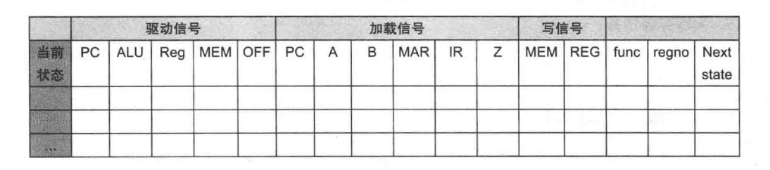

控制单元所有实现都是对于处理控制单元的FSM的硬件实现的。

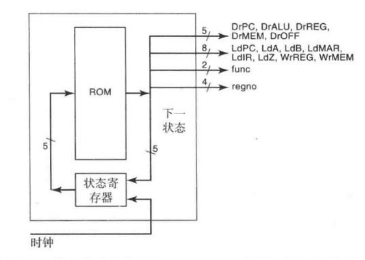

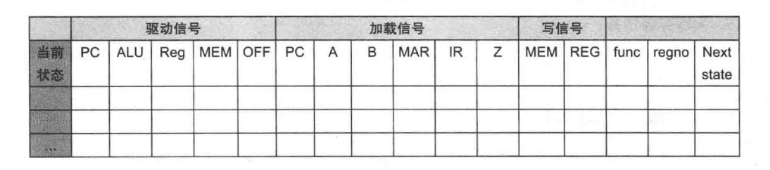

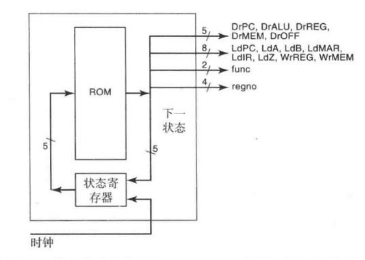

ROM加状态寄存器:

状态寄存器的引入:

FSM三个状态,取指,译码,执行都有许多为状态来表示宏观的细节

ifetch1 0000

ifetch2 0001

ifetch3 0010

使用一个表,表中每一项都包含该状态下所需的全部控制信号。

每一个控制信号用1位表示。

硬件实现:

用只读存储器ROM冻结表中的内容。

每过一个时钟周期状态机寄存器就到ROM中输出对应的控制信号,计入下一个状态。

ROM发出的所有加载信号充当掩码,决定控制的存储元件是否在这个时钟周期中被驱动。

FETCH宏状态:

程序计数器PC发送给内存。

读出内存的内容。

将内存内容发送到IR中。

递增PC。

` DECODE宏状态

识别IR中的指令,找到微程序

对于不同的操作码的类型,有多路分支到不同状态。

处理器设计所围绕的两个问题:

指令集设计(软件)

机器结构设计(硬件)

第三章为处理器设计。

处理器设计所受影响:

电子部件(ALU,总线,寄存器)的组成如何满足性能和价位。

散热,主板的物理几何学。

多处理器考虑电路板,背板,连接器,底盘设计。

本章讲单处理器的数据通路和控制。

处理器如何设计:

硬件基础概念。--------------------------------一

数据通路设计。--------------------------------二

控制单元。--------------------------------------三

一:硬件基础概念

电路:

组合电路,没有记忆,由基本的逻辑门组成。

时序逻辑,在组合电路的基础上添加触发器的记忆元件。

数据通路的硬件资源:

内存,保存指令和操作数。

算术/逻辑单元(ALU),执行算数/逻辑指令。

寄存器堆,绝大部分指令使用寄存器堆。

双端口寄存器堆(DPRF),允许同时读取两个寄存器

程序计数器(PC),指向当前指令以及分支跳转指令。

指令寄存器(IR),用来存储从内存中取出的指令。

边沿触发逻辑:

电平逻辑,高电平触发。

边沿触发逻辑,只发生在时钟的上升沿(正)和下降沿(负)。

连接数据通路的元件:

1、PC指明指令的地址

2、指令从内从中取出到IR

3、IR中指令从寄存器堆中读对应的寄存器,并将结果协会到寄存器堆对应的寄存器。

假设为正边沿触发,在一个时钟周期内可以将信息从一个存储元件传送到另一个存储元件,

1、2步骤可以在一个时钟周期内完成。到下一个时钟周期IR中指令才可用。

上述过程中,决定时钟周期的:

PC等待稳定到可以读取的时间

PC到内存的线延迟

内存访问时间

内存到IR的线延迟

第二个时钟上升沿前,IR等待达到稳定的时间,也叫建立时间

第二个时钟上升沿后,IR保持输出,也叫保持时间

延迟最大的那个时钟周期的用时,就是时钟宽度。

线延迟占主要地位。

基于总线的设计:

单总线:

元件和总线见有一个驱动器(三态缓冲器),一个时钟周期只有一个开。

双总线设计:

依旧驱动器,总线分为地址总线和数据总线。

在有地址总线和数据总线的数据通路中加入控制单元。

有限状态机FSM:

将数据通路通过状态切换来完成指令。

Fetch:这个状态将指令从内存中取出。

Decode:对读出的指令进行解释,确定操作。

Excute:执行指令。

二:数据通路设计

指令系统架构ISA与数据通路宽度:

总线窄,牺牲性能,价格更低。

总线宽,性能强,价格高。

时钟脉冲宽度:

类似之前时钟周期宽度的计算,就是计算最坏情况的延迟。

三:控制单元

控制单元所有实现都是对于处理控制单元的FSM的硬件实现的。

ROM加状态寄存器:

状态寄存器的引入:

FSM三个状态,取指,译码,执行都有许多为状态来表示宏观的细节

ifetch1 0000

ifetch2 0001

ifetch3 0010

使用一个表,表中每一项都包含该状态下所需的全部控制信号。

每一个控制信号用1位表示。

硬件实现:

用只读存储器ROM冻结表中的内容。

每过一个时钟周期状态机寄存器就到ROM中输出对应的控制信号,计入下一个状态。

ROM发出的所有加载信号充当掩码,决定控制的存储元件是否在这个时钟周期中被驱动。

FETCH宏状态:

程序计数器PC发送给内存。

读出内存的内容。

将内存内容发送到IR中。

递增PC。

` DECODE宏状态:

识别IR中的指令,找到微程序

对于不同的操作码的类型,有多路分支到不同状态。

EXCUTE宏状态:

执行指令

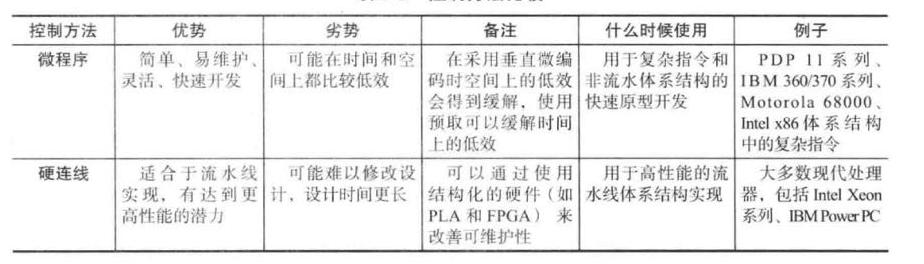

微程序设计易于维护,但是时间上需要向ROM提供一个地址,然后经过访问延迟才可用,

空间上,表中用的是水平微码风格,位大部分是0,但是可以通过一种垂直微码技术来克服。

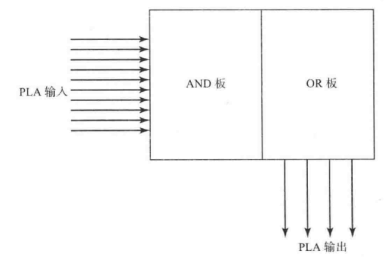

硬连线控制:

使用AND/OR门,或者NAND/NOR这样的门,可以生成所有控制信号

这种设计在时间和空间上都十分有效(不用查找ROM)

可编程逻辑阵列PLA和现场可编程门阵列FPGA的硬件实现。

非常灵活,现代VLSI已经离不开了

控制方法的比较:

浙公网安备 33010602011771号

浙公网安备 33010602011771号