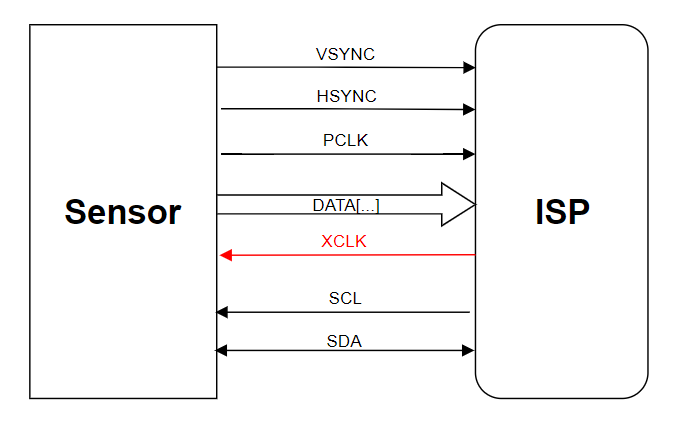

Camera DVP接口

PCLK:pixel clock ,像素时钟,每个时钟对应一个像素数据;

HSYNC:horizonal synchronization,行同步信号

VSYNC:vertical synchronization,帧同步信号;

DATA:像素数据,视频数据,具体位宽要看ISP是否支持;

XCLK:或者MCLK,ISP芯片输出给驱动sensor的时钟;

DVP的时序图FV为帧同步信号,LV为行同步信号(LV为高时,传输有效的像素数据)。

ISP与sensor之间通过IIC协议读写sensor的寄存器,配置sensor,在实际应用的时候,ISP首先会给sensor一个XCLK,sensor内部的PLL会对计算,产生PCLK,PCLK由幅面(F_W、F_H)、帧率(FPS)决定,并存在如下关系:

-

PCLK = F_W * F_H * FPS

野火技术文档:

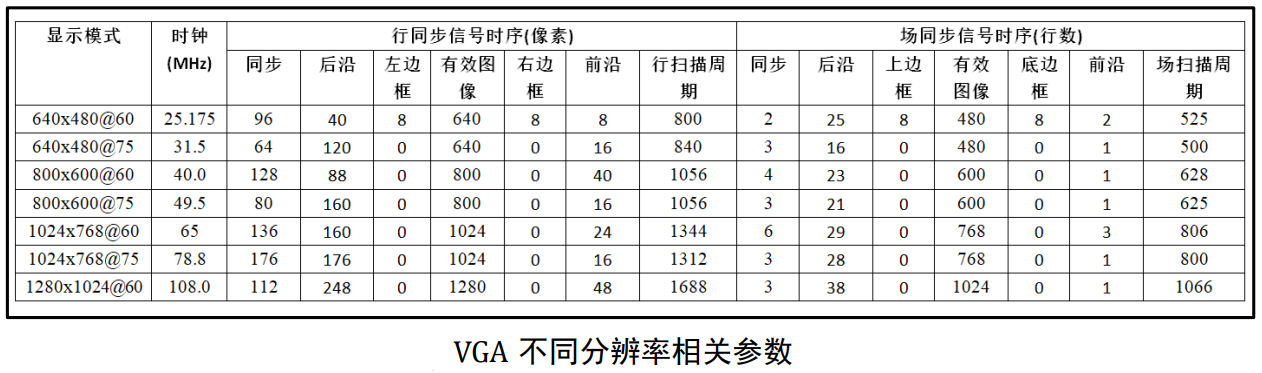

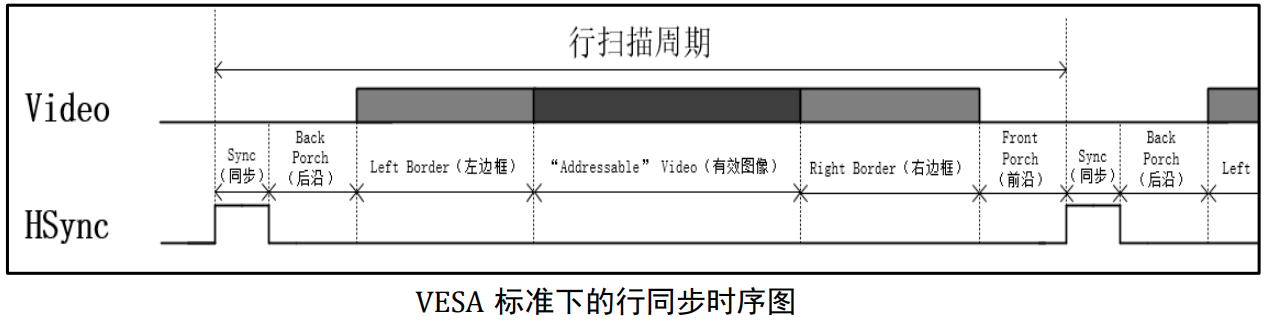

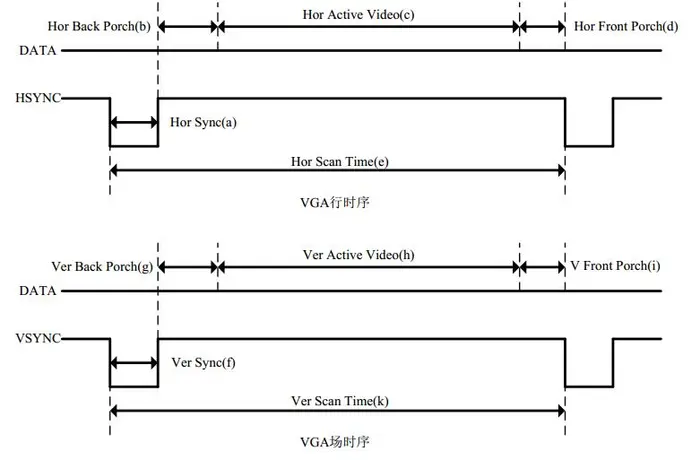

行同步时序

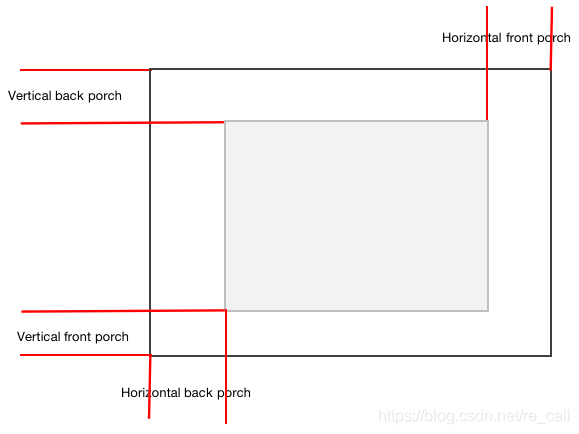

图中 Video 代表传输的图像信息,HSync 表示行同步信号。HSync 自上升沿起到下一个上升沿止为一个完整周期,我们称之为行扫描周期。一个完整的行扫描周期,包含 6 部分:Sync(同步)、Back Porch(后沿)、Left Border(左边框)、“Addressable” Video(有效图像)、Right Border(右边框)、FrontPorch(前沿),这 6 部分的基本单位是 pixel(像素),即一个像素时钟周期。

在一个完整的行扫描周期中,Video 图像信息在 HSync 行同步信号的同步下完成一行图像的扫描显示,Video 图像信息只有在“Addressable” Video(有效图像)阶段,图像信息有效,其他阶段图像信息无效。HSync 行同步信号在 Sync(同步)阶段,维持高电平,其他阶段均保持低电平,在下一个行扫描周期的 Sync(同步)阶段,HSync 行扫描信号会再次拉高,其他阶段拉低,周而复始。

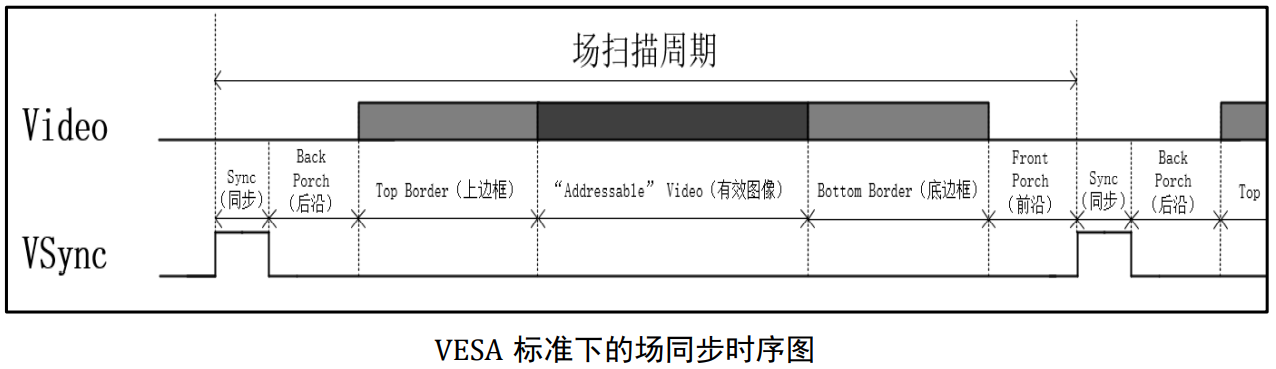

场同步时序

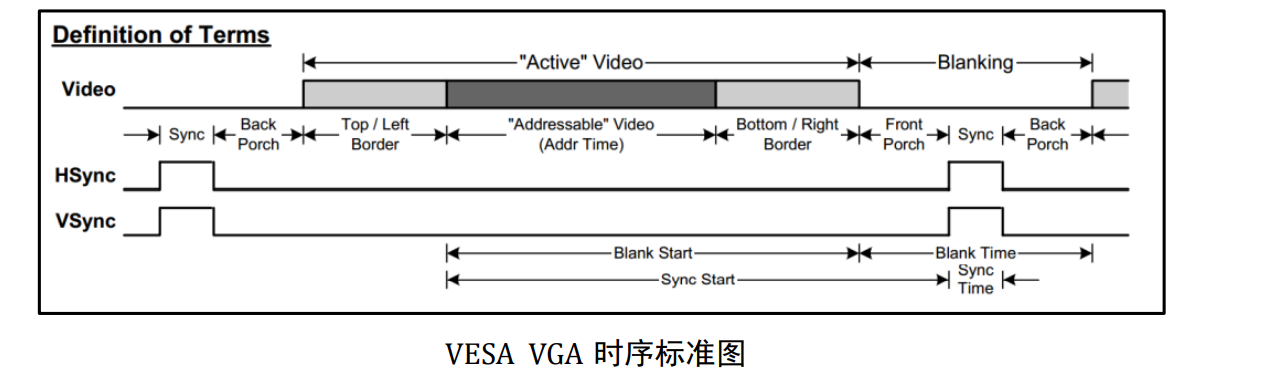

如图所示,Video 代表传输的图像信息,VSync 表示场同步信号,VSync 自上升沿起到下一个上升沿止为一个完整周期,我们称之为场扫描周期。一个完整的场扫描周期,也包含 6 部分:Sync(同步)、Back Porch(后沿)、TopBorder(上边框)、“Addressable” Video(有效图像)、Bottom Border(底边框)、FrontPorch(前沿),与行同步信号不同的是,这 6 部分的基本单位是 line(行),即一个完整的行扫描周期。在一个完整的场扫描周期中,Video 图像信息在 HSync(行同步信号)和 VSync(场同步信号)的共同作用下完成一帧图像的显示,Video 图像信息只有在“Addressable” Video(有效图像)阶段,图像信息有效,其他阶段图像信息无效。

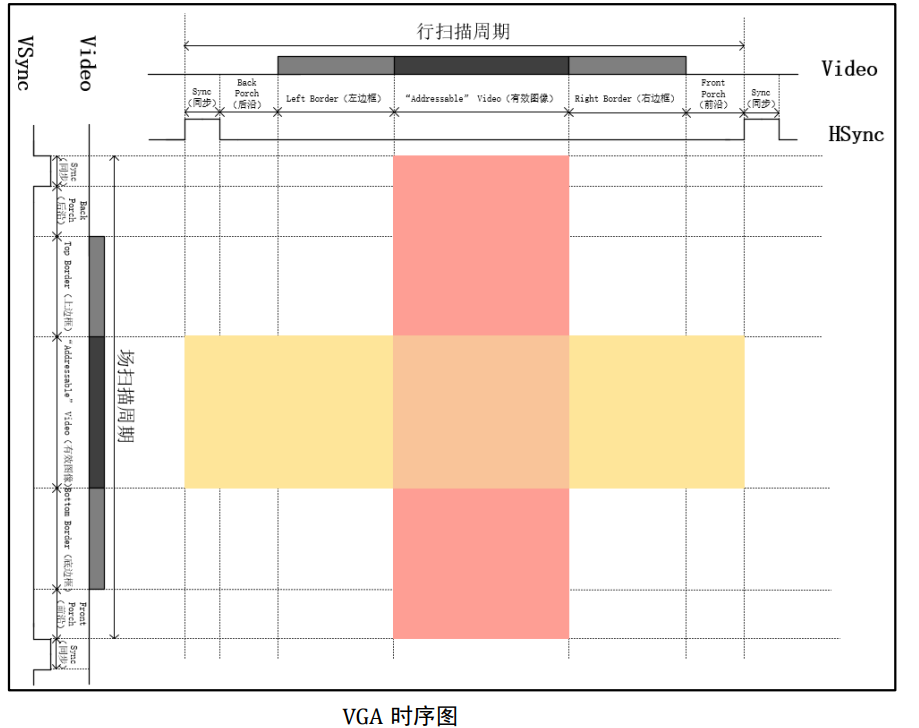

VSync 行同步信号在 Sync(同步)阶段,维持高电平,其他阶段均保持低电平,完成一个场扫描周期后,进入下一帧图像的扫描。将行同步时序图与场同步时序图结合起来就构成了 VGA 时序图

其他文档:

https://www.likecs.com/show-204108749.html

参考文章:

征途Pro《FPGA Verilog开发实战指南——基于Altera EP4CE10》

https://blog.csdn.net/xuhao0258/article/details/119481873

浙公网安备 33010602011771号

浙公网安备 33010602011771号