芯片仿真验证——CDC

随着技术的发展,数字电路的集成度越来越高,设计也越来越复杂。很少有系统会只工作在同一个时钟频率。一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。如果一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossing)问题。

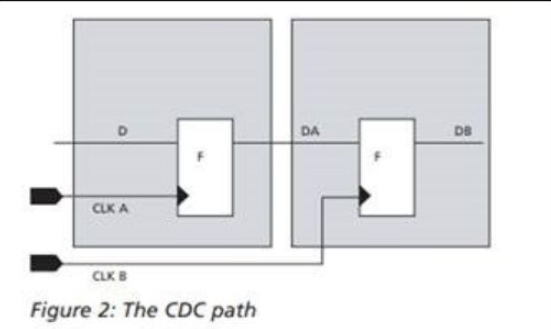

如下图中,CLKA和CLKB之间没有固定的相位关系,是异步时钟。前半部分设计属于时钟域CLKA,后半部分设计属于时钟域CLKB。DA信号从时钟域CLKA进入到时钟域CLKB,是一个跨时钟域的信号,这条path也会被称为CDC path。

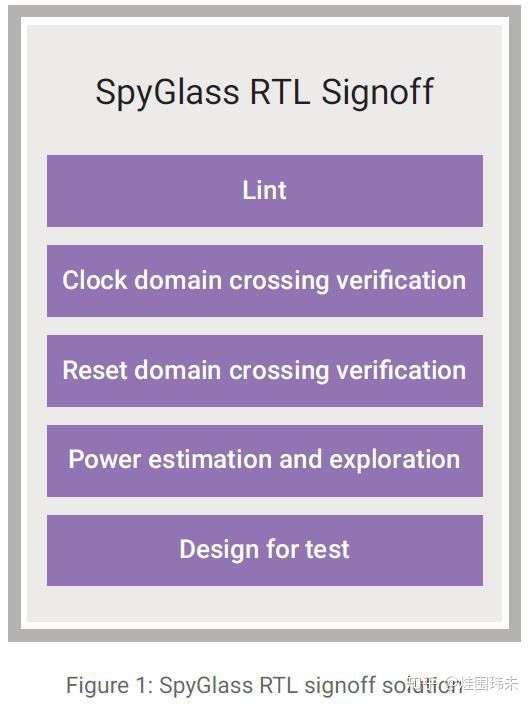

SpyGalss是目前业界唯一可靠的RTL Sign off解决方案,可以帮助客户在设计早期发现潜在问题,保证产品质量,极大的减少设计风险,降低设计成本。

包含五大模块:

①、lint :检查verilog代码的语法和可综合性

②、CDC(跨时钟域检查):识别各种FIFO和握手信号

③、LP(低功耗):在未进行DC和PR之前对verilog进行功耗分析

④、Constraint(约束):验证SDC文件的正确性

⑤、DFT(可测试性):测试ATPG的覆盖率分析

SpyGlass CDC分析使你能够识别设计中的CDC问题。SpyGlass CDC tool是一种 Formal Check Methodology工具, 相比写case跑仿真来找CDC问题, 靠SpgGlass能更早,更全,更快的发现CDC问题. 它能够:

- 管理是多时钟域设计

- 系统地处理CDC问题

- 检查和报告任何不同步的信号: 时钟和复位

SpyGlass CDC与静态时序分析相比:

STA对async interface不太好使,只适合sync模块分析

CDC paths 总是需要设置成false paths

一般在design的后期在netlist level做才有意义

SpyGlass CDC与功能仿真相比:

- 黑盒测试很难穷举(exhaust)

- 白盒测试需要assertions

- 需要覆盖CDC的所有test branches

- 很难幸运的覆盖所有,一般只能发现部分问题

- 一般在design后期才发现问题

当SOC design涉及的clock domain太多,用到很多第三方IP,及涉及人员水平参差不齐时, 用SpyGlass CDC来做检查来保证RTL质量是十分必要的.

在工程的block-level和SOC 集成的两个不同阶段, 所适用的CDC Goal也是有所不同的. Block-Level关心的是模块内部, 只有模块内检查没问题后才能做deliver. 而SOC集成主要关心的是模块间interface的CDC问题.

CDC常见问题:

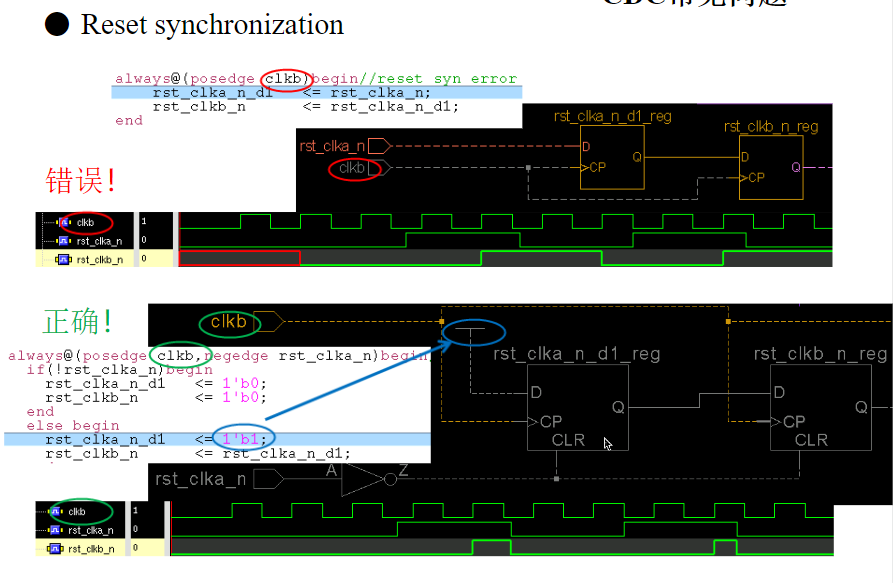

reset synchronization 复位同步

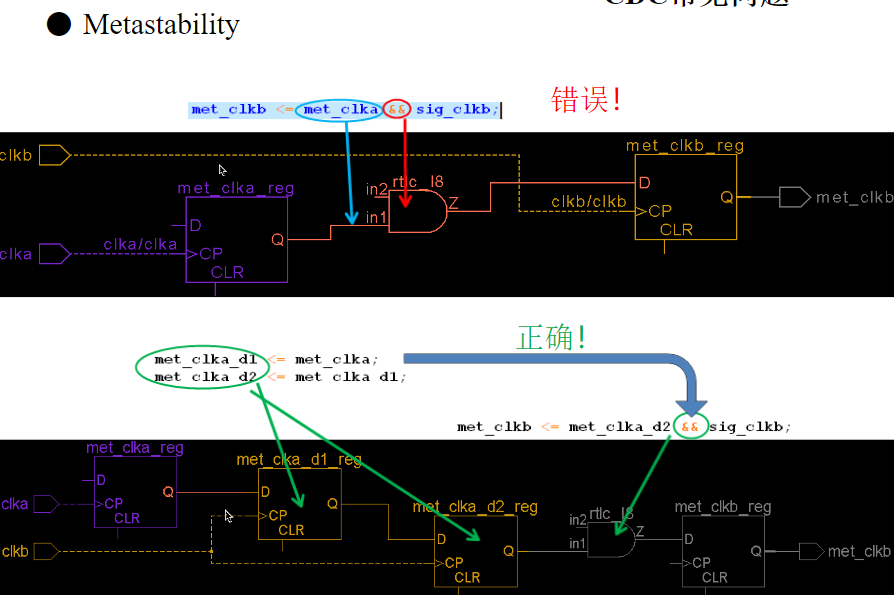

metastability 亚稳态问题

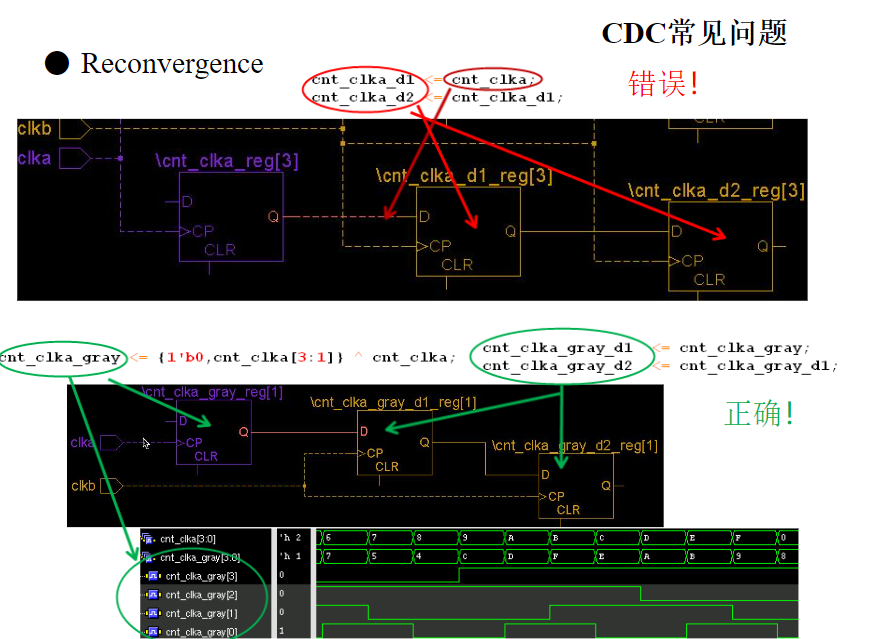

reconvergence

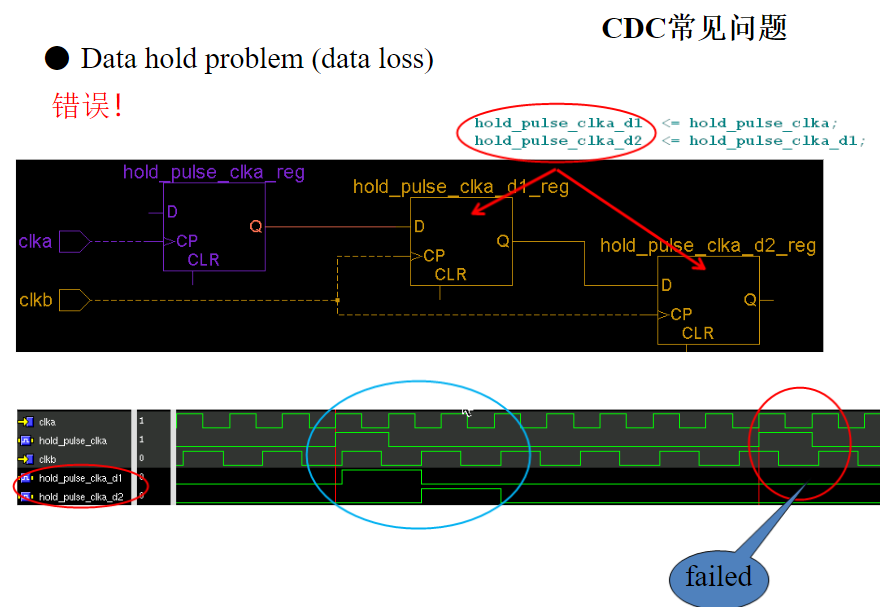

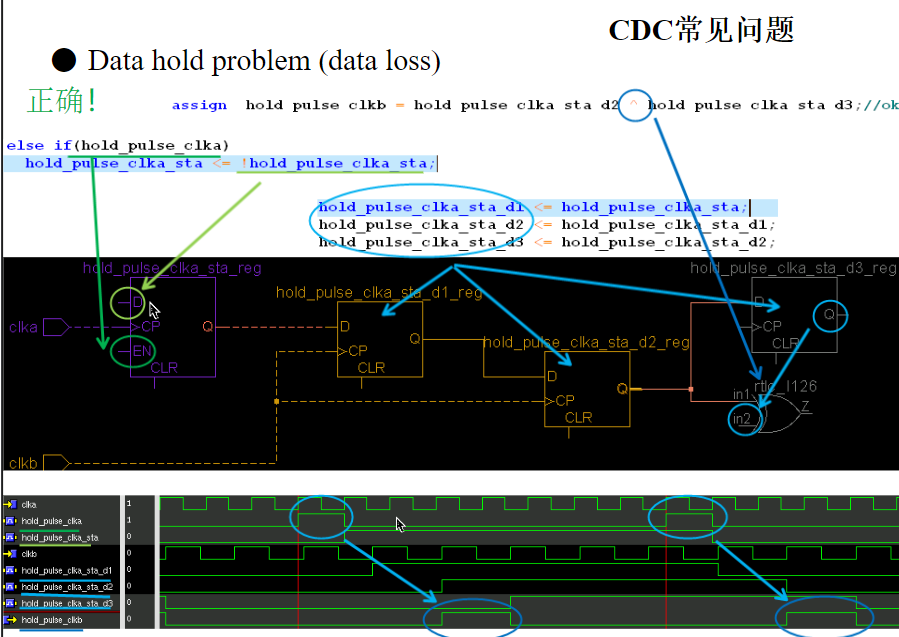

Data hold problem (data loss)数据保存问题(数据丢失)

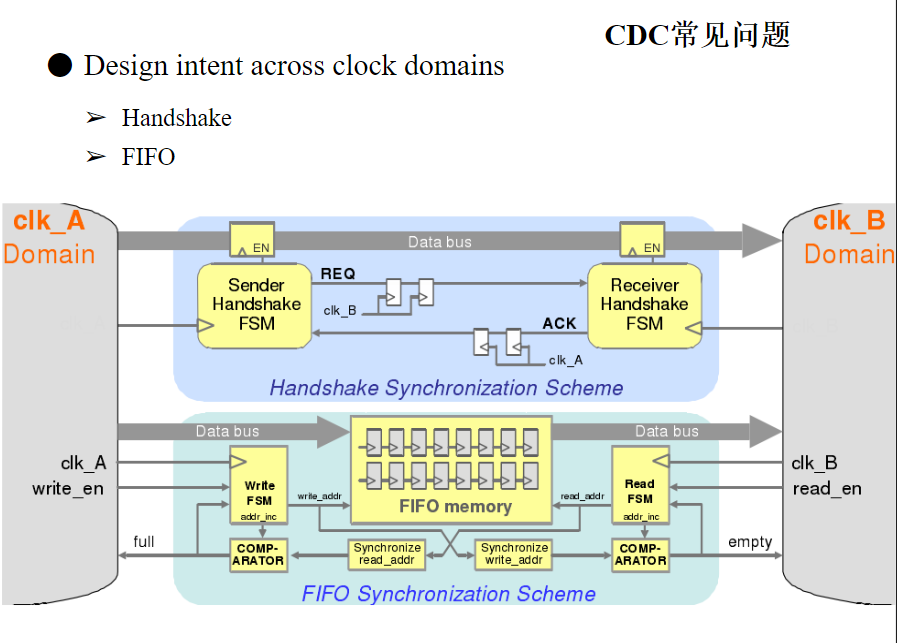

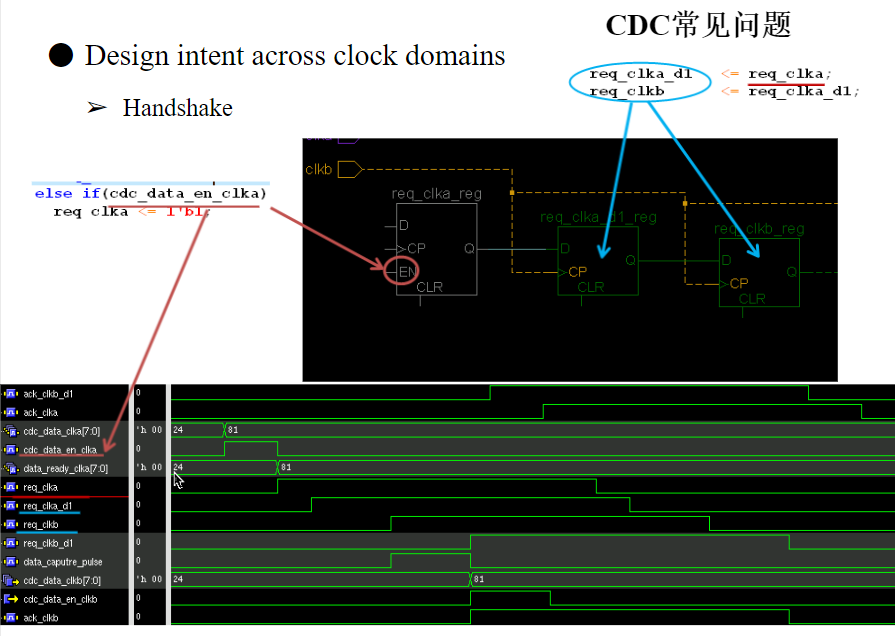

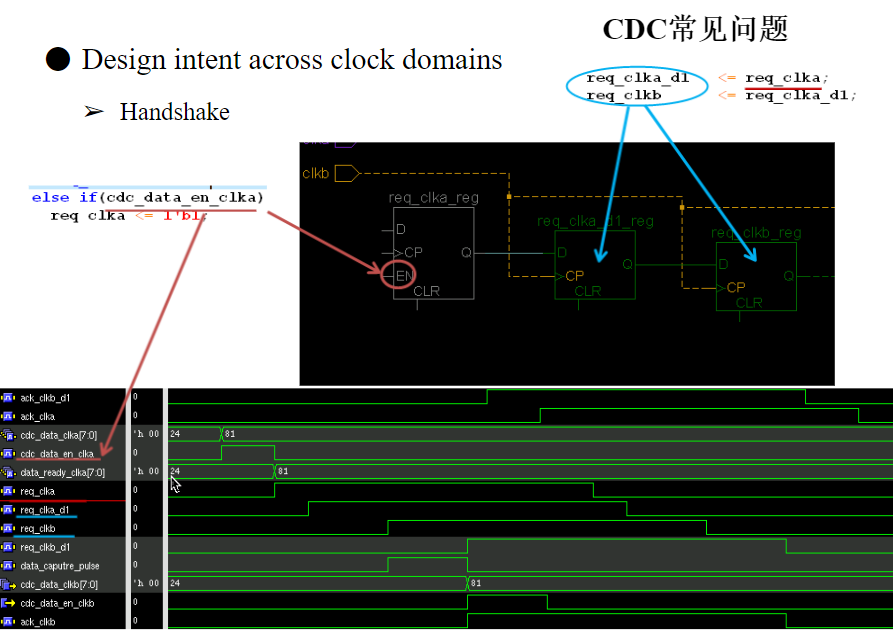

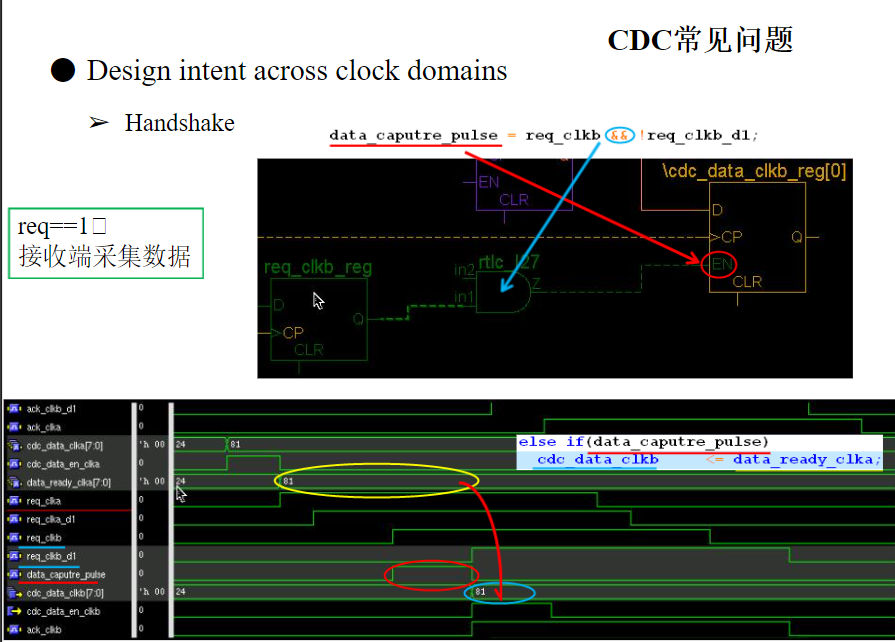

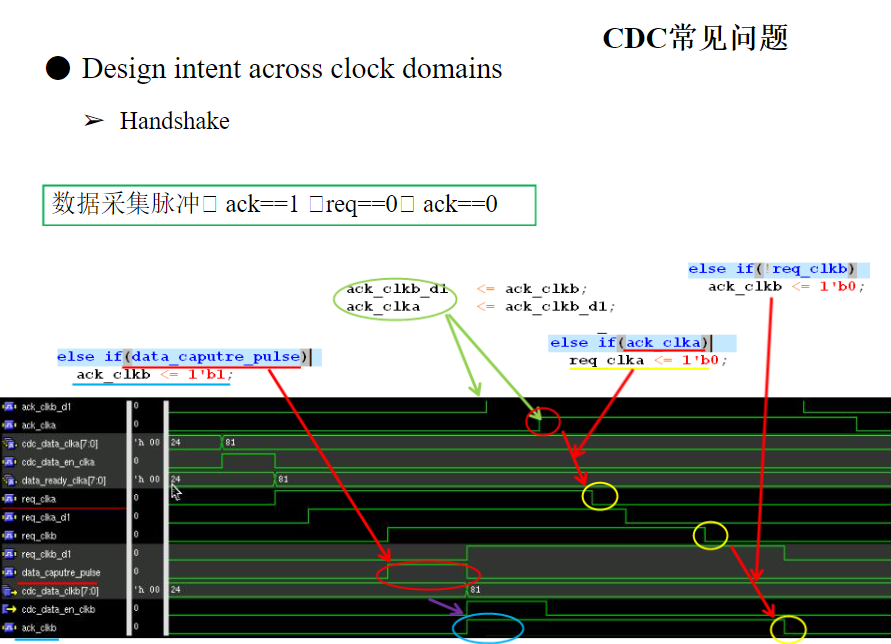

Design intent across clock domains

reset synchronization

metastability

reconvergence

Data hold problem (data loss)

Design intent across clock domains

转载or参考处:

https://max.book118.com/html/2016/1101/60956731.shtm

https://zhuanlan.zhihu.com/p/116888880

https://blog.csdn.net/qq_21842097/article/details/122538986?utm_medium=distribute.pc_aggpage_search_result.none-task-blog-2

浙公网安备 33010602011771号

浙公网安备 33010602011771号