quartus 实践

目前最好的教程是正点原子,黑金等稍逊,其他品牌就是纯粹的verilog ,很少涉及强大的 platform 。

对于软核 一般两个总线,数据总线连接所有乱七八糟的外设接口,具体每个接口内部我看了,乱七八糟。但是他们就是能工作,机制不了解。ram和rom 要同时连接指令总线和数据总线(但是如果rom有两个接口,数据命令总线分开 哈佛结构/冯诺依曼?)。

issp使用,quartus18

-

Probe:probe,抓取模块内部信号值,在电脑上实时观察模块内部信号值。

Sources:驱动源,连接被测模块的一些寄存器,通过电脑如果上面提供了一个值,这个值会实时写入板卡的寄存器中;通过驱动寄存器,可以观察其他模块的响应 - 总体来说 probe输出到电脑 source电脑输入

- 重要使用platform 创建ip 要是用文件添加功能添加到工程才能使用

乘法器和普通乘法器有什么区别,为什么要用ip实现乘法器。主要是为了节省dsp。标准dsp 是9*9 或者18*18.如果操作数超过这个位宽,那么将造成浪费,乘法ip可以使用部分逻辑单元代替零头dsp,从而节省dsp单元

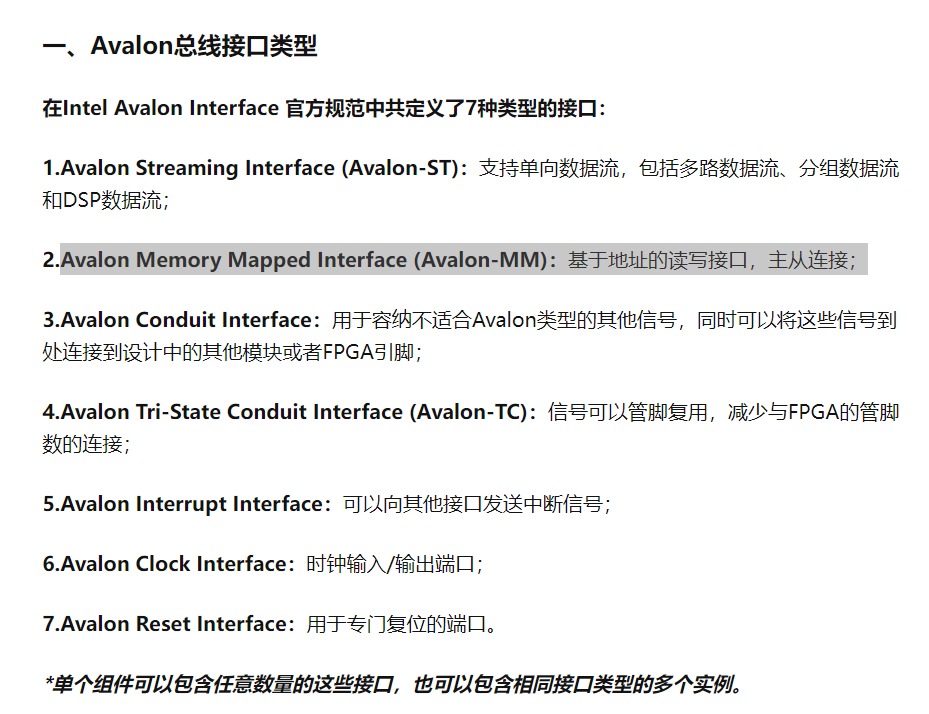

对于Avalon接口,fpga内部软核和各个从器件 大多采用该接口

PIO IP 的作用主要用于控制io,每个PIO最高32个io

一般外设地址要锁定

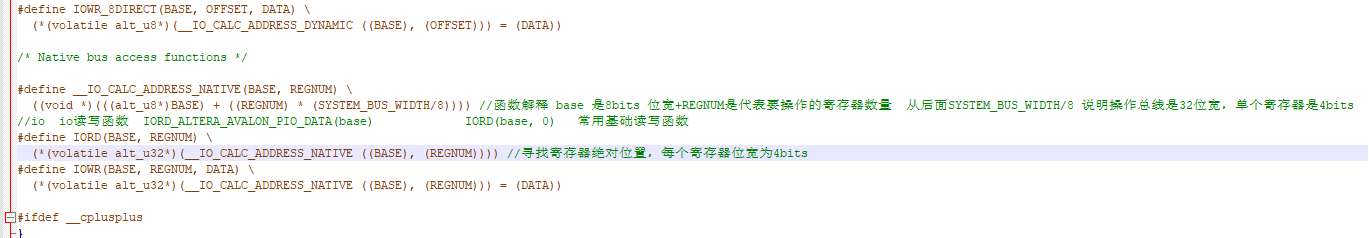

软核cpu和逻辑单元如何通信? alter做了一个通信机制,使用qsys自动生成底层代码,通过sys.h代码可以看到对软核cpu的配置参数,以及关键寄存器地址定义,这里和qsys定义的地址匹配对应。然后使用专用的接口函数在c代码实现cpu数据输出,以及外部寄存器读取。

quartus ii 调试神器 jtag-uart 该工具注意事项

1.c语言相关位置 打开printf 相关的开关。(uart有两种,一种是使用jtag模拟,也就是我们对接板子不需要更多的io,jtag既可以下载也可以串口通信,但是串口助手不能用,只能使用altera自己的软件。另一种就是逻辑实现串口,需要两根额外的串口线,重新定位c语言printf的接口)

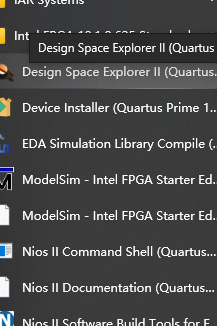

2.找到comm tool 命令工具,找了很久。发现在 电脑程序 ,ide里面是没有的

打开工具nios2-terminal 工具。使用命令工具定位到 bin64文件夹,这里面就有这个exe。其实直接打开这个exe执行文件也是可以的。

这样printf就可以用了

对于未使用引脚 最上层 最好删除,不然会告知 有一个引脚未布线的错误

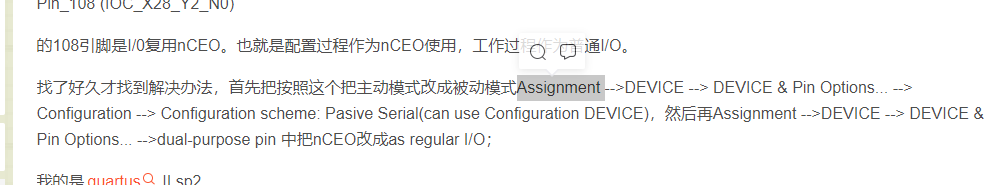

1. 引脚复用

2.对于 cyclone iv 来说 lck io 无法作为输出引脚 但是可以作为输入。cyclone v 仍然是标准io。cl10 系列几乎是 ep4ce 系列的马甲产品

3. ucf 管脚配置文件 ‘|’ 周围必须有空格

浙公网安备 33010602011771号

浙公网安备 33010602011771号