fpga vhdl 基础知识 根据2-8原则,你只需要熟悉掌握2成基本操作就可以熟练地实现大部分基本功能

vhdl 稍微老久一些,用起来还可以,受c语言影响大,要加入头文件,声明函数 但又不太像c,不仅仅是并行不并行。存在周期比较长,像c一样 维护了很多的库文件。verilog 做的有点现代化语言便捷了一些,像python java, 用起来更像c语言。

vhdl常用知识

1.function 和 procedure 过程区别,function 不消耗时间不能使用任何等待语句,procedure 可以使用等待所以称为过程语句

2. := 立即赋值语句 变量只能用这个。 => 指示链接指示不指示方向

3.vhdl长使用 a(0) &a(1) = a(1)&a(2) 来实现移位操作,‘&’操作并不是指c语言的按位与,而是合并组装的意思,bit(0)&bit(1) ,"0"&a 指的是在a高位添加一位,假如a原来是8bits后变为9bits,同时该功能常被用于延迟信号 a(55 downto 0) 假如我每次只用a(0),我通过移位可以实现最大56个时钟延迟

xilink 与 alter 区别 主要是 ise(lod)与 quartus的区别。两者操作相似,但是同类别 xilink的fpga速度较快,逻辑较少,价格偏贵。而alter的逻辑偏多,价格便宜,quartus 内部集成自家专用软核和图形化模组配置强大的引脚配置工具,适合新老手操作,一定程度降低了开发的复杂性。最重要的是配合完善的软核库,你可以像开发单片机一样开发alter的fpga,非常适合mcu升级fpga选手。可以体现出跨界编程的优势。赞!

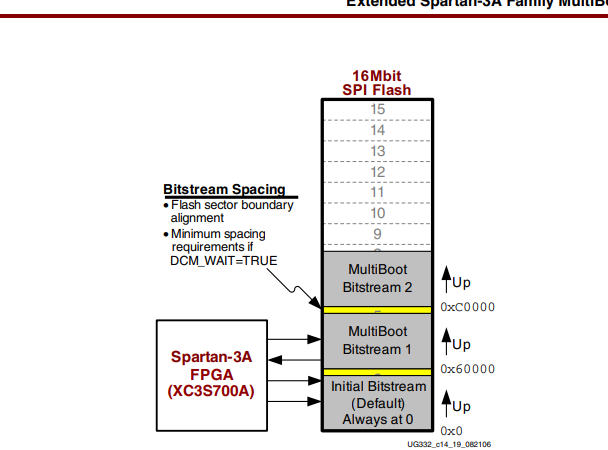

dcm 等待情况下要计算两个 app的间隔空间,另外flash 块对其

加入你只是更改软核代码 请使用data2mem 这样你不必要再进行代码vhdl的编译工作。

以下是处理 软核处理器的ram问题 http://forum.6502.org/viewtopic.php?f=10&t=2575

// BMM LOC annotation file. // // Release 14.6 - P.20131013, build 3.0.10 Apr 3, 2013 // Copyright (c) 1995-2022 Xilinx, Inc. All rights reserved. /////////////////////////////////////////////////////////////////////////////// // // Processor 'softcore_top', ID 0, memory map. //因此,要使用 Data2MEM 修补比特流文件,我需要创建一个与 MEM 文件格式兼容的数据文件。MEM 文件格式非常简单。它本质上是一个包含 ASCII 十六进制地址和数据的文件。地址以@符号开头,并通过空格或换行符与数据分隔。如果多个数据元素用空格分隔,则可以将它们放在一行上。在提供另一个@地址之前,假定它们的地址是连续的 类似hex文件 //事实上,Data2MEM 预期的每个数据字中的半字节顺序是完全颠倒的 @0000 ffc 500 600 e0c -> cff 005 006 coe //(1) 确定要修补的块 RAM 的网表名称。 //(2) 创建一个BMM文件并附加到工程文件列表中。(此时Loc/Patch约束可选) //(3)设置Translate的“Other Ngdbuild Command Line Options”引用BMM文件:-bm myBMM<.bmm> //(4)运行Synthesis、MAP和PAR、BitGen。检查 BitGen 的 myBMM_db.bmm 文件,并约束 myBMM 中定义的块 RAM。 //(5) 创建 MEM 文件以修补成比特流文件。 //(6) 设置BitGen 的“Other Bitgen Command Line Options”启用实时补丁:-bd myMEM.mem //(7) 重新运行MAP、PAR、BitGen,将打补丁的比特流文件下载到目标。(此时可以为 FPGA 创建 PROM 文件。) /////////////////////////////////////////////////////////////////////////////// ADDRESS_MAP softcore_top PPC405 0 /////////////////////////////////////////////////////////////////////////////// // // Processor 'softcore_top' address space 'memory1' 0x00000000:0x00003FFF (16 KBytes). // /////////////////////////////////////////////////////////////////////////////// ADDRESS_SPACE memory1 RAMB16 [0x00000000:0x00003FFF] BUS_BLOCK /Mram_ram8 RAMB16 [31:28] [0:4095] PLACED = X0Y8; /Mram_ram7 RAMB16 [27:24] [0:4095] PLACED = X0Y6; /Mram_ram6 RAMB16 [23:20] [0:4095] PLACED = X0Y7; /Mram_ram5 RAMB16 [19:16] [0:4095] PLACED = X0Y5; /Mram_ram4 RAMB16 [15:12] [0:4095] PLACED = X0Y2; /Mram_ram3 RAMB16 [11:8] [0:4095] PLACED = X0Y4; /Mram_ram2 RAMB16 [7:4] [0:4095] PLACED = X0Y3; /Mram_ram1 RAMB16 [3:0] [0:4095] PLACED = X0Y1;//2k=512*8 END_BUS_BLOCK; END_ADDRESS_SPACE; END_ADDRESS_MAP;

未使用的port组件 不分配网络 会报错。对于这种你可以使用 open ,或者在声明时候删除该端口或者赋初值

纯函数 和脏函数 的区别,本质区别是 脏函数可以自由调用读取甚至修改函数外的信号。纯函数不行。

verilog 对格式化非常 关键 如果出现莫名故障 可以尝试先格式化文档

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】凌霞软件回馈社区,博客园 & 1Panel & Halo 联合会员上线

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步