HDLBits: Exams/m2014 q6c

1、 Exams/m2014 q6c

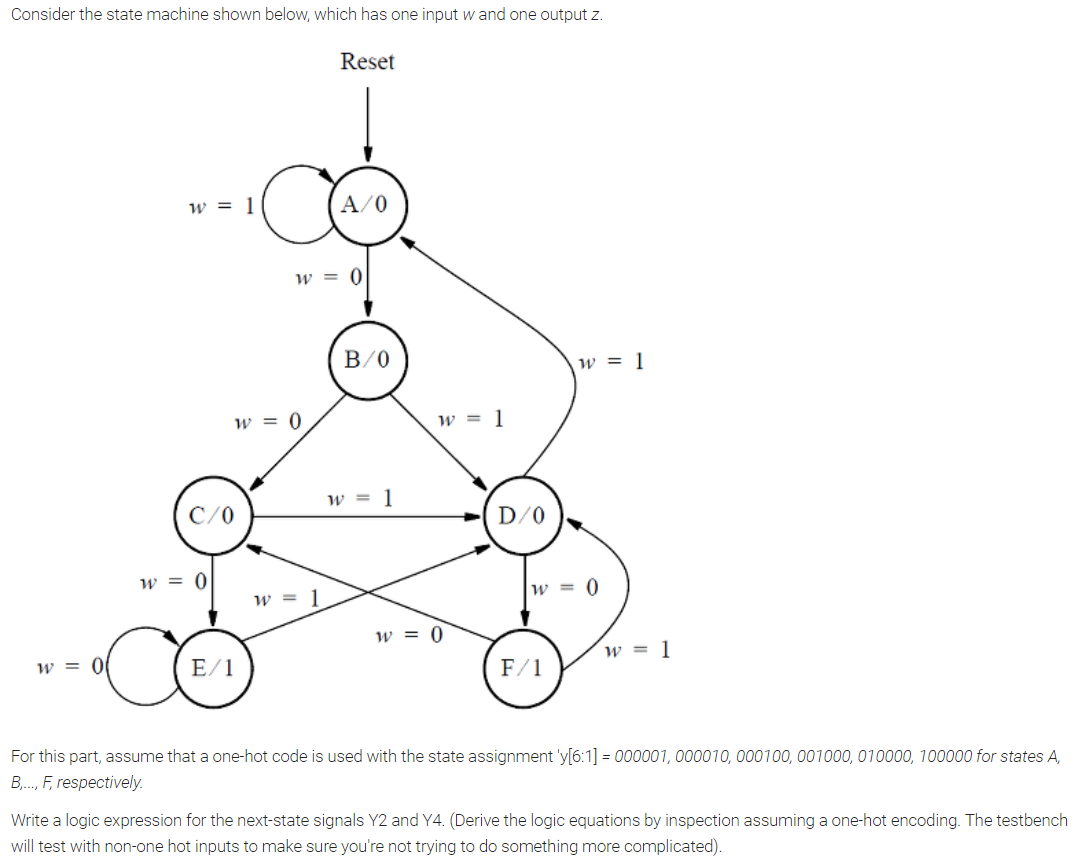

#1、状态转换图

#2、分析

这道题需要注意的地方是:每一位都是独立转换的,比如 A -> B的转换的实际意义是,如果y[1] == 1 且w == 0,那么next_state[2]就会转换为1。

#3、实现

按照上述思想写出的代码如下,可以简化,比如 next_state[1] = (y[1] == 1) &(w == 1) | (y[4] == 1)&(w == 1) = (y[1] | y[4]) & (w) ;

甚至可以简化出: assign Y2 = y[1] & (~w);

module top_module ( input [6:1] y, input w, output Y2, output Y4); parameter A=6'b000001, B=6'b000010, C=6'b000100, D=6'b001000, E=6'b010000, F=6'b100000; reg [6:1] next_state; /* always @(*) begin case(y[6:1]) A: next_state = w ? A : B; B: next_state = w ? D : C; C: next_state = w ? D : E; D: next_state = w ? A : F; E: next_state = w ? D : E; F: next_state = w ? D : C; default: next_state = 6'bxxxxxx; endcase end */ always @(*) begin next_state = 6'b0; //别忘了 if(y[1]) if(w) next_state[1] = 1; else next_state[2] = 1; if(y[2]) if(w) next_state[4] = 1; else next_state[3] = 1; if(y[3]) if(w) next_state[4] = 1; else next_state[5] = 1; if(y[4]) if(w) next_state[1] = 1; else next_state[6] = 1; if(y[5]) if(w) next_state[4] = 1; else next_state[5] = 1; if(y[6]) if(w) next_state[4] = 1; else next_state[3] = 1; end always @(*) begin Y2 = next_state[2]; Y4 = next_state[4]; end //assign Y2 = next_state[2]; //assign Y4 = next_state[4]; endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号