tq2440开发板基本配置

- 时钟配置及分配

tq2440的晶振频率是12MHz,在uboot中有如下语句:

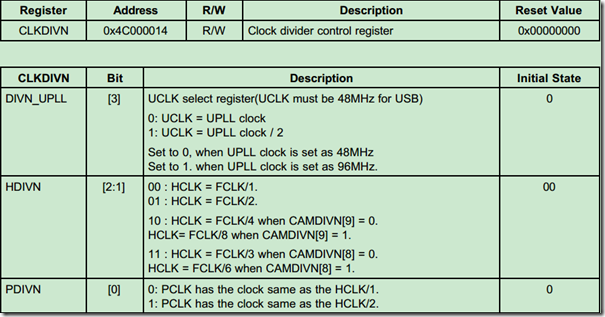

#define S3C2440_CLKDIV 0x05 /* FCLK:HCLK:PCLK = 1:4:8, UCLK = UPLL */ //HJ 100MHz

#define S3C2440_UPLL_48MHZ ((0x38<<12)|(0x02<<4)|(0x02)) //HJ 100MHz

/* Fin = 12.0000MHz */

#define S3C2440_MPLL_400MHZ ((0x5c<<12)|(0x01<<4)|(0x01)) //HJ 400MHz

void clock_init(void)

{

S3C24X0_CLOCK_POWER *clk_power = (S3C24X0_CLOCK_POWER *)0x4C000000;

/* FCLK:HCLK:PCLK = ?:?:? */

clk_power->CLKDIVN = S3C2440_CLKDIV; //HJ 1:4:8

/* change to asynchronous bus mod */

__asm__( "mrc p15, 0, r1, c1, c0, 0\n" /* read ctrl register */

"orr r1, r1, #0xc0000000\n" /* Asynchronous */

"mcr p15, 0, r1, c1, c0, 0\n" /* write ctrl register */

:::"r1"

);

/* to reduce PLL lock time, adjust the LOCKTIME register */

clk_power->LOCKTIME = 0xFFFFFF;

/* configure UPLL */

clk_power->UPLLCON = S3C2440_UPLL_48MHZ; //fin=12.000MHz

/* some delay between MPLL and UPLL */

delay (4000);

/* configure MPLL */

clk_power->MPLLCON = S3C2440_MPLL_400MHZ; //fin=12.000MHz

/* some delay between MPLL and UPLL */

delay (8000);

}

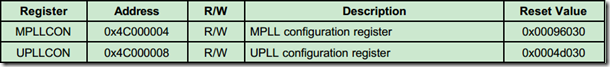

从上面的配置可以看到,与时钟相关的几个寄存器的配置值:

配置的值是:

MOLLCON = 0x5C011

UPLLCON = 0x38022

其中,Mpll就是FCLK UPLL就是UCLK

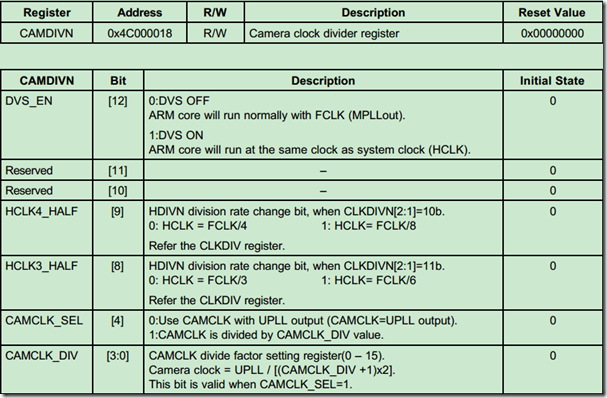

配置的值是:0x05

该寄存器没有配置,所以是初始值,也就是全0。

综上,FCLK:HCLK:PCLK = 1 : 4 : 8

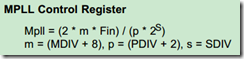

Mpll(FCLK) = (2 * (0x5c+8) * 12M)/((1+2) * 2) = (2*100*12M)/(6) = 400MHz

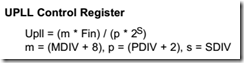

UPLL(UCLK) = ((0x38+8)*12M)/((2+2)*2^2) = (64*12M)/(16)=48MHz

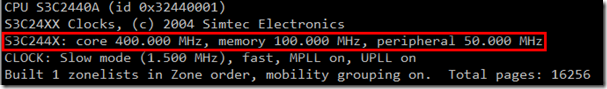

所以,FCLK=400MHz HCLK=100Hz PCLK=50MHz

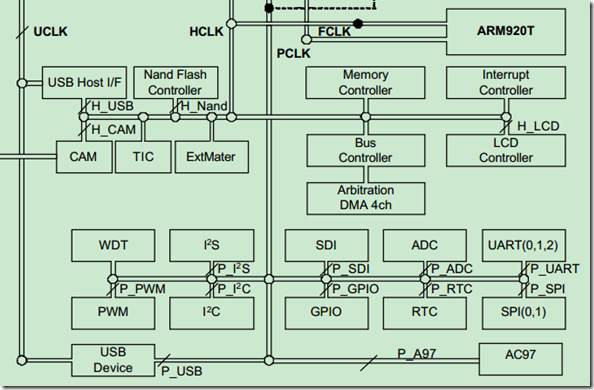

从上图可以看到系统中FCLK、HCLK、PCLK以及UCLK是如何分配给外设的。

其实也可以从系统的启动信息看出:

本文来自博客园,作者:摩斯电码,未经同意,禁止转载