引脚 CPU插槽 寄存器

https://baike.baidu.com/item/引脚/10879873

- 中文名

- 引脚

- 外文名

- pin

- 位 置

- 引线末端

- 组成部分

- 脚跟、脚趾、脚侧

- 别 名

- 管脚

- 重点作用

- 接口,接线

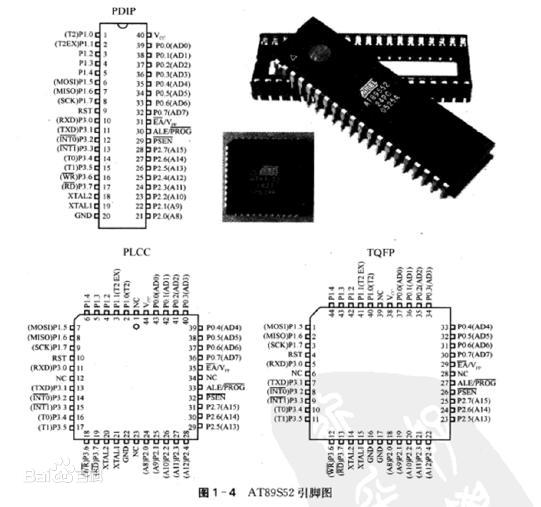

引脚是指从集成电路(芯片)内部电路引出与外围电路的接线,引脚构成了这块芯片的接口。按照功能,AT89S52的引脚可分为主电源、外接晶振或振荡器、多功能I/O口,以及控制、选通和复位四类。

(1)脚是一个多功能引脚,各种制式下的第二伴音中频信号可以用不平衡的方式从该脚进入内部的调频解调电路解调,同时它还是块内AV\TV转换和PAL、NTSC、SECAM彩色制式转换的控制引脚,输入阻抗大约3.4K。

(2)脚是识别输出脚,它以○C门方式输出图像识别信号,当TV方式已经接收到图像电视信号时,该脚对外呈现高阻抗,通过外接上拉电阻就能够得到高电平信号;当没有接收到信号时,该脚呈现低阻抗,输出低电平。

(3)脚是APC1滤波器端子,该芯片内部以振荡的方式产生38MHz开关信号完成图像中频信号的解调,产生的开关信号是否准确,就依靠自动相位控制电路(APC)控制。其中该脚上完成APC1误差信号的滤波。

(4)脚是APC2滤波器端子,第二级APC电路的滤波端。

(5)脚是石英晶体振荡器外接引脚,通过该脚外接的石英晶体和内部电路以串联共振的形式产生振荡。振荡频率为图像中频信号载频的四分之一。不同的信号制式下,所要求接入的石英晶体频率也不相同,其中PAL制式下需要的频率为38.90MHz×1/4,在NTSC制式下需要的频率为45.75MHz×1/4。另外得这两个引脚之间需要接上一个100±1%Ω的高精度电阻。

(6)脚是AFT信号输出脚,图像中频信号经过内部频率比较,从该引脚输出AFT误差信号。

(7)脚是全电视信号输出脚,图像中信号经过解调,最终从该脚输出视频信号和第二伴音中频信号,输出信号电平为2V。

(8)脚是射频AGC延迟调整引脚,通过调整外部的电位器,即能够实现AGC延迟量的调整。

(9)脚分别是内部和外部视频信号的输入引脚,信号输入时需要采用隔断 直流的方式,耦合电容容量为1uF,输入电平辐度为内部输入时为峰,峰值2V,外部输入时为峰,峰值1V,其输入阻抗大约是50kΩ。在集成电路内部,消隐电平被固定在4.5V。

(10) 脚是对比度控制电压的输出引脚,同时也可以用来控制ACL。

(11)脚是内藏滤波器的标准电平及S-VHS的开关,它需要一个1Uf 电容器接地来设定标准电平;当处于S-VHS方式时,要通过外电路把它的引脚电压设定在2V以下,处于普通的AV状态时,要把电压平设置在2V以上。

(12)脚是S-VHS方式的色度信号输入脚和直流控制的输入引脚,在输入色度信号时,需要用一个0.01Uf左右的电容隔断直流输入,在PAL制式下输入色度信号的电平应当为峰峰值300mV,在NTSC制式下输入色度信号的电平应当是峰峰值286mV。直流控制的情况是:对于LA7687,只有该脚加上5V的直流控制电压时,模拟控制总线才有效。

(13) 脚是延迟视频信号输出,还能实现ABL控制,输出视频信号的电平为峰峰值2V,还需要输入0.5mA以上的电流以实现ABL控制。

(14)脚是消色控制的输出脚,内部消色电路起控后将从该引脚输出一个低电平的信号。

(15)脚是模拟总线控制的地址输入引脚。

(16)脚是模拟总线控制的数据输入引脚。

(17)脚是多用引脚,它可以是内部场扫描脉冲的输出引脚;同时,外接电阻值的大小能够设定内部场同步分离的灵敏度;同时如果不需要内部的场脉冲,还可以从该脚输入其它的场脉冲信号,此时内部的场输出自动切断;它还是自动触发方式解除开关和行AFC选通解除开关。

(18)脚是50\60Hz识输出,集成电路内部通过对行频的计数,判断出场扫描频率,当频率是50Hz时,输出低电平;当频率是60Hz时,输出高电平。这个引脚和LA7837\8配合使用,能够自动地调整场幅度,可以给该脚一个固定的电平,实现工作一种场频下。例如仅使用50Hz,可以直接将该脚接地,如果仅使用60Hz可以把该脚接电源。

(19)脚是行AFC1的滤波引脚,AFC的直流偏压是H,VCC-3f,为了改善它对电源泳冲的特性,AFC滤波器设在电源一侧。C1是来消除场脉冲的电容器,R1是把控制电流转变为电压的电阻,而C2是用来平滑的滤波器,该脚的输出被限制在±2Vf之内。

(20)脚是行振荡石英晶体接入引脚,晶体频率应当是500Hz。

(21)脚是行振荡、行预激励电路单独供电引脚,较高的电压通过电阻为该脚提供一个直流电压,经过内部的稳压电路稳压成7V,供以上电路使用。电阻的选择计算是: R1=(+B1-7.0V)/13mA

(22)脚是行预激励脉冲输出引脚,以推挽方式输出。

(23)脚是行逆程脉冲的输入脚,沙堡\脉冲输出脚,行逆程脉冲信号经过内部形成沙堡脉冲之后再从该脚输出,作为部分电路统一的工作时序,该脚还是SECAM制式所用的集成电路V脉冲的输出脚.

(24)脚步是行一致性检测输出和SECAM制式参考信号输出脚,该脚输出了SECAM彩色解调所需要的4.43MHz考信号,同时还是行一致性检测器识别结果输出脚。如果图像行同步良好,该脚输出H.Vcc一半的高电平信号,相反如果行不同步,则变成低电位.

(25)脚是字符底色消隐脉冲输入引脚步,标准控制电压为1V,当输入电压高于1V时图像显示停止,字符显示在当前位置上,当该脚电压低于1V时,图像就显示在当前的位置上。

(26)脚是屏幕字符显示(OSD)三色信号的输入引脚,当使用模拟字符显示方式时,需要隔断直流输入,当用数字字符显示方式时,需要把高电平设置在4V上。

(27)脚是负极性亮度信号输出,该脚同时是消陷信号的输入引脚。

(28)脚是三个色差信号的输出引脚,分别输出电视图像的R-Y、G-Y、B-Y或者经过字符显示转换的R、G、B三色屏幕字符显示点阵。

(29)脚是ALC放大器(CCD延迟调整)的输入引脚步,经过集成一行延迟线延迟、运算之后,两个色差信号再从这两个引脚回到LA7687内。

(30)脚是对集成延迟线输出色差信号的引脚,在PAL制式时,两个解调不完全的色差信号从这两个引脚输出到延迟线进一步处理;当处于SECAM制式时,由于色差信号并不来自LA7687。所以在这个制式下该两个引脚呈现高阻抗状态。输出直流电压是3.6V。

(31)脚副载波恢复电路石英晶体的接入引脚,需要接4.43MHz和3.58/MHz的石英晶体。

(32)脚是彩色解调电路APC滤波引脚,外部的阻容器件组成的滤波器能够设定副载波振荡的同步范围。

(33)脚是第一级中放AGC滤波脚,AGC检测电路通过对视频信号峰值检波,分离出同步信号,在本脚滤波变成AGC电压,集成电路内部藏有第二级AGC滤波器。

(34)脚步是图像中频信号输入,经过声表面滤波器形成了特定中放曲线的图像中频信号,以平衡的方式从这两个引脚进入集电路内部放大;在集成电路内部,共有三级放大器,总的放大增益在60dB以上。

(35)脚是射频AGC的输出脚,以集电极开路方式输出。

(36)脚是音频信号输出脚,集成电路内部完成调频信号的解调,从该脚输出音频信号,在外部应有阻容器件组成的去加重电路。

(37)脚是音频滤波器脚,用于消除前置放大器的直流反馈,外部需要接1uF的电容器。另外当该脚设置为高电平时,图像中频就成为SECAM方式。 [1]

高压电容引脚断裂失效分析

环境应力筛选试验 (ESS试验)是考核导弹质量的必要手段。ESS试验中的随机振动试验旨在考核产品在结构、装配、应力等方面的缺陷。导弹在生产中要经历组件、舱段、全弹3级的ESS试验。在3级振动试验中多次出现发射机探测功率抖动或功率很小的故障现象,排查后发现是发射机组件的整流器电路板上高压电容的引脚在焊点处断裂引起。

整流器电路板上有10个贴片瓷介高压电容(在电路中起倍压或滤波作用),在两侧镀银电极焊接11 mm镀银铜丝后插装在印制板上,电容陶瓷底面距印制板小于0.5 mm,然后用电烙铁焊接,最后在电容底部涂1圈硅橡胶GD414以粘接固定在印制板上。通过对断口宏微观观察、化学成分分析和硬度检测、装配生产流程分析以及材料力学计算,确定断裂性质和原因,进而制定经济、可行、有效的补偿措施,并进行随机振动试验验证,从而使最终问题得到解决。这一研究对ESS试验的进行有较重要的工程应用价值。

工艺分析和改进措施

(1)固定胶分析和改进

硅橡胶拉伸强度为4~5 MPa,伸长率为100%~200%,分子间作用力弱,粘附性差,粘接强度低;而E-4X环氧树脂胶拉伸强度大于83 MPa,伸长率小于9%,粘合性好,粘接强度高,收缩率低,尺寸稳定。从性能上明显看出,E-4X环氧树脂胶才能对“悬臂梁”式的高压电容起到真正的固定作用。

(2)生产流程分析和改进

审查整流器电路板装配生产流程,发现是先装配高压电容再装配其它元件,这样立式高压电容为最高点,周转或放置时,电容易受到磕碰或外力而造成歪斜,每批电路板测试或固定前发现部分高压电容有歪斜现象,固定前人工进行了扶正。更改工序即先装配其它元件和粘接立柱再装配高压电容。这样周转或放置时比高压电容稍高的立柱受力,保护了高压电容。改进工序前,先对电路板真空涂覆(在电容陶瓷面上形成约15 μm厚的派埃林薄膜材料),再涂硅橡胶固定。改进后,先在电容上涂环氧胶,再在整个电路板真空涂覆,这样在电容和胶外表面一体形成派埃林薄膜。由于派埃林薄膜表面粗糙度小于陶瓷面,胶在派埃林薄膜表面的接触角大于陶瓷表面(接触角越小润湿效果越好),改进后固定效果更好。

分析与改进结果

高压电容是片式SMC,焊盘应设计成长方形的焊盘,焊接采用表面组装技术(SMT)回流焊接,这样高压电容不再是“悬臂梁”,正应力会因质心降低和受力面积增大而大幅度减小。重新对电路板设计可从根本上解决问题,但涉及大批量在制品的报废和返修,严重影响导弹的生产交付。

在X和Y方向随机振动中高压电容受交变的拉伸和剪切应力,硅橡胶粘接强度弱且固定不足高压电容高度的1/5,基本没有起到支撑作用,特别是Y向振动中电容在颤振,焊点处受到高频率的剪切应力,最终导致弯曲疲劳断裂。

电路板(试验件)换胶后通过了加强考核的随机振动试验,随后大批量正式产品进行返修。新投产的整流器电路板按照改进后的流程生产,用E-4X环氧树脂胶固定高压电容。返修后的产品和按改进措施新生产的产品在组件、舱段、全弹三级的ESS试验均未再发生高压电容引脚断裂故障,表明问题得到解决。

结论

1)高压电容引脚断裂性质是疲劳断裂;

2)装配方式设计不合理,固定胶粘接强度不够和工艺不完善是导致引脚断裂的原因;

https://baike.baidu.com/item/CPU插槽/5825574

- 中文名

- CPU插槽

- 外文名

- CPU socket

- 类 型

- Socket、Slot

- 接口方式

- 触点式、针脚式

- 特 点

- 不能互相接插

CPU插槽代表

Socket 478

我们知道,CPU需要通过某个接口与主板连接的才能进行工作。CPU经过这么多年的发展,采用的接口方式有触点式和针脚式。而CPU的接口都是针脚式接口,对应到主板上就有相应的插槽类型。CPU接口类型不同,在插孔数、体积、形状都有变化,所以不能互相接插。Socket 478

最初的Socket 478接口是早期Pentium 4系列处理器所采用的接口类型,针脚数为478针。Socket 478的Pentium 4处理器面积很小,其针脚排列极为紧密。英特尔公司的Pentium 4系列和P4 赛扬系列都采用此接口,这种CPU已经逐步退出市场。

但是,Intel于2006年初推出了一种全新的Socket 478接口,这种接口是Intel公司采用Core架构的处理器Core Duo和Core Solo的专用接口,与早期桌面版Pentium 4系列的Socket 478接口相比,虽然针脚数同为478根,但是其针脚定义以及电压等重要参数完全不相同,所以二者之间并不能互相兼容。随着Intel公司的处理器全面向Core架构转移,今后采用新Socket 478接口的处理器将会越来越多,例如即将推出的Core架构的Celeron M也会采用此接口。

Socket 939

Socket 939

Socket 939是AMD公司2004年6月才推出的64位桌面平台接口标准,具有939根CPU针脚,支持双通道DDR内存。采用此接口的有面向入门级服务器/工作站市场的Opteron 1XX系列以及面向桌面市场的Athlon 64以及Athlon 64 FX和Athlon 64 X2,除此之外部分专供OEM厂商的Sempron也采用了Socket 939接口。Socket 939处理器和与过去的Socket 940插槽是不能混插的,但是Socket 939仍然使用了相同的CPU风扇系统模式。从2006年开始AMD公司全面转向支持DDR2内存, 939被Socket AM2所取代,在2007年初完成自己的历史使命从而被淘汰,从推出到被淘汰其寿命还不到3年。

https://baike.baidu.com/item/寄存器/187682

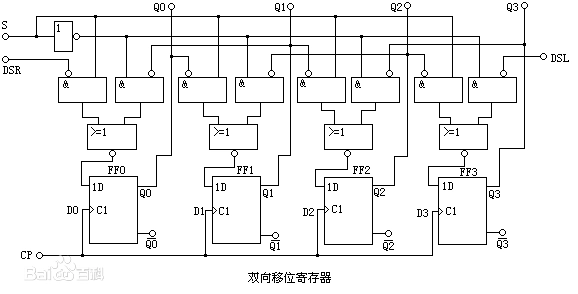

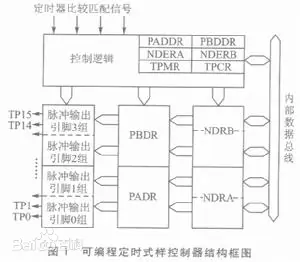

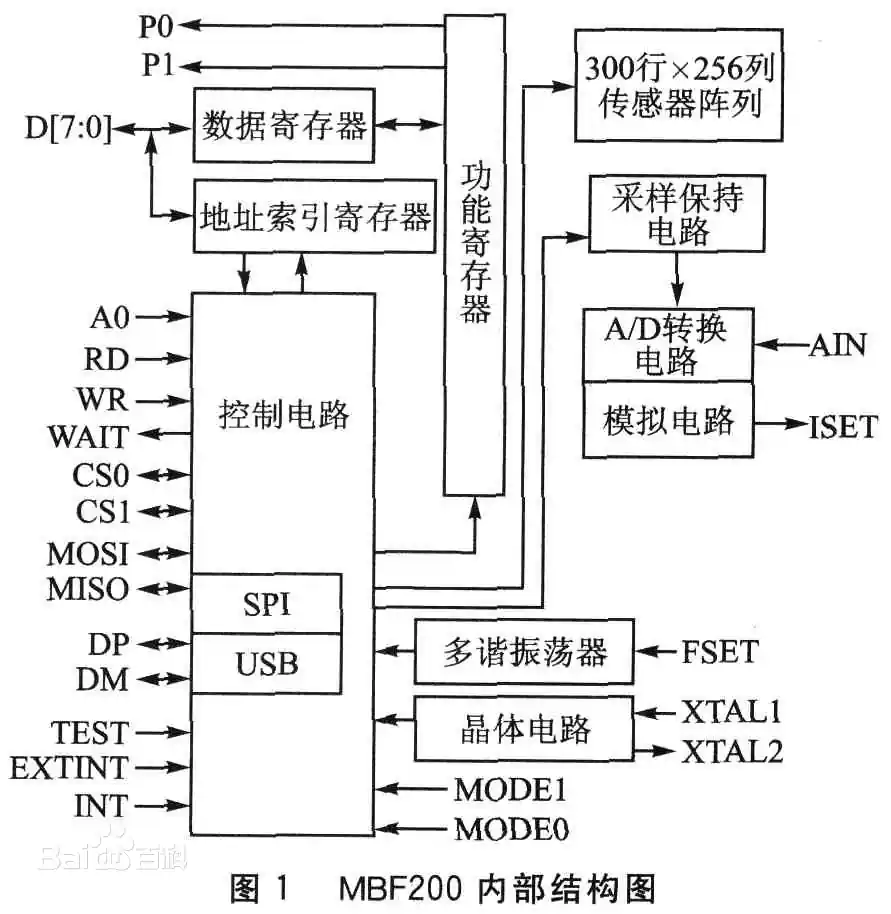

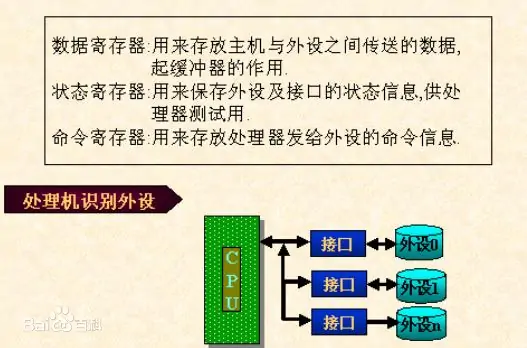

寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部分。寄存器是有限存储容量的高速存储部件,它们可用来暂存指令、数据和位址。 [2]

寄存器最起码具备以下4种功能。

①清除数码:将寄存器里的原有数码清除。 [3]

②接收数码:在接收脉冲作用下,将外输入数码存入寄存器中。 [3]

③存储数码:在没有新的写入脉冲来之前,寄存器能保存原有数码不变。 [3]

④输出数码:在输出脉冲作用下,才通过电路输出数码。 [3]

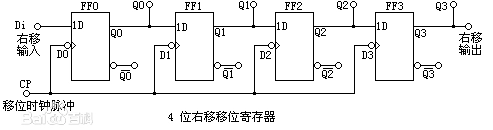

仅具有以上功能的寄存器称为数码寄存器;有的寄存器还具有移位功能,称为移位寄存器。 [3]

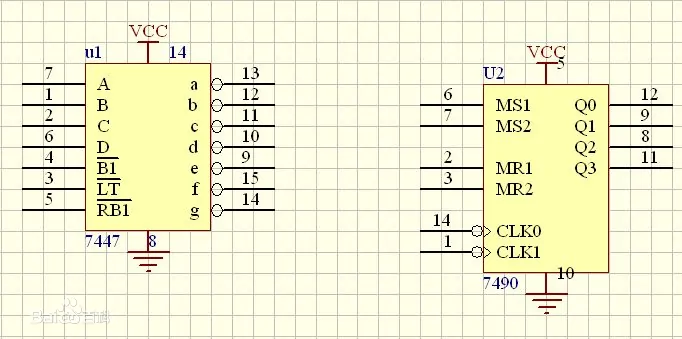

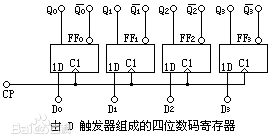

结构

74HC175则是用CMOS边沿触发器组成的4位寄存器,根据边沿触发的动作特点可知,触发器输出端的状态仅仅取决于CLK上升沿到达时刻D端的状态。可见,虽然74LS75和74HC175都是4位寄存器,但由于采用了不同结构类型的触发器,所以动作特点是不同的。 [4]

为了增加使用的灵活性,在有些寄存器电路中还附加了一些控制电路,使寄存器又增添了异步置零、输出三态控制和保持等功能。这里所说的保持,是指CLK信号到达时触发器不随D端的输入信号而改变状态,保持原来的状态不变。 [4]

工作原理

在计算机及其他计算系统中,寄存器是一种非常重要的、必不可少的数字电路构件,它通常由触发器(D触发器)组成,主要作用是用来暂时存放数码或指令。一个触发器可以存放一位二进制代码,若要存放N位二进制数码,则需用N个触发器。 [6]

寄存器应具有接收数据、存放数据和输出数据的功能,它由触发器和门电路组成。只有得到“存入脉冲”(又称“存入指令”、“写入指令”)时,寄存器才能接收数据;在得到“读出”指令时,寄存器才将数据输出。 [6]

寄存器存放数码的方式有并行和串行两种。并行方式是数码从各对应位输入端同时输入到寄存器中;串行方式是数码从一个输入端逐位输入到寄存器中。 [6]

寄存器读出数码的方式也有并行和串行两种。在并行方式中,被读出的数码同时出现在各位的输出端上;在串行方式中,被读出的数码在一个输出端逐位出现。 [6]

类型

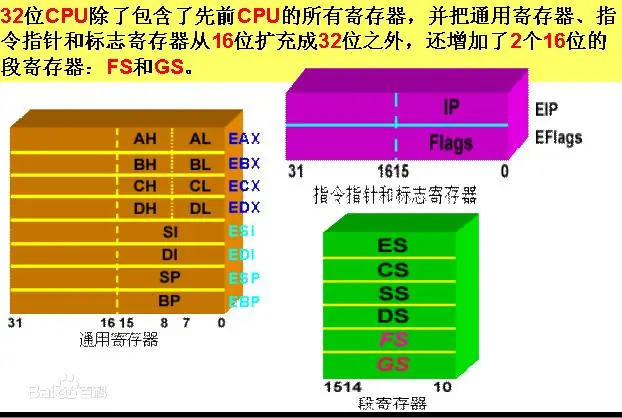

1.通用寄存器组

通用寄存器组包括AX、BX、CX、DX4个16位寄存器,用以存放16位数据或地址。也可用作8位寄存器。用作8位寄存器时分别记为AH、AL、BH、BL、CH、CL、DH、DL。只能存放8位数据,不能存放地址。它们分别是AX、BX、CX、DX的高八位和低八位。若AX=1234H,则AH=12H,AL=34H。通用寄存器通用性强,对任何指令,它们具有相同的功能。为了缩短指令代码的长度,在8086中,某些通用寄存器用作专门用途。例如,串指令中必须用CX寄存器作为计数寄存器,存放串的长度,这样在串操作指令中不必给定CX的寄存器号,缩短了串操作指令代码的长度。下面一一介绍:

AX(AH、AL):累加器。有些指令约定以AX(或AL)为源或目的寄存器。输入/输出指令必须通过AX或AL实现,例如:端口地址为43H的内容读入CPU的指令为INAL,43H或INAX,43H。目的操作数只能是AL/AX,而不能是其他的寄存器。 [5]

CX(CH、CL):计数寄存器。CX在循环和串操作中充当计数器,指令执行后CX内容自动修改,因此称为计数寄存器。 [5]

2.指针和变址寄存器

SI( Source Index Register):源变址寄存器。 [5]

DI( Destination Index Register):目的变址寄存器。 [5]

这组寄存器存放的内容是某一段内地址偏移量,用来形成操作数地址,主要在堆栈操作和变址运算中使用。BP和SP寄存器称为指针寄存器,与SS联用,为访问现行堆栈段提供方便。通常BP寄存器在间接寻址中使用,操作数在堆栈段中,由SS段寄存器与BP组合形成操作数地址即BP中存放现行堆栈段中一个数据区的“基址”的偏移量,所以称BP寄存器为基址指针。 [5]

寄存器SI和DI称为变址寄存器,通常与DS一起使用,为访问现行数据段提供段内地址偏移量。在串指令中,其中源操作数的偏移量存放在SⅠ中,目的操作数的偏移量存放在DI中,SI和DI的作用不能互换,否则传送地址相反。在串指令中,SI、DI均为隐含寻址,此时,SI和DS联用,Dl和ES联用。 [5]

3.段寄存器

8086/8088CPU可直接寻址1MB的存储器空间,直接寻址需要20位地址码,而所有内部寄存器都是16位的,只能直接寻址6KB,因此采用分段技术来解决。将1MB的存储空间分成若干逻辑段,每段最长64KB,这些逻辑段在整个存储空间中可浮动。 [5]

8086/8088CPU内部设置了4个16位段寄存器,它们分别是代码段寄存器CS、数据段寄存器DS、堆栈段寄存器SS、附加段寄存器ES、由它们给出相应逻辑段的首地址,称为“段基址”。段基址与段内偏移地址组合形成20位物理地址,段内偏移地址可以存放在寄存器中,也可以存放在存储器中。 [5]

例如:代码段寄存器CS存放当前代码段基地址,IP指令指针寄存器存放了下一条要执行指令的段内偏移地址,其中CS=2000H,IP=001AH。通过组合,形成20位存储单元的寻址地址为2001AH。 [5]

代码段内存放可执行的指令代码,数据段和附加段内存放操作的数据,通常操作数在现行数据段中,而在串指令中,目的操作数指明必须在现行附加段中。堆栈段开辟为程序执行中所要用的堆栈区,采用先进后出的方式访问它。各个段寄存器指明了一个规定的现行段,各段寄存器不可互换使用。程序较小时,代码段、数据段、堆栈段可放在一个段内,即包含在64KB之内,而当程序或数据量较大时,超过了64KB,那么可以定义多个代码段或数据段、堆栈段、附加段。现行段由段寄存器指明段地址,使用中可以修改段寄存器内容,指向其他段。有时为了明确起见,可在指令前加上段超越的前缀,以指定操作数所在段。 [5]

4.指令指针寄存器IP

8086/8088CPU中设置了一个16位指令指针寄存器IP,用来存放将要执行的下一条指令在现行代码段中的偏移地址。程序运行中,它由BIU自动修改,使IP始终指向下一条将要执行的指令的地址,因此它是用来控制指令序列的执行流程的,是一个重要的寄存器。8086程序不能直接访问IP,但可以通过某些指令修改IP的内容。例如,当遇到中断指令或调用子程序指令时,8086自动调整IP的内容,将IP中下一条将要执行的指令地址偏移量入栈保护,待中断程序执行完毕或子程序返回时,可将保护的内容从堆栈中弹出到IP,使主程序继续运行。在跳转指令时,则将新的跳转目标地址送入IP,改变它的内容,实现了程序的转移。 [5]

5.标志寄存器FR

标志寄存器FR也称程序状态字寄存器。 [5]

存放代码满足条件

(1)代码要存得进;

(2)代码要记得住;

(3)代码要取得出。 [7]

寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位2进制代码,存放n位2进制代码的寄存器,需用n个触发器来构成。对寄存器中的触发器只要求它具有置1、置0的功能即可,因而无论用何种类型的触发器都可组成寄存器。 [7]

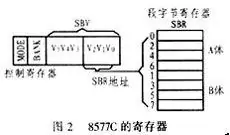

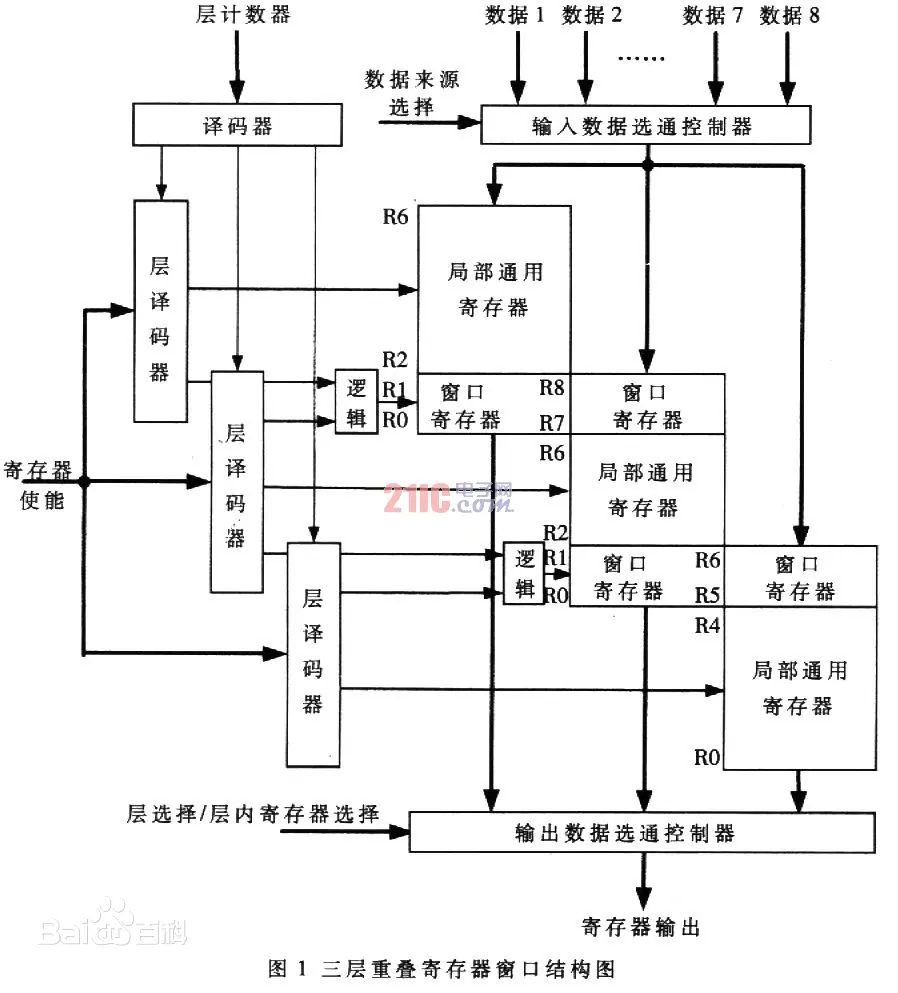

寄存器组织

ARM微处理器共有37个32位寄存器,其中31个为通用寄存器,6个为状态寄存器。但是这些寄存器不能被同时访问,具体哪些寄存器是可编程访问的,取决于微处理器的工作状态及具体的运行模式。但在任何时候,通用寄存器R14~R0、程序计数器PC、一个或两个状态寄存器都是可访问的。 [8]

ARM9处理器共有37个32位长的寄存器,这些寄存器包括:

(2)堆栈指针:堆栈指针的最低两位永远是O,这意味着堆栈总是4字节对齐的。 [9]

(4)程序计数器:指向当前的程序地址,如果修改它的值,就能改变程序的执行流。 [9]

(5)6个状态寄存器(1个CPSR、5个SPSR),用以标识CPU的工作状态及程序的运行状态,均为32位,目前只使用了其中的一部分。 [9]

Cortex-A8处理器有40个32位长的寄存器,多了监控模式下的寄存器,如RO~R12、R15、CPSR通用,R13_ mon、R14_mon、SPSR_mon三个专用寄存器。 [9]

寄存器寻址

寄存器寻址是指操作数存放在CPU内部的寄存器中,指令中给出操作数所在的寄存器名。寄存器操作数可以是8位寄存器AH、AL、BH、BL、CH、CL、DH、DL,也可以是16位寄存器AX、BX、CX、DX、SP、BP、SI、DI等。因为寄存器寻址不需要通过总线操作访问存储器,所以指令执行速度比较快。 [11]

寄存器寻址( Register Addressing)是以通用寄存器的内容作为操作数的寻址方式,在该寻址方式下,操作数存放在寄存器中。寄存器寻址方式的寻址对象为:A,B,DPTR,R0~R7。其中,B仅在乘除法指令中为寄存器寻址,在其他指令中为直接寻址。A可以按寄存器寻址又可以直接寻址,直接寻址时写成ACC。 [12]

浙公网安备 33010602011771号

浙公网安备 33010602011771号