存储器 主存 内存条 总线宽度 内存条插槽

[2.5.1]--六管静态MOS管电路(4m32s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re/?p=11&spm_id_from=pageDriver

第二周 主存储器组织

第二周 主存储器组织引言

第1讲 存储器基本概念

第2讲 主存的基本结构

第3讲 主存的性能指标

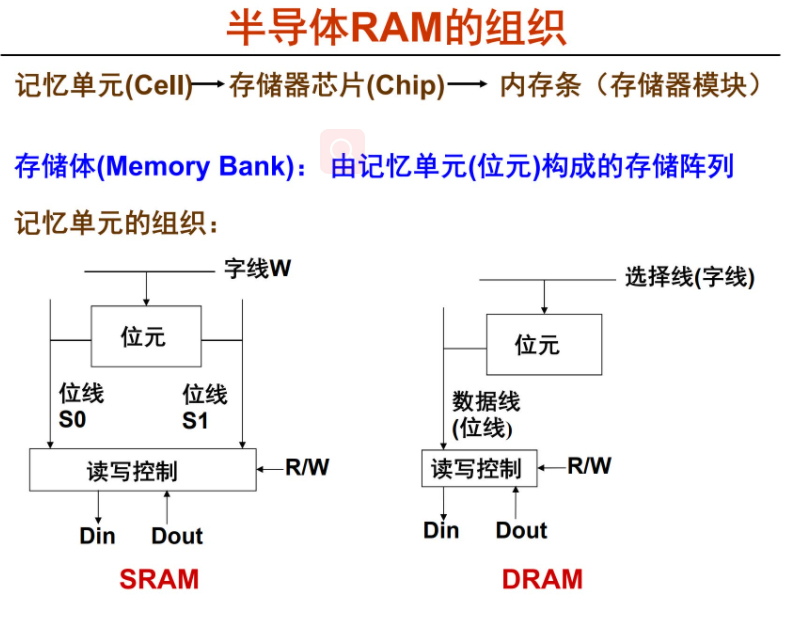

第4讲 半导体存储器组织

第5讲 内存条组织与总线宽度

第6讲 主存模块的连接与读写操作

课件PPT

第二周小测验

基本术语

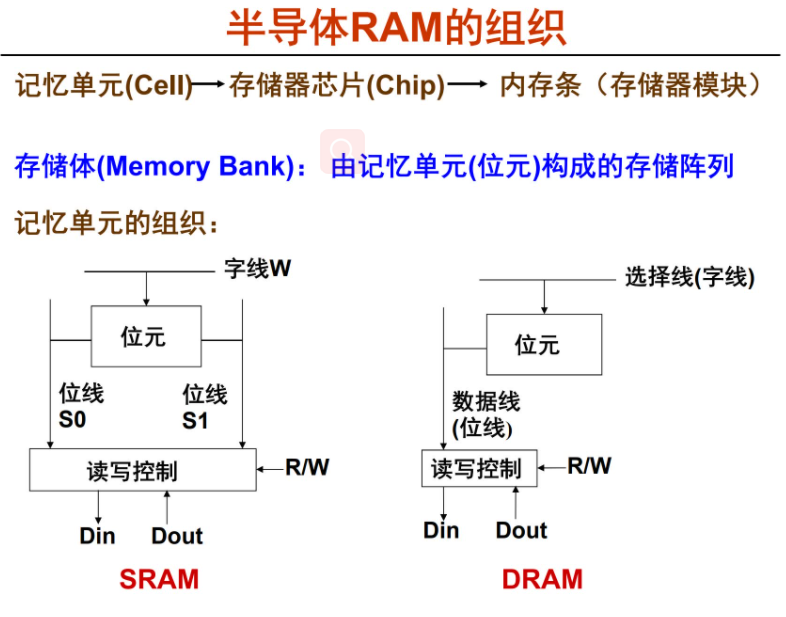

°记忆单元(存储基元/ 存储元/ 位元)(Cell)•具有两种稳态的能够表示二进制数码0和1的物理器件

°存储单元/ 编址单位(Addressing Unit)•具有相同地址的位构成一个存储单元,也称为一个编址单位

°存储体/ 存储矩阵/ 存储阵列(Bank)•所有存储单元构成一个存储阵列°编址方式(Addressing Mode)-字节编址、按字编址

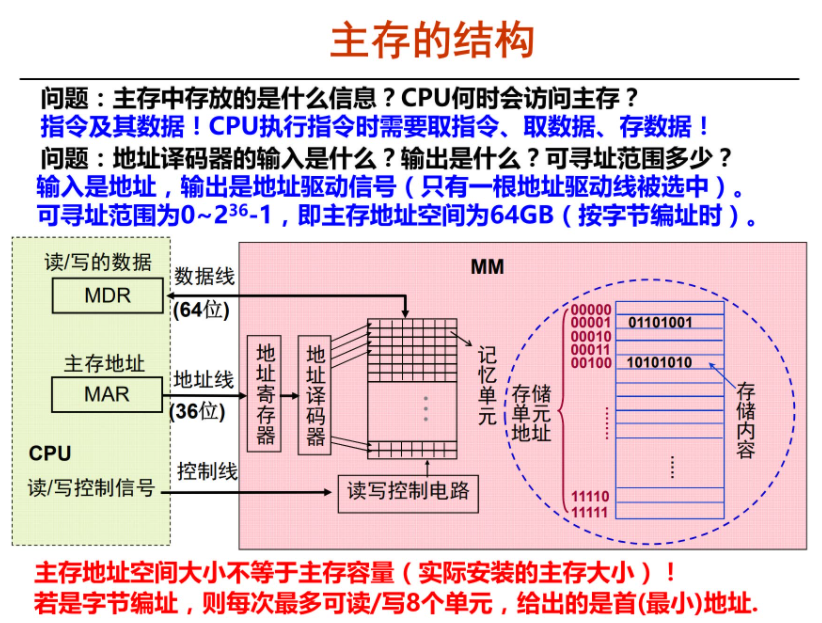

°存储器地址寄存器(Memory Address Register -MAR)•用于存放主存单元地址的寄存器°存储器数据寄存器(Memory Data Register-MDR (或MBR))•用于存放主存单元中的数据的寄存器

存储器分类(

1)按工作性质/存取方式分类

•随机存取存储器RandomAccessMemory(RAM)-每个单元读写时间一样,且与各单元所在位置无关。如:内存。(注:原意主要强调地址译码时间相同。现在的DRAM芯片采用行缓冲,因而可能因为位置不同而使访问时间有所差别。)

•顺序存取存储器SequentialAccessMemory(SAM)-数据按顺序从存储载体的始端读出或写入,因而存取时间的长短与信息所在位置有关。例如:磁带。

•直接存取存储器DirectAccessMemory(DAM)-直接定位到读写数据块,在读写数据块时按顺序进行。如磁盘。•相联存储器AssociateMemory(AM)ContentAddressedMemory(CAM)-按内容检索到存储位置进行读写。例如:快表。

(2)按存储介质分类

半导体存储器:

双极型,静态MOS型,动态MOS型磁表面存储器:磁盘(Disk)、磁带(Tape)

光存储器:CD,CD-ROM,DVD

(3)按信息的可更改性分类

读写存储器(Read / Write Memory):可读可写

只读存储器(Read Only Memory):只能读不能写

(4)按断电后信息的可保存性分类

非易失(不挥发)性存储器(Nonvolatile Memory)

信息可一直保留,不需电源维持。(如:ROM、磁表面存储器、光存储器等)

易失(挥发)性存储器(Volatile Memory)电源关闭时信息自动丢失。(如:RAM、Cache等)

(5)按功能/容量/速度/所在位置分类

•寄存器(Register)-封装在CPU内,用于存放当前正在执行的指令和使用的数据-用触发器实现,速度快,容量小(几~几十个)

•高速缓存(Cache)-位于CPU内部或附近,用来存放当前要执行的局部程序段和数据-用SRAM实现,速度可与CPU匹配,容量小(几MB)

•内存储器MM(主存储器Main(Primary)Memory)-位于CPU之外,用来存放已被启动的程序及所用的数据-用DRAM实现,速度较快,容量较大(几GB)

•外存储器AM(辅助存储器Auxiliary/SecondaryStorage)-位于主机之外,用来存放暂不运行的程序、数据或存档文件-用磁盘、SSD等实现,容量大而速度慢

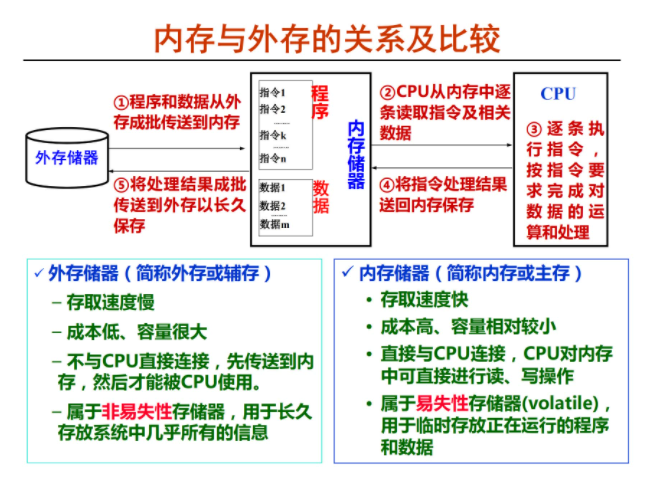

内存与外存的关系及比较

地址寄存器

地址译码器

数据线 地址线 控制线

n位地址线 2^n个存储单元地址

性能指标:

•按字节连续编址,每个存储单元为1个字节(8个二进位)•存储容量:所包含的存储单元的总数(单位:MB或GB)

•存取时间TA:从CPU送出内存单元的地址码开始,到主存读出数据并送到CPU(或者是把CPU数据写入主存)所需要的时间(单位:ns,1ns=10-9s),分读取时间和写入时间

•存储周期TMC:连读两次访问存储器所需的最小时间间隔,它应等于存取时间加上下一次存取开始前所要求的附加时间,因此,TMC比TA大(因为存储器由于读出放大器、驱动电路等都有一段稳定恢复时间,所以读出后不能立即进行下一次访问。)(就像一趟火车运行时间和发车周期是两个不同概念一样。)

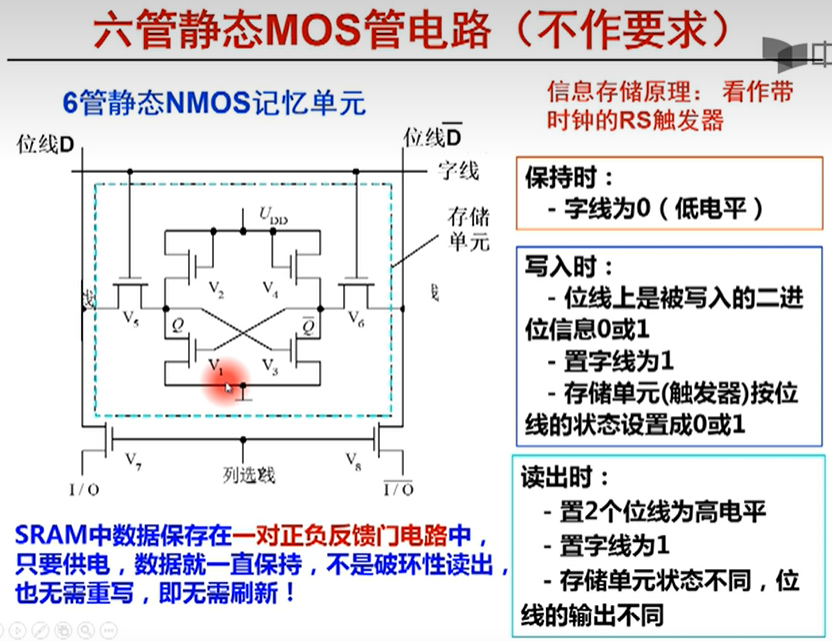

六管静态MOS管电路

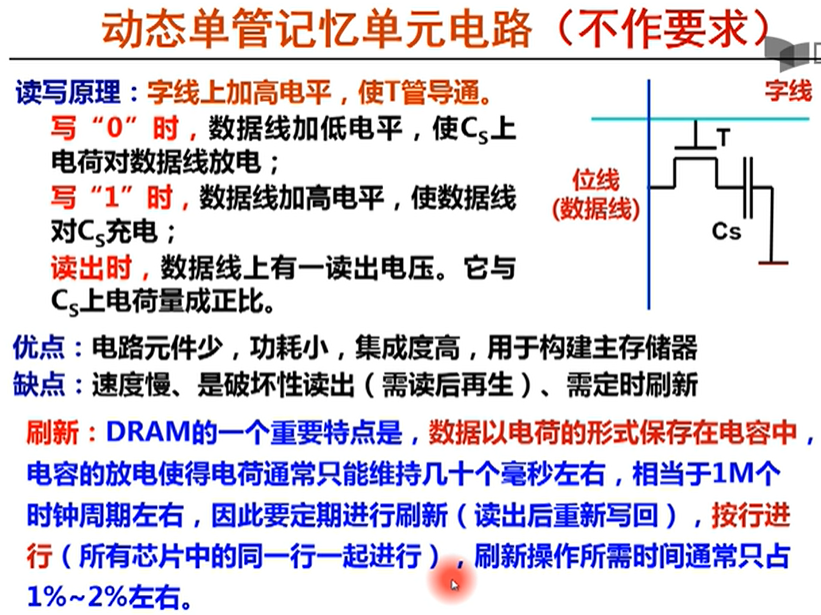

动态单管记忆电路

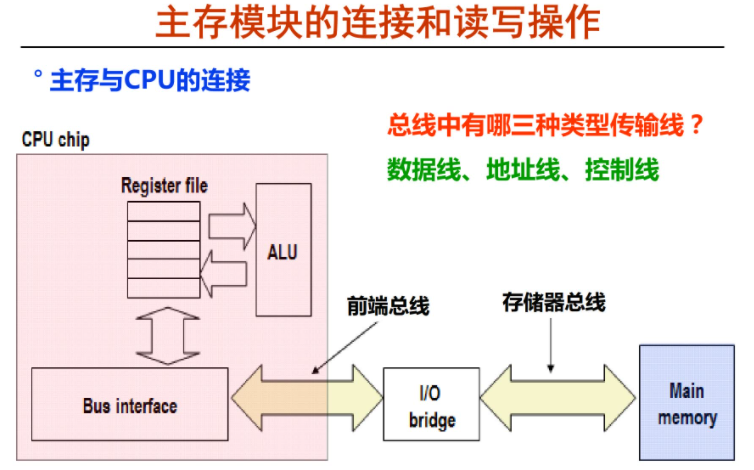

总线中有哪三种类型传输线?数据线、地址线、控制线

[2.6.1]--SPARCstation20的内存条(9m59s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re?p=15

主存与CPU的连接

数据线 地址线 控制线

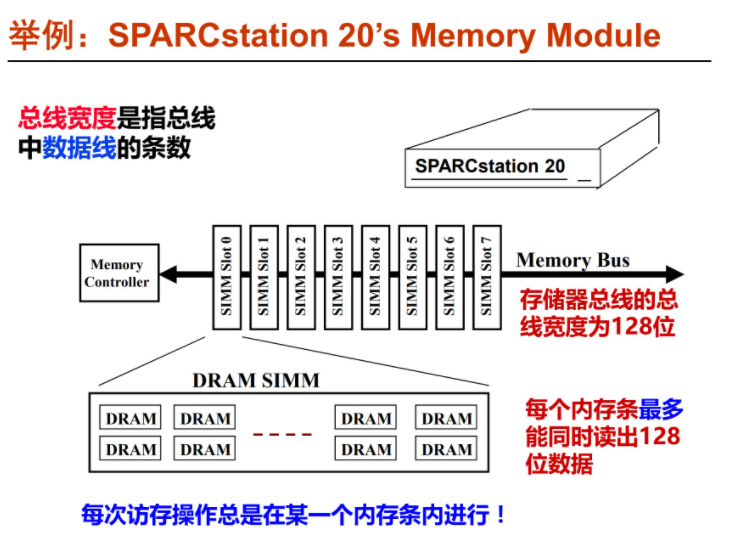

总线宽度是指总线中数据线的条数

总线宽度

每次访存操作总是在某一个内存条内进行!

内存条插槽

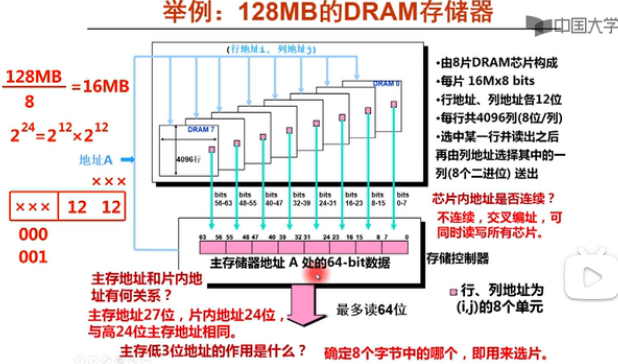

芯片行 列 位平面

芯片内地址 不连续

[2.6.2]--PC中的内存条(4m18s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re?p=16

[2.6.3]--内存条与CPU的连接(6m24s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re?p=17

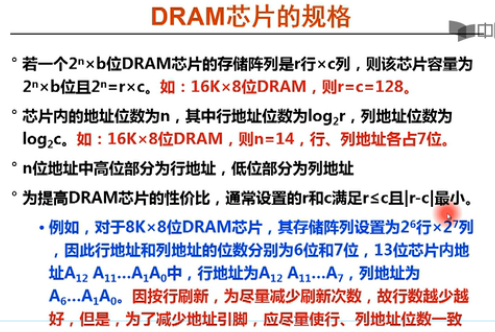

DRAM芯片规格

引脚数 行数 列数

[2.7.1]--主存模块的连接与读写操作(4m08s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re?p=18

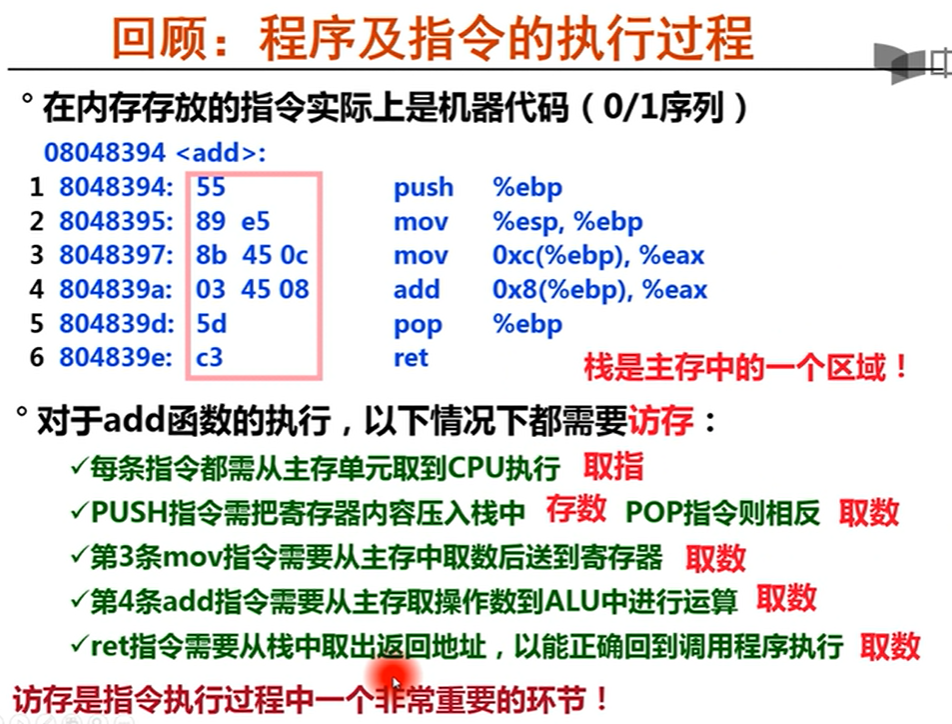

指令 movl 8(%ebp),%eax

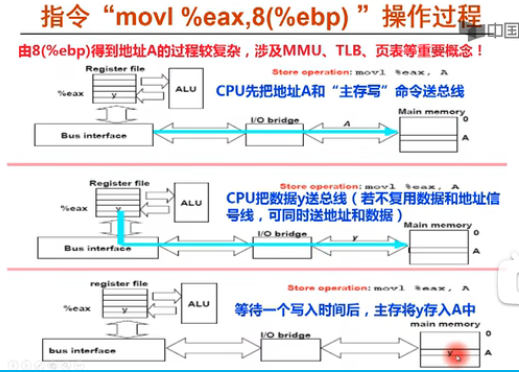

指令 movl %eax,8(%ebp) 操作过程

[2.7.1]--主存模块的连接与读写操作(4m08s)_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1rE41127Re?p=18

浙公网安备 33010602011771号

浙公网安备 33010602011771号