3.6 基于硬件的前瞻执行

3.6 基于硬件的前瞻执行

Tomasulo算法通过寄存器重命名、设置预留站和使用公共数据总线等方式,优化指令的并行执行,能够处理数据依赖,但在处理控制依赖时存在局限。如果存在分支带来的控制依赖,Tomasulo算法需要等待分支指令的执行结果,(或者不等待,但可能导致中断的不精确,乱序执行本身就会导致中断不精确,要实现完全的精确,就需要额外的机制辅助)。

硬件前瞻技术可以通过分析和预测指令的执行结果,提前执行那些有用的指令,从而减少处理器的空闲时间,并提高整体性能,弥补Tomasulo算法(和Scoreboarding)的不足。

硬件前瞻技术主要基于三点重要思想:

-

动态分支预测用于选择执行哪些指令

-

推测允许在控制依赖项解决之前执行指令(具有撤销错误推测序列的影响的能力)

-

进行动态调度,以应对基本块不同组合方式的调度(意思是硬件前瞻能够跨越基本块的边界进行调度,没有硬件前瞻的动态调度只能在基本块内部进行部分重叠的调度,因为它需要在实际执行后续基本块中的任何指令之前先解析分支指令。基本块是指程序中单入口单出口的代码块,可以理解为for循环的一块或者if-else的两块)

硬件前瞻根据预测来选择何时执行指令,一旦操作数可用就立刻执行计算。为了扩展Tomasulo的算法以支持推测,我们必须将指令结果旁路(这是推测执行指令所需的)与指令的实际完成分开。通过这种分离,我们可以允许一条指令执行并将其结果旁路到其他指令,而不允许该指令执行任何无法撤消的更新,直到我们知道该指令不再具有不确定性。当一条指令确定后再更新寄存器/存储器,这叫做指令提交。

推测后的关键思想是允许指令乱序执行(不用管前面分支指令的结果出来了没有),但强制顺序提交,防止不可挽回的动作(状态更改、触发异常)。因此就引入重排序缓冲(Reorder Buffer, ROB)这个硬件结构。详细可参考不精确中断文章。(Smith 和 Pleszkun, 1985)(注意一下:硬件前瞻技术本身不直接解决中断精确性的问题。硬件前瞻主要用于预测指令的执行结果,并提前执行有用的指令,以提高处理器效率。它更多地关注于指令的执行流程和优化。)

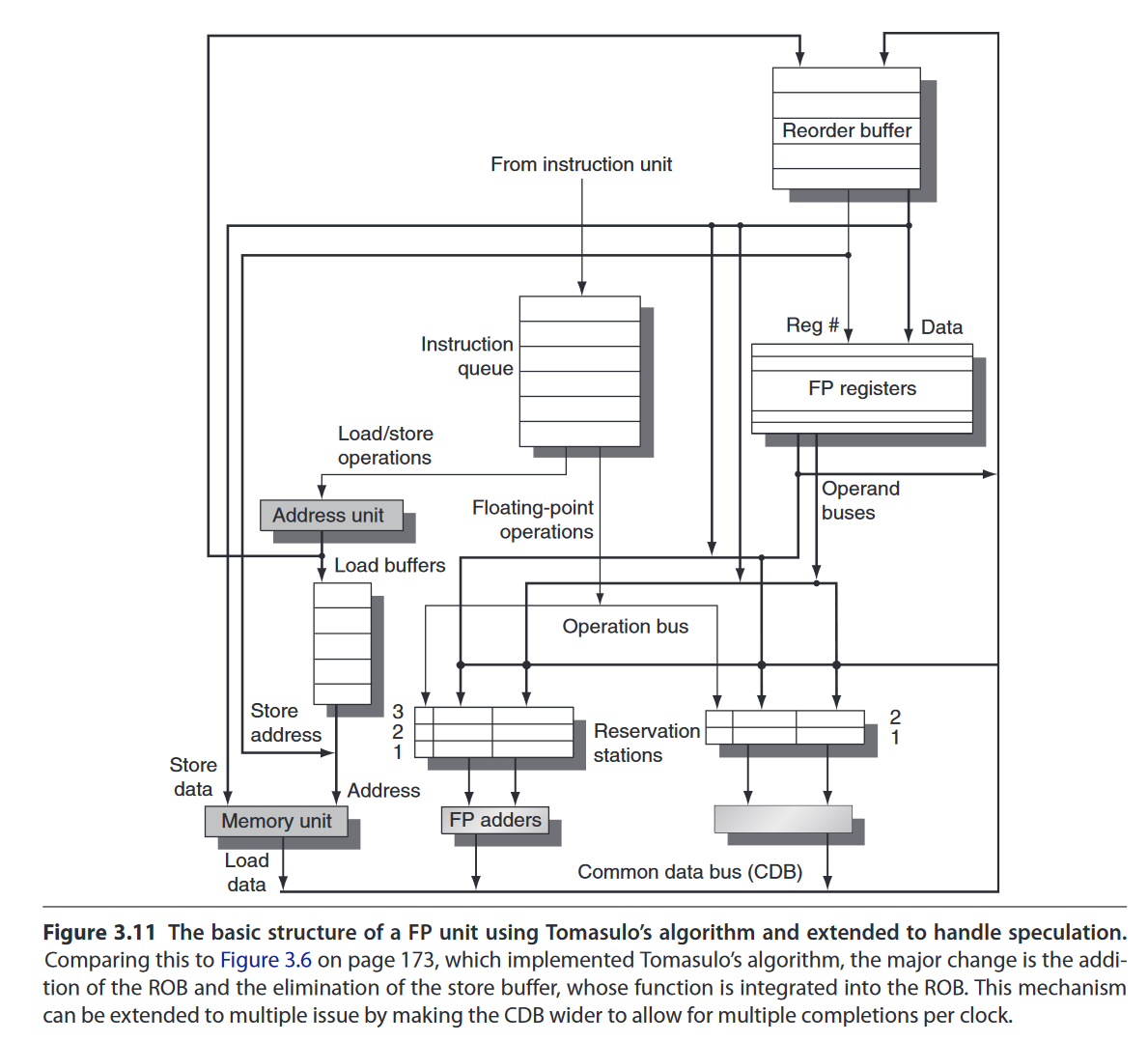

ROB主要包含四个信息:指令类型,目的字段、值字段和就绪,“Figure 3.11” (Hennessy 和 Patterson, p. 185)展示了进行硬件前瞻拓展后的Tomasulo结构,去处理Store Buffer。上往下数据依次从新变旧,因此数据先从ROB拿,没有再找register。拓宽CDB还可以支持多发射。

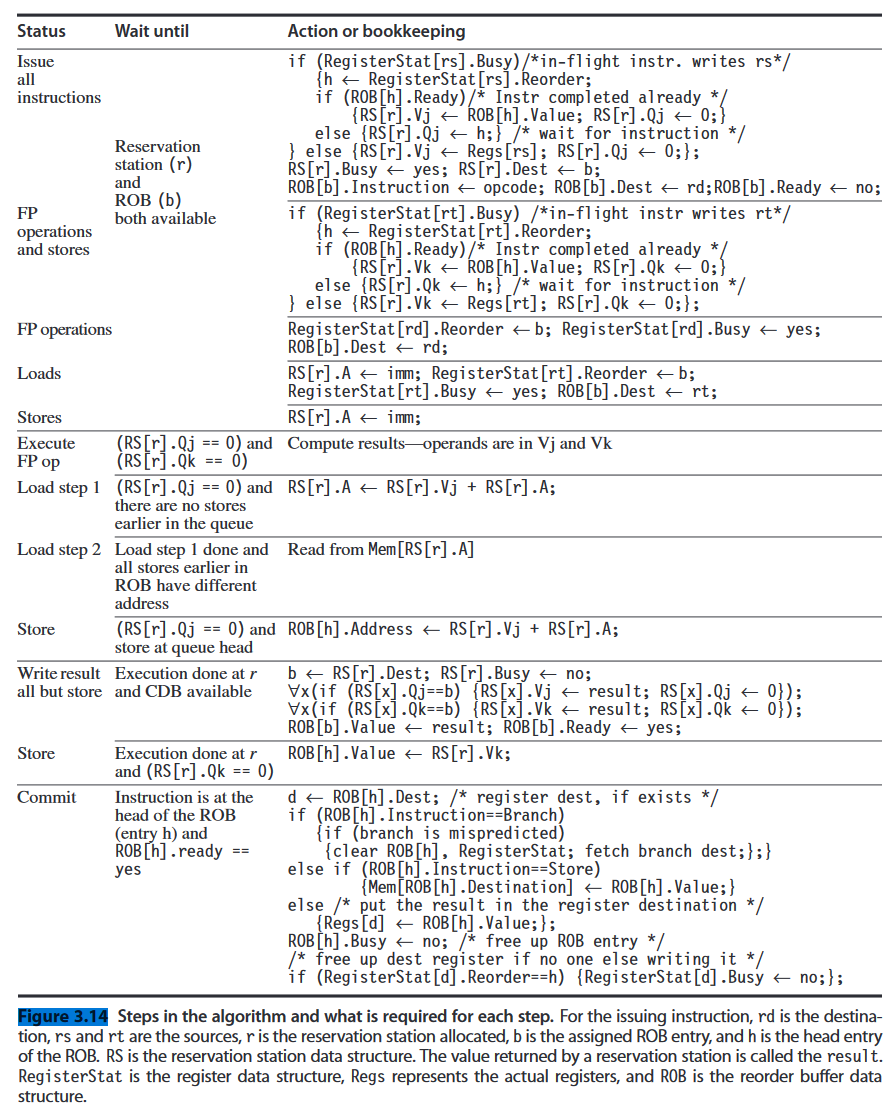

指令执行的4个步骤:

-

Issue:ROB与保留站都有空才发射;

-

Execute:操作数都可用时执行,否则监视CDB,避免RAW;

-

Write Result:将结果与ROB标签写在CDB上,写到ROB与需要的保留站上;对于Store指令,如果要存的值就绪了,就存入,否则监视CDB;

-

Commit:分三种情况,完成后都需要清除ROB对应条目。ROB满了就要停止取指令直到有空。

-

正常提交:当指令到达ROB头部且结果已经写回ROB时,用结果更新寄存器;

-

提交存储指令:类似正常提交,不过更新的是存储器;

-

分支预测错误:ROB被刷新,重新从分支后续正常指令开始执行。

-

“Figure 3.14” (Hennessy 和 Patterson, p. 191)非常重要,具体讲清楚了各种操作。具体不同体现

-

Issue的时候需要多考虑一次ROB中的数据是不是有效的?有效的话直接从ROB里面取(ROB数据比寄存器新);

-

增加了Commit部分的判断;

总而言之,硬件前瞻技术能够带来一下四点好处:

-

提高处理器效率:通过预测指令的执行结果,硬件前瞻技术能够提前执行有用的指令,避免等待无用指令执行完成的时间,从而显著提高处理器的运算效率。

-

优化指令执行顺序:硬件前瞻技术可以分析和预测数据依赖性和控制依赖性,优化指令的执行顺序,使得处理器能够更加高效地利用资源。

-

减少处理器空闲时间:通过提前执行有用的指令,硬件前瞻技术减少了处理器的空闲时间,从而提高了处理器的整体性能。

-

支持更复杂的任务处理:硬件前瞻技术能够处理复杂的数据依赖和控制依赖场景,使得处理器能够更高效地处理复杂任务,满足不断增长的计算需求。

浙公网安备 33010602011771号

浙公网安备 33010602011771号