3.5 动态调度的例子与算法

3.5 动态调度的例子与算法

Tomasulo算法优势

-

分布式危险检测逻辑。分布式保留站和CDB实现,如果多个指令正在等待单个结果,并且每个指令已经有了它的其他操作数,那么可以通过在CDB上广播结果来同时释放这些指令。如果使用集中式寄存器文件,当寄存器总线可用时,这些单元必须从寄存器中读取它们的结果。

-

消除了WAW和WAR的延迟。重命名寄存器以及在操作数可用时将其存储到预订站。

Tomasulo算法细节

-

Load和Store先要通过功能单元进行地址计算,再将操作放入独立的Load和Store Buffer中。

-

Load指令在第二个执行步骤访存,并将结果写回寄存器并广播在CDB中发送给保留站。

-

Store指令在写回阶段完成。无论目标是寄存器还是内存,所有写操作都发生在写结果中,这一限制简化了Tomasulo算法。

-

如果操作数在寄存器中可用,则将它们存储在V字段中。否则,将Q字段设置为指示将生成作为源操作数所需值的保留站。

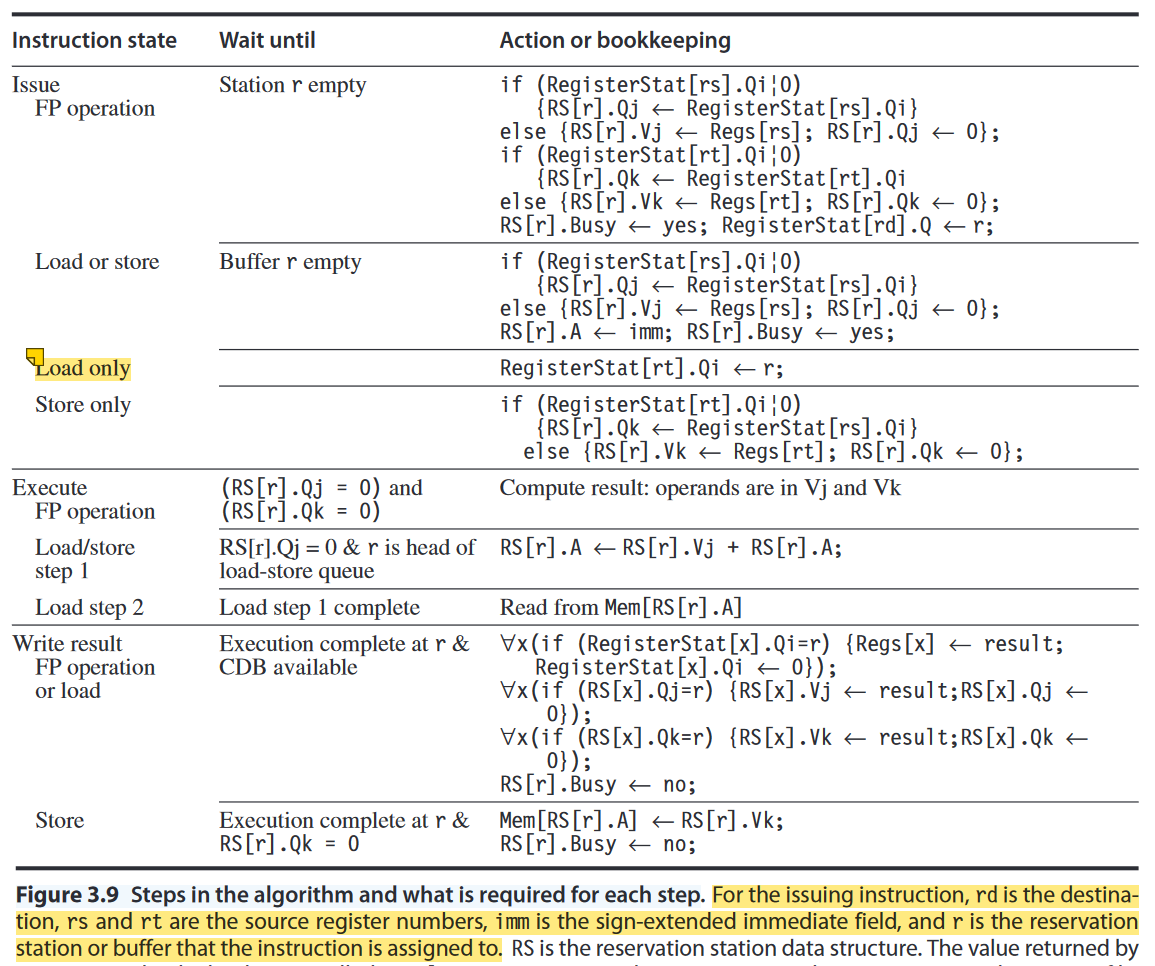

“Figure 3.9 Steps in the algorithm and what is required for each step” (Hennessy 和 Patterson, p. 180)很重要,分析可以得到一下信息:

-

Issue阶段FP操作,当保留站有空的时候就可以发射;如果寄存器状态表中rs寄存器的项目不为零,则表示前面有指令要写rs寄存器,所以把保留站的Qj指向写rs的指令,否则从寄存器中取数,rt同理;同时设busy,更新寄存器状态表。

-

Issue阶段Load&Store操作,当Buffer有空的时候就能发射,与FP类似;先算rs得到地址,再用rt存/取数据,所以要先确定rs非空。对于Load还需要更新寄存器状态表,rt是写入,就不用管了,不过对于Store还需要判断rt(源数据);

-

Execute阶段,对于FP操作,两个操作数都准备好了就执行;对于Load&Store阶段1,只要Qj为零就表示地址计算已经就绪了,开始算地址;Load一阶段完成后随机进入二阶段访存取数。

-

Write Result阶段,对于FP或Load,相当于得到结果了,所以只要计算完成且CDB空闲就可以。此时判断寄存器、保留站是否需要该数据,并释放占用。如果寄存器状态表中仍有该数据,说明没有WAW,所以要写进寄存器中,否则不写寄存器了。

-

Write Result阶段,对于Store,相当于把源数据存进内存的目的地址,所以只要算完地址且得到了源数据就可以执行,此时进入Store Buffer,并释放占用。

Tomasulo执行循环的例子

在Tomasulo的方案中,结合了两种不同的技术:将体系结构寄存器重命名为更大的寄存器集,以及缓冲来自寄存器文件的源操作数。

-

尽管Tomasulo的算法是在缓存之前设计的,但缓存的存在,以及固有的不可预测的延迟,已经成为动态调度的主要动机之一。乱序执行允许处理器在等待缓存丢失完成的同时继续执行指令,从而隐藏了全部或部分缓存丢失惩罚。

-

随着处理器的问题处理能力越来越强,设计人员越来越关注难以调度的代码(如大多数非数字代码)的性能,寄存器重命名、动态调度和推测等技术变得更加重要。

-

它可以实现高性能,而不需要编译器将代码定位到特定的管道结构,这在收缩包装的大众市场软件时代是一个有价值的属性。

浙公网安备 33010602011771号

浙公网安备 33010602011771号