汇编语言简易教程(2): 计算机体系概览

汇编语言简易教程(2): 计算机体系概览

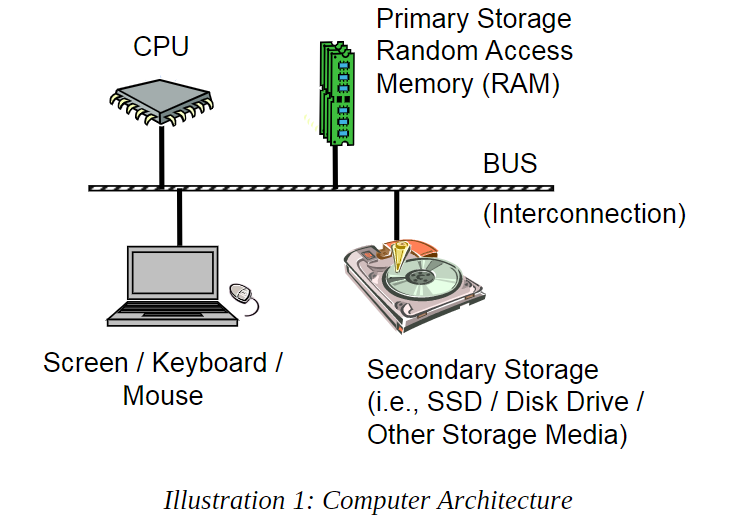

架构

- CPU

- RAM

- BUS

- DEVICE

- Secondary Storage (SSD / Disk Drive)

通常来说程序被存储在硬盘中, 在实际需要运行时从硬盘加载到内存.

主存通常来说是易失性存储, 所以在断电时, 存储内容会丢失. 二级内存通常是不易失的, 对于断电等行为有一定的抗性.

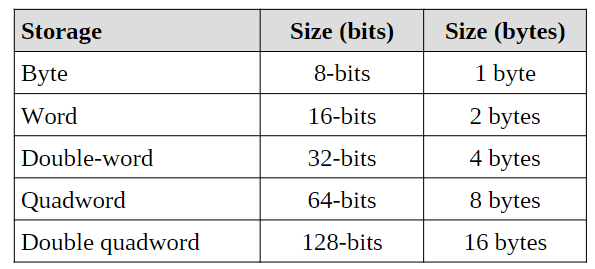

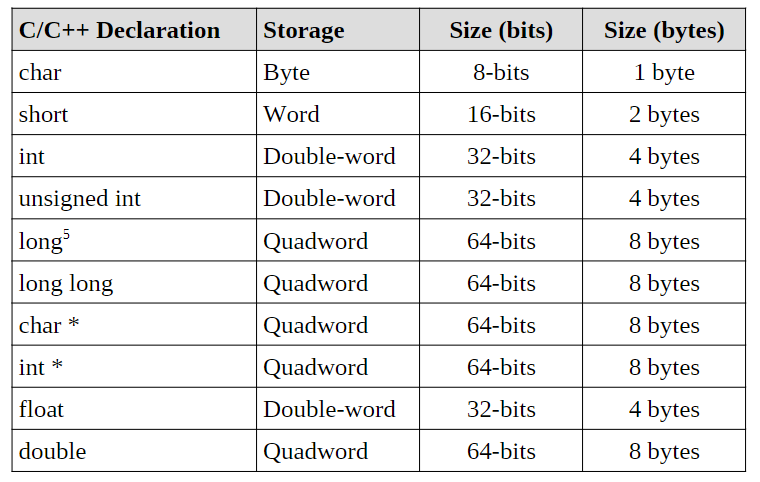

数据存储大小

CPU组成

算术逻辑单元 (ALU), 算术以及逻辑运算

寄存器

通用寄存器概览

组成

一个寄存器可能会有多个名字, 真正影响的是操作位置

左高右低

栈帧寄存器 (RSP)

One of the CPU registers, rsp, is used to point to the current top of the stack. The rspregister should not be used for data or other use

用于存储当前栈顶指针, 不应该用于存储数据或其他使用.

基址寄存器 (RBP)

One of the CPU registers, rbp, is used as a base pointer during function calls. The rbpregister should not be used for data or other uses

用于在函数调用期间存储基址指针, 不应该用于存储数据或其他使用.

指令寄存器 (RIP)

In addition to the GPRs, there is a special register, rip, which is used by the CPU topoint to the next instruction to be executed. Specifically, since the rip points to thenext instruction, that means the instruction being pointed to by rip, and shown in thedebugger, has not yet been executed

用来指向下一条要执行的指令, 需要注意此时尚未开始执行.

标志寄存器 (rFlags)

一个示例: CMPXCHG

标志寄存器 rFlags 用于状态和 CPU 控制信息.

rFlag 寄存器在每条指令后由 CPU 更新,并且不能由程序直接访问。

该寄存器存储有关刚刚执行的指令的状态信息。 rFlag 寄存器中的 64 位中,许多保留供将来使用

常见的标志寄存器

名称 符号表示 bit位 用途 Carry CF 0 用于指示前一个操作是否产生进位 Parity PF 2 用于指示最后一个字节是否有偶数个1 Adjust AF 4 用于支持二进制编码的十进制运算 Zero ZF 6 用于指示先前操作是否导致结果为零 CMPXCHG Sign SF 7 用于指示前一操作的结果是否在最高有效位中产生 1(在有符号数据的上下文中指示负数) Direction DF 10 用于指定某些字符串操作的方向(递增或递减) Overflow OF 11 用于指示之前的操作是否导致溢出 XMM 寄存器

专用寄存器用于支持 64 位和 32 位浮点运算以及单指令多数据 (SIMD) 指令。

SIMD 指令允许将单个指令同时应用于多个数据项。有效地使用,可以显着提高性能。典型应用包括一些图形处理和数字信号处理

根本原因是: 一个像素点的颜色的一个分量是通过8bit来操作的, 如果直接使用通用寄存器来处理的话, 会有比较大的浪费.

可以参考下图:

将一个128bit的寄存器, 按照8bit一组的方式分成了16组.

请注意,一些较新的 X86-64 处理器支持 256 位 XMM 寄存器

SP

Cache

通常来说是主存的子集, 位于CPU中

如果一个主存位置被访问, cache中会存储这个值的拷贝.

快速连续发生的对该内存位置的后续访问将从高速缓存位置(CPU 芯片内部)的查找。

内存读取涉及通过总线将地址发送到内存控制器,内存控制器将获取所请求内存位置的值,然后通过总线将其发送回。相比之下,如果某个值在缓存中,则访问该值会快得多

当可以在缓存中找到所请求的数据时,发生缓存命中,而当无法在缓存中找到时,发生缓存未命中。

高速缓存命中是通过从高速缓存读取数据来实现的,这比从主内存读取数据要快。

缓存可以处理的请求越多,系统通常执行的速度就越快。

历代CPU芯片都增加了高速缓存并改进了高速缓存映射策略,以提高整体性能

一个典型的CPU cache架构如下图所示:

目前的芯片设计通常包括每个核心一个 L1 高速缓存和一个共享的 L2 高速缓存。

许多较新的 CPU 芯片将有一个额外的 L3 高速缓存.

从图中可以看出,所有内存访问都会经过每一级缓存。

因此,可能存在该值的多个重复副本(CPU 寄存器、L1 缓存、L2 缓存和主内存)。

主存

主存可以被看做是连续的字节.

主存是可以定位的 (如同数组可以通过下标定位一样)

另外需要注意: 其架构是小端序, 这意味着最低有效字节(LSB)存储在最低的内存地址中。最高有效字节 (MSB) 存储在最高内存位置。

我们以 5,000,000 (0x004C4B4016) 举例

可以参考: 编码序

通常来说在网络传输中使用的是大端序

在内存中运行时是小端序.

程序的内存布局

- 保留部分对用户程序不可用

- 文本段/代码段 是用来存储机器码的位置

- 数据段用来存储初始化数据

- BSS: 存储未提供初始值的已声明变量的位置。如果在设置之前访问,该值将没有意义。

- 堆是存储动态分配的数据的位置(如果需要)。

- 堆栈从高内存开始并向下增长

计算机存储结构

存储金字塔

典型的存储金字塔如上所示

越在顶端的存储速度越快, 价格越高, 容量越小

在底层的存储通常来说能够在相同的价格上提供数量级的存储容量提升, 以及数量级的慢速.

典型速度

- 寄存器, 大小通常是64bit, 速度在1 ns 以内

- CPU Cache, 大小一般在MB左右, 访问速度在50-60 ns

- 主存, 一般在GB数量级, 访问速度在 100 - 150 ns

- 次级存储/硬盘存储, TB量级, 3 - 15ms