每个程序员都应该了解的内存知识(二): CPU Cache

CPU Cache

架构

每个程序员都应该了解的内存知识.pdf - p22 - 每个程序员都应该了解的内存知识-P22-20240328112647

每个程序员都应该了解的内存知识.pdf - p23 - 每个程序员都应该了解的内存知识-P23-20240328112807

每个程序员都应该了解的内存知识.pdf - p23 - 每个程序员都应该了解的内存知识-P23-20240328112841

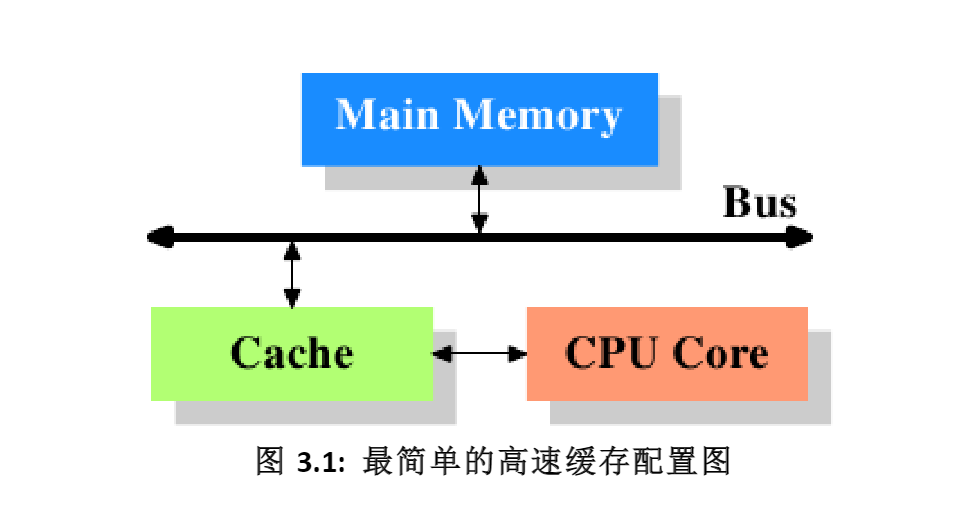

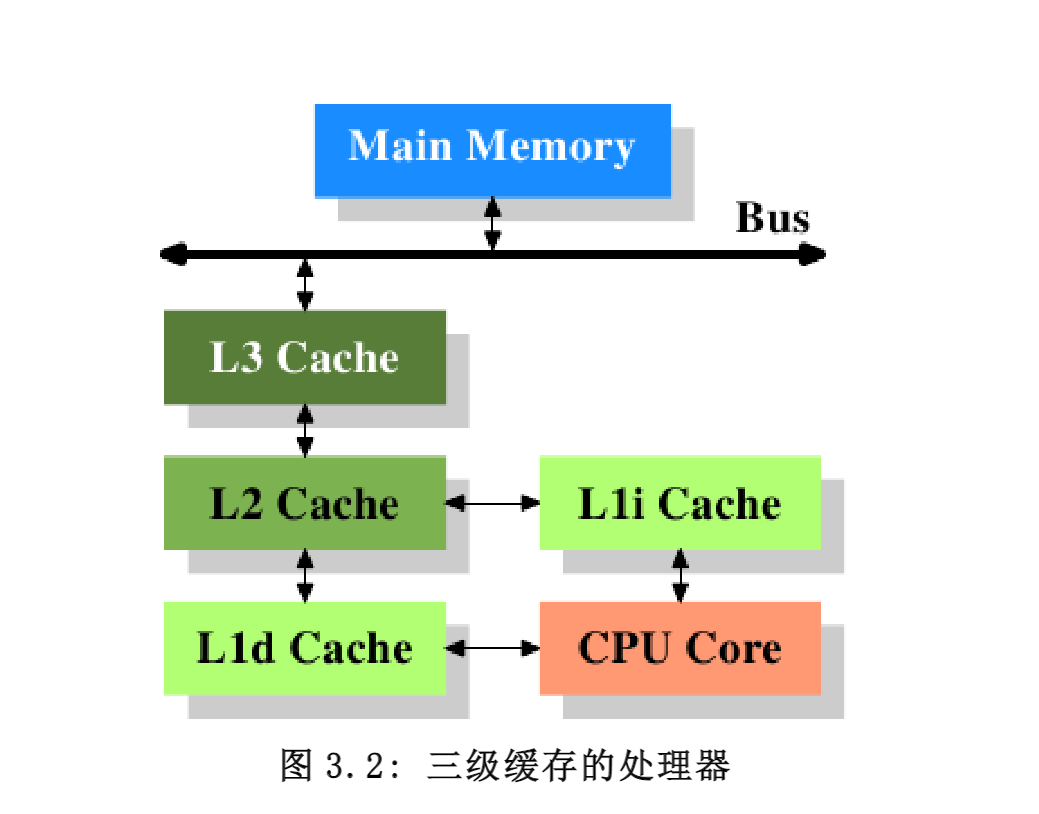

cpu core -> l1 cache -> l2 cache -> l3 cache -> main memory

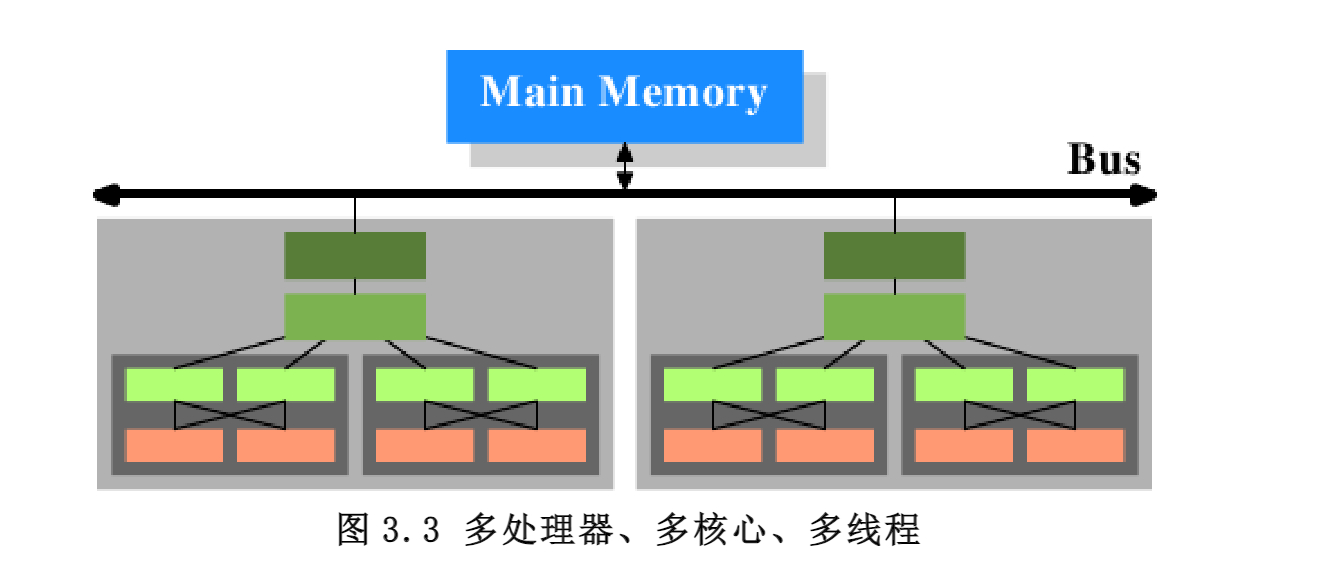

- L1缓存:几乎所有的现代多核CPU都会为每个核心提供独立的L1缓存,这是因为L1缓存设计用于提供极低的访问延迟。每个核心的L1缓存通常分为两部分:L1数据缓存(L1-D)和L1指令缓存(L1-I)。

- L2缓存:多核处理器中的L2缓存可能是每个核心独立的,也可能是部分或完全共享的。这取决于具体的CPU设计和制造商。共享L2缓存可以提高多核心之间的数据共享效率,但也可能增加核心之间的竞争。

- L3缓存:许多现代多核处理器都采用了共享的L3缓存,它是位于CPU核心和主内存之间的最后一级缓存。共享L3缓存可以大幅度提高不同核心之间的数据共享效率和降低访问主内存的延迟。所有核心都可以访问这个缓存层次来检索数据。

缓存操作

- 一个脏缓存线不存在于任何其他处理器的缓存之中。

- 同一缓存线中的干净拷贝可以驻留在任意多个其他缓存之中

BTW, 这也会直接影响到程序的设计, 例如经典的 volatile 关键字, 其实就会涉及到cpu cache的使用位置, 即此变量每次都从内存中获取, 而不是直接使用cache中的数据.

缓存写入策略

写通(write-through)

写通比较简单。当修改缓存线时,处理器立即将它写入主存。这样可以保证主存与缓存的内容永远保持一致。当缓存线被替代时,只需要简单地将它丢弃即可。这种策略很简单,但是速度比较慢。如果某个程序反复修改一个本地变量,可能导致 FSB 上产生大量数据流,而不管这个变量是不是有人在用,或者是不是短期变量.

写回(write-back)

写回比较复杂。当修改缓存线时,处理器不再马上将它写入主存,而是打上已弄脏(dirty)的标记。当以后某个时间点缓存线被丢弃时,这个已弄脏标记会通知处理器把数据写回到主存中,而不是简单地扔掉。