|

一、硬件概述

DBF技术的实现全部是在数字域实现,然而天线阵列接收的信号经过多次混频后得到的中频信号是模拟信号,实现DBF处理并充分发挥DBF技术优势的关键技术一直就是要设计高性能高速模数变换(ADC)阵列,完成模拟信号到数字信号的转换,同时需要高性能数字信号处理硬件平台实现同时多波束形成、实时自适应权重系数计算。

一般的数字阵列雷达系统由天线阵列、数字T/R组件、频综、自适应DBF处理器、雷达信号处理器等5个部分组成。本文使用DBF技术的数字阵列雷达为项目背景,结合高速多通道采样软件无线电技术,设计了一款数字阵列雷达多通道中频信号采集和DBF电路,并在该硬件平台上实现中频软件无线电W及同时多波束数字波束形成功能。该电路具有采样率高、通道数目多、信号处理能力强,对软件无线电技术和DBF技术的实现和工程应用具有现实意义。

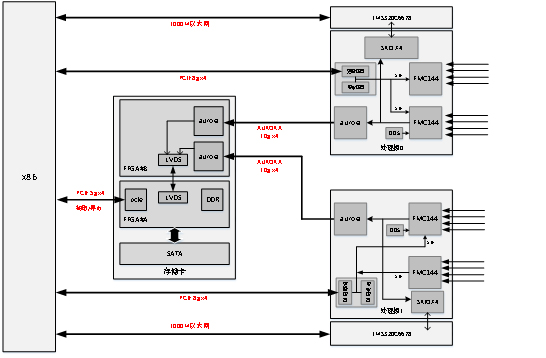

该电路具体实现基于6U VPX机箱,集成4块6U VPX信号预处理卡 ,每块板卡集成16路250Msps采样AD,一共64路AD,实现同源同频,同步触发采集,每块卡通过RapidIOX4 把数据汇总到6U VPX信号处理板卡。6U VPX卡由高性能的XC7V690T+C6678 构成,板卡上同时集成双FMC,扣AD子卡,实现信号的输出验证。

整机系统基于6U VPX架构,为一套整机设备系统原理框图如下所示:

二、硬件内容

2.1.基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡

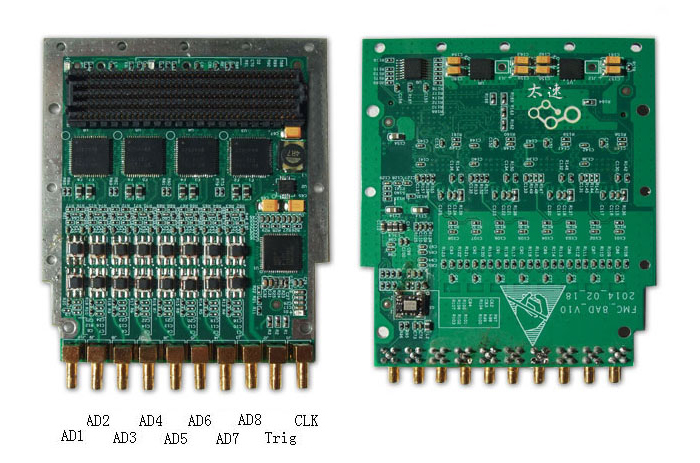

2.2、FMC144 -八路 250MSPS 14bit AD FMC子卡

2.3. 硬件互联关系

三.软件设计架构

3.1.管理流

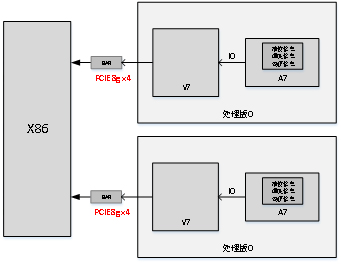

管理流主要是X86与处理版之间的信息交互,主要是X86对槽位对应板卡的信息管理和处理版温度及资源信息的监控;

对于槽位的区分管理,处理板和机箱都在硬件上已经具备了这一功能,而处理卡需要做的就是将A7 IO口所得到的插槽信息,通过V7 PCIE上传到X86,所以在系统运行开始,需要将这一流程实现。同样通过V7更新BAR空间指定寄存器即可。我们知道上位机区分不同PCIE是通过配置PCIE时配置成不同的设备ID,所以X86上位机通过固定ID的PCIE接收到对应处理卡V7对寄存器所更新的信息,即可知道PCIE ID所对应的板卡槽位信息。

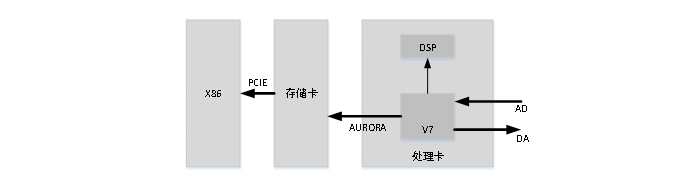

3.2.数据流

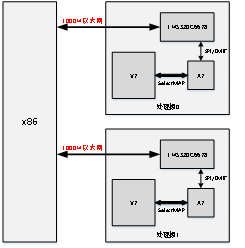

3.3.加载流

加载流主要是完成处理卡FPGA的在线重加载,目前基于9号处理卡的动态重加载已经实现,bit流数据通过emif传输到处理卡上的A7,A7通过SelectMAP对V7进行动态重加载。

针对动态重加载对PCIE功能的影响,也做了相应的测试,证实重加载会对PCIE的使用产生直接影响,重加载完成后必须重新启动X86设备,才能重新正确使用PCIE。

这里X86通过1000M网对DSP的控制由甲方自行开发。

3.4.上位机界面设计方案

|

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

2020-04-23 信号处理板学习资料:基于6UVPX C6678+XCVU9P的信号处理板卡440