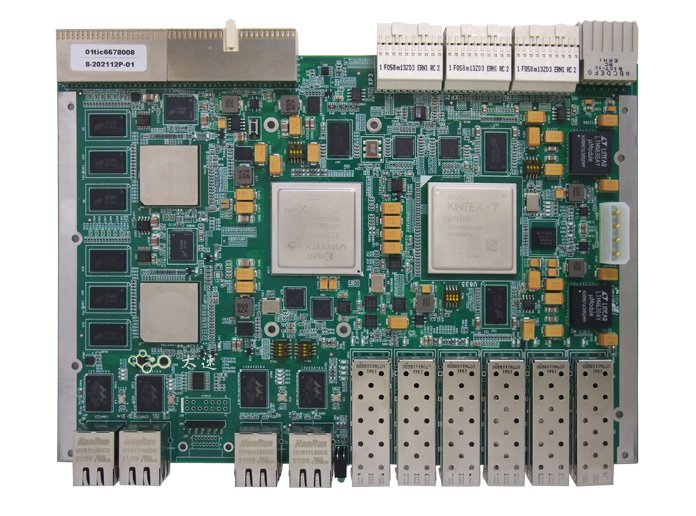

1、板卡概述

板卡由我公司自主研发,基于6UCPCI架构,处理板包含双片TI DSP TMS320C6678芯片;一片Xilinx公司FPGA XC7K420T-1FFG1156 芯片;六个千兆网口(FPGA两个,DSP四个);DSP与FPGA之间 RapidIOX4互联, DSP 之间 Hyperlink X4 互联;FPGA 提供12个GTX连于背板(GTX支持6.25Gbps的传输频率);每颗DSP外接1GB的DDR3,64bit位宽,32MB Nor Flash;FPGA 外接2组DDR3,各512MB,64bit位宽,32MB Nor Flash;通过PCIe桥连接DSP的PCIe和FPGA的PCIe口,PCIe对外X4模式;FPGA连接不少于160根普通IO到CPCIe的P4,P5连接器。

2、处理板技术指标

- 板卡要求采用双片TI DSP TMS320C6678芯片,8核,主频1G。

- 板卡采用Xilinx公司FPGA XC7K420T-1FFG1156 芯片。

- 前面板 两个DSP各出一个千兆网口,另外2个网络连于背板。

- 前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps

- 前面板出4个指示灯,1个复位按钮。

- DSP与FPGA之间 RapidIOX4互联,DSP的Uart,SPI,I2C连接于FPGA。

- DSP 之间 Hyperlink X4 互联。

- FPGA 提供12个GTX连于背板,支持4个X2,1个X4的工作模式配置。GTX

高工作频率为6.25Gbps。 高工作频率为6.25Gbps。

- 每颗DSP外接1GB的DDR3,64bit位宽;32MB Nor Flash.

- FPGA 外接2组DDR3,各512MB,64bit位宽,32MB Nor Flash,在原理图设计阶段,如FPGA的I/O引脚资源不够,则可将DDR3位宽调整为32BIT宽。

- DSP 支持远程网络加载,PCIe加载;FPGA支持Master SelectMAP和Master BPI加载,同时支持DSP0或者DSP1的SPI口对FPGA进行动态加载和对配置芯片程序更新。

- FPGA连接不少于160根普通IO到CPCIe的P4,P5连接器。

- FPGA能读取背板槽位信息,ID[3:0]。

- FPGA 外接E2PROM。

- 板卡芯片要求工业级。

- 供电 采用 +5V +12V 双电源。

- 板卡结构标准CPCIe 6U大小。

- 整板冷却,支持加固。

3、软件系统

3.1 DSP底层软件包括

(1)DSP的DDR3测试程序;

(2)DSP的Nor Flash 擦写程序;

(3)DSP的网络接口测试,SGMII互传程序;

(4)DSP的HyperLink互连传输程序;

(5) DSP的SPI接口程序;

(6)DSP的I2C E2PROM操作程序;

(7)DSP的RapidIO接口驱动程序;

(8)DSP的Boot Load引导程序;

(9)DSP的多核加载测试程序;

(10)DSP的网络加载程序;

(10)DSP的GPIO中断服务测试程序;

(11) DSP对 FPGA的动态加载和配置程序更新程序;

3.2 FPGA底层软件包括

(1)FPGA的DDR3驱动接口程序;

(2)FPGA的网络接口驱动程序;

(3)FPGA的 Nor Flash接口驱动程序;

(4)FPGA与DSP的RapidIO驱动程序;

(5)与背板互连DSP板卡的GTX传输程序;

(6) FPGA的光纤接口驱动程序;

(7) 配置FPGA的控制程序;

(8) 从FPGA的电源管理,复位管理,配置管理程序;

4、物理特性:

尺寸:6U CPCIe板卡,大小为160X233.35mm。

工作温度:0℃~ +55℃ ,支持工业级 -40℃~ +85℃

工作湿度:10%~80%

5、供电要求:

双直流电源供电。整板功耗 50W。

电压:+5V 5A ,+3.3V 6A。

纹波:≤10%

|

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· 【自荐】一款简洁、开源的在线白板工具 Drawnix