超前进位加法器原理详解

对于波纹进位加法器(亦称脉动进位加法器,ripple-carry adder)来说,如果增加运算位数,一方面需要更多的逻辑门,另一方面由于高位的计算必须等待低位的进位输出信号被计算出来才能开始,在进行大规模数据计算时会显著增加运算时间。

所以,当今的计算机使用的是另一种有些不同的加法运算器:超前进位加法器('carry-look-ahead' adder)。

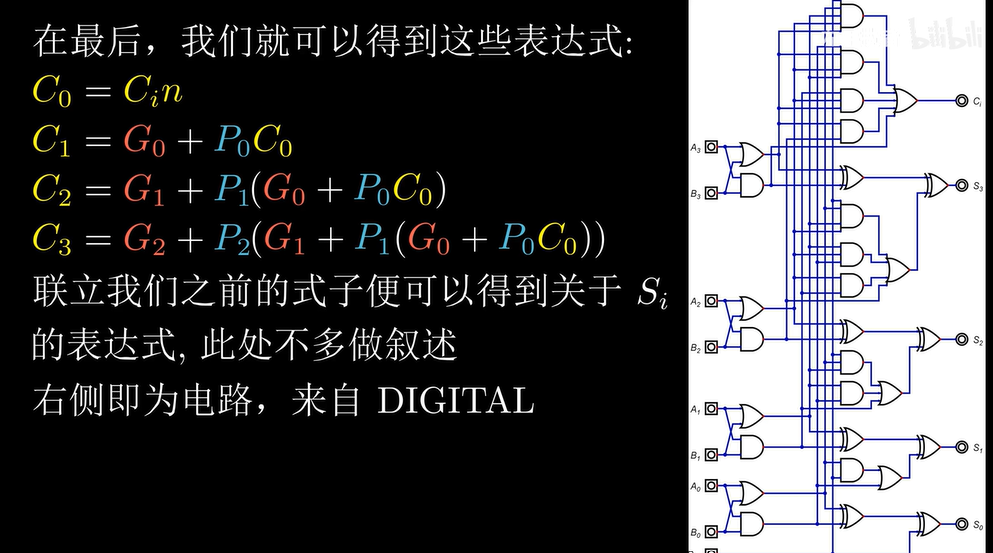

总结:超前进位加法器的原理是数学公式推导所得到的结果。通过将输出在高位的进位利用输入的低位去表示,实现效率的提升。

下面来看超前进位加法器的具体原理。

Ai、Bi为两个输入在第i位的值,Ci(carry)代表该位向下一位的进位,Si(sum)代表该位的和。

在布尔代数中,点乘是“与”,加法是“或”,右上小撇代表“非”,⊕代表异或运算。

两数相乘(“与”)如果有一个是0,则结果一定为0,亦知只有两个乘数都是1时才能得1。

两数相加(“或”),只要有一个不是0,则得数为1。注意1+1=1。

在异或运算中,1⊕1=0,0⊕0=0,1⊕0=1。

为什么 Si=Ai⊕Bi⊕Ci ?为什么用“异或”运算去表示S?

由二进制算术(非逻辑)可知,1+1=10,1+0=1,0+0=0。

可以发现,二进制算术加法所得结果在个位上的数字与逻辑运算中“异或”的结果是相同的。

M⊕N为什么等于(MN)⊕M+N?

若M⊕N为true,则M、N不相同。

则此时(MN),即M和N求逻辑“与”运算应当为false;(M+N)应当为true。则(MN)⊕M+N为true,与M⊕N结果相同。

由于高位的进位输出表达式(积之和式)涉及的变量更多,对应的逻辑电路连线会变得更复杂,而且在实际应用中会遭遇逻辑门的扇入问题。

所以出于对成本的考虑,有必要对位数过高的全加器进行逻辑划分,如将六十四位全加器分为四个十六位超前进位加法器来实现,以此来实现成本和性能的平衡。

参考:

浙公网安备 33010602011771号

浙公网安备 33010602011771号