虚拟内存(Virtual Memory)

Each process has its own virtual address space, so the virtual address 0xdead0000 in one process's address space will represent a different physical page than the page represented by 0xdead0000 in another process. Each process has it's own mapping from virtual addresses to physical addresses, virtual addresses are often reused between processes.

| Basic Paramaters | |

| Symbol | Description |

| N = 2n | Number of addresses in virtual address space |

| M = 2m | Number of addresses in physical address space |

| P = 2p | Page size (bytes) |

| Components of a virtual address (VA) | |

| Symbol | Description |

| VPO | Virtual page offset (bytes) |

| VPN | Virtual page number |

| TLBI | TLB index |

| TLBT | TLB tag |

| Components of a physical address (PA) | |

| Symbol | Description |

| PPO | Physical page offset(bytes) |

| PPN | Physical page number |

| CO | Byte offset within cache block |

| CI | Cache index |

| CT | Cache tag |

As we have seen, every time the CPU generates a virtual address, the MMU must refer to a PTE in order to translate the virtual address into a physical address. In the worst case, this requires an additional fetch from memory, at a cost of tens to hundreds of cycles. If the PTE happens to be cached in L1, then the cost goes down to one or two cycles. However, many systems try to eliminate even this cost by including a small cache of PTEs in the MMU called a translation lookaside buffer (TLB).

A TLB is a small, virtually addressed cache where each line holds a block consisting of a single PTE. A TLB usually has a high degree of associativity. As shown below, the index and tag fields that are used for set selection and line matching are extracted from the virtual page number in the virtual address. If the TLB has T = 2t sets, then the TLB index (TLBI) consists of the t least significant bits of the VPN, and the TLB tag (TLBT) consists of the remaining bits in the VPN.

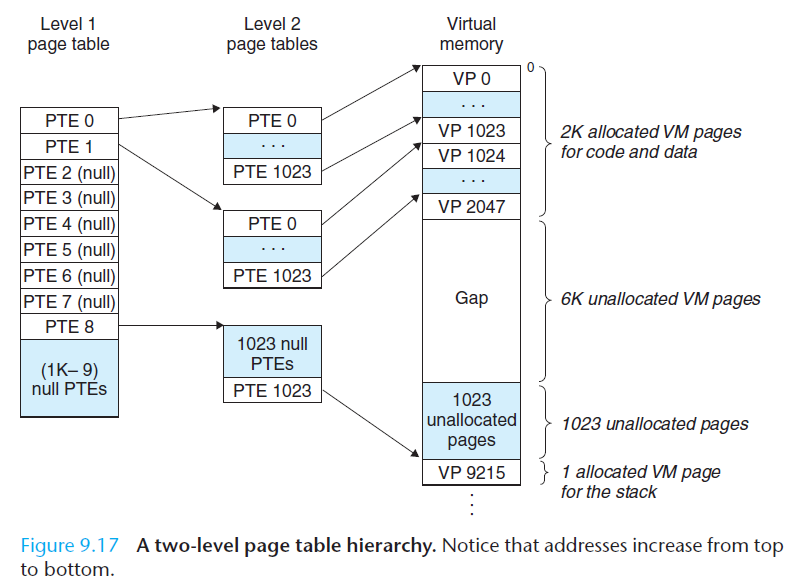

Two-level paging scheme

可以转载, 但必须以超链接形式标明文章原始出处和作者信息及版权声明

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】凌霞软件回馈社区,博客园 & 1Panel & Halo 联合会员上线

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】博客园社区专享云产品让利特惠,阿里云新客6.5折上折

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步