Makefile

Makefile 是和 make 命令一起配合使用的.

很多大型项目的编译都是通过 Makefile 来组织的, 如果没有 Makefile, 那很多项目中各种库和代码之间的依赖关系不知会多复杂.

Makefile的组织流程的能力如此之强, 不仅可以用来编译项目, 还可以用来组织我们平时的一些日常操作. 这个需要大家发挥自己的想象力.

长话短说,我们直接来实战下:

首先我们创建个c文件和h文件:

main.c

#include <stdio.h>

#include "fun.h"

int main()

{

fun();

return 0;

}

fun.h

void fun()

{

printf("hello world!\n");

}

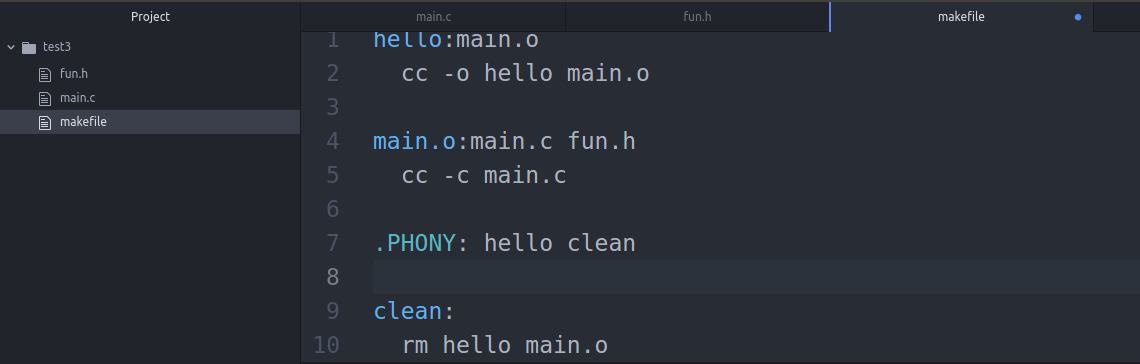

下面就是来对makefile进行编写:

hello:main.o

cc -o hello main.o

main.o:main.c fun.h

cc -c main.c

.PHONY: hello clean

clean: rm hello main.o

hello:你需要生成的目标文件

main.o:属于前置条件

cc -o hello main.o:属于命令

下面代码也类似

clean:属于“伪目标”,主要就是用来删除对象文件

但是,如果当前目录中,正好有一个文件叫做clean或者hello,那么这个命令不会执行。因为Make发现clean文件已经存在,就认为没有必要重新构建了,就不会执行指定的rm命令。

为了避免这种情况,可以明确声明clean和hello是"伪目标",写法如下。

.PHONY: hello clean

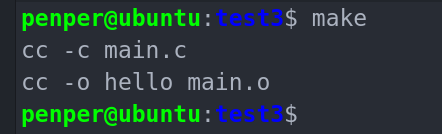

下面我们进行编译:

在命令行写入:make

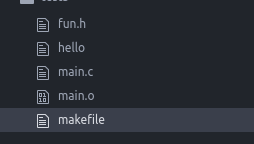

可以发现,目标文件已经生成

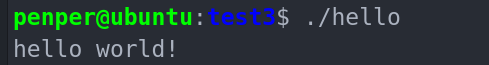

然后我们继续。。。。

发现成功了。。美滋滋

如果文件非常多,我们可以统一编写如下的makefile文件:

hello:main.o

gcc -o $@ $^

.c.o:

gcc -c $?

.PHONY: hello clean

clean:

rm hello *.o

下面是所有的自动化变量及其说明:

- $@

- 表示规则中的目标文件集。在模式规则中,如果有多个目标,那么,"$@"就是匹配于目标中模式定义的集合。

- $<

- 依赖目标中的第一个目标名字。如果依赖目标是以模式(即"%")定义的,那么"$<"将是符合模式的一系列的文件集。注意,其是一个一个取出来的。

- $?

- 所有比目标新的依赖目标的集合。以空格分隔。

- $^

- 所有的依赖目标的集合。以空格分隔。如果在依赖目标中有多个重复的,那个这个变量会去除重复的依赖目标,只保留一份。

浙公网安备 33010602011771号

浙公网安备 33010602011771号