利用IP核设计高性能的计数器

利用Quartus II的LPM_counter IP核进行设计(利用IP核设计可以迅速高效的完成产品的设计)

新建工程

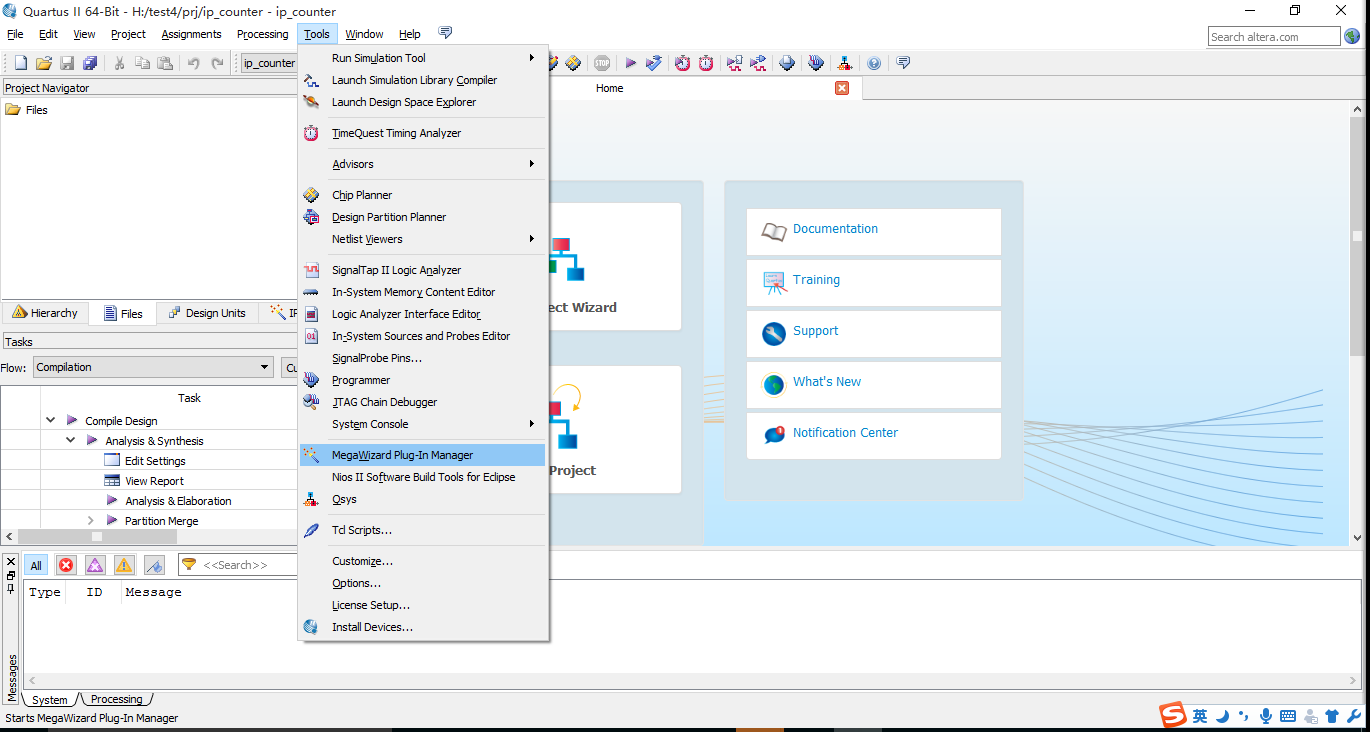

调用IP核

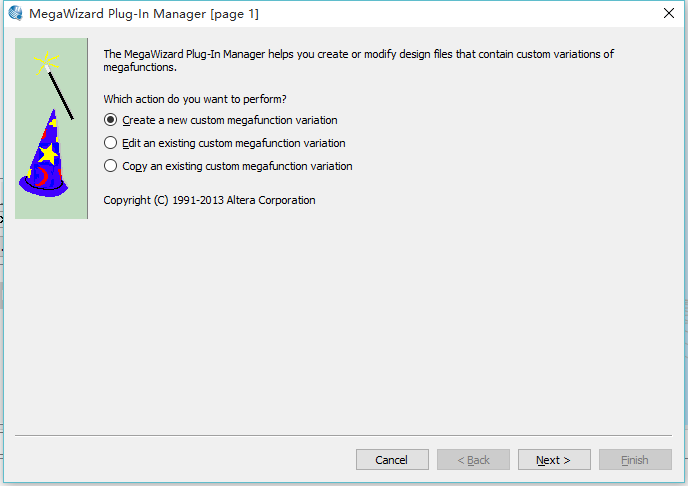

创建一个新的IP核

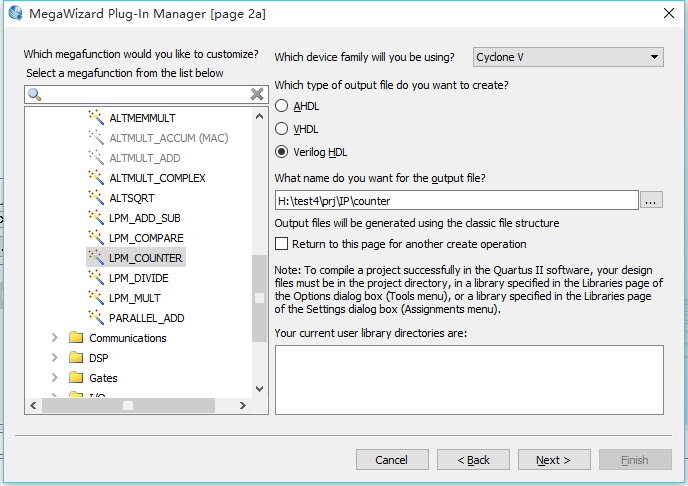

选择LMP_COUNTER,语言类型,输出路径。

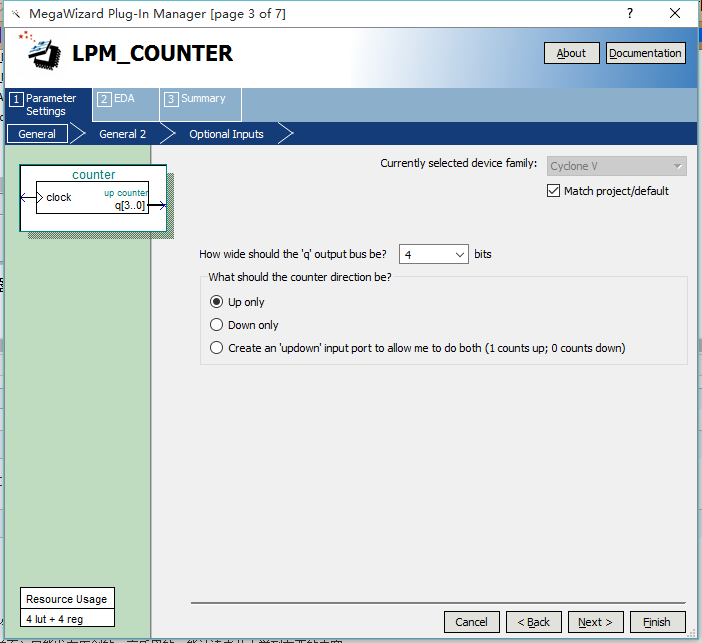

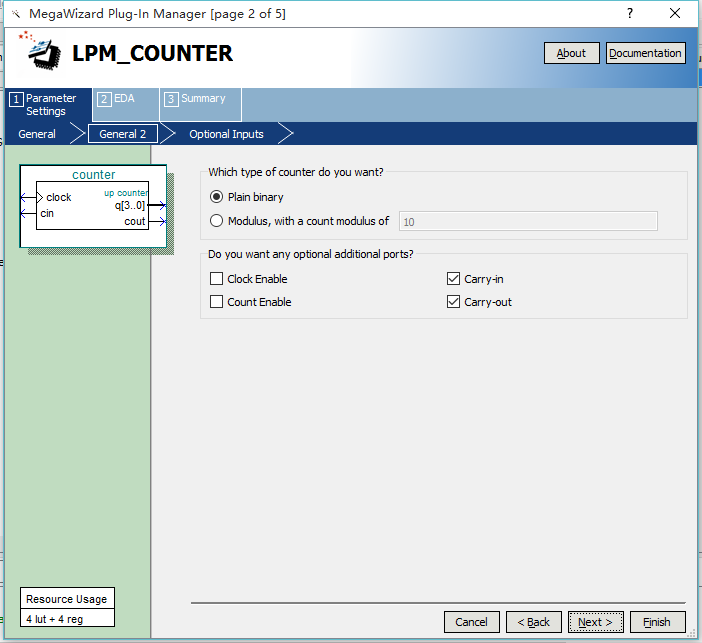

选择希望输出的寄存器是多少位的,计数类型,

选择计数器类型(直接计数还是以模的形式计数),是否需要时钟使能和计数使能信号、进位链的输入和进位链的输出。

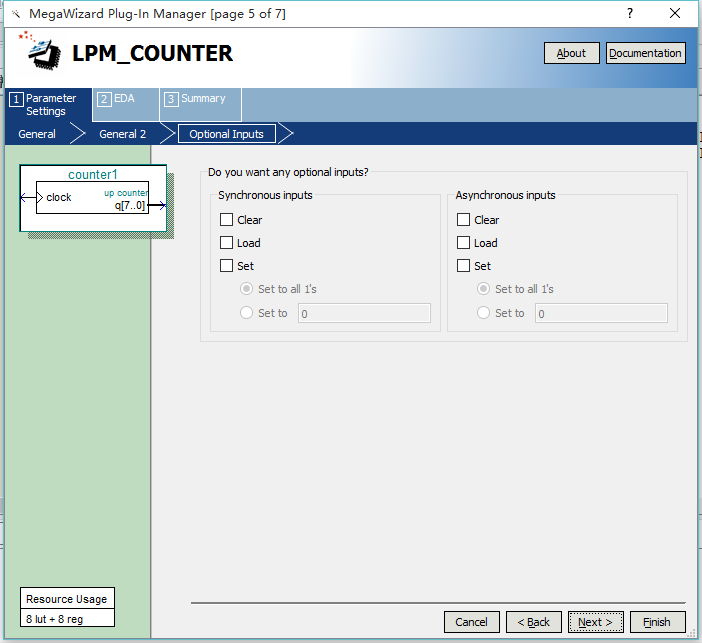

清零加载等信号

之后一直next直到finish

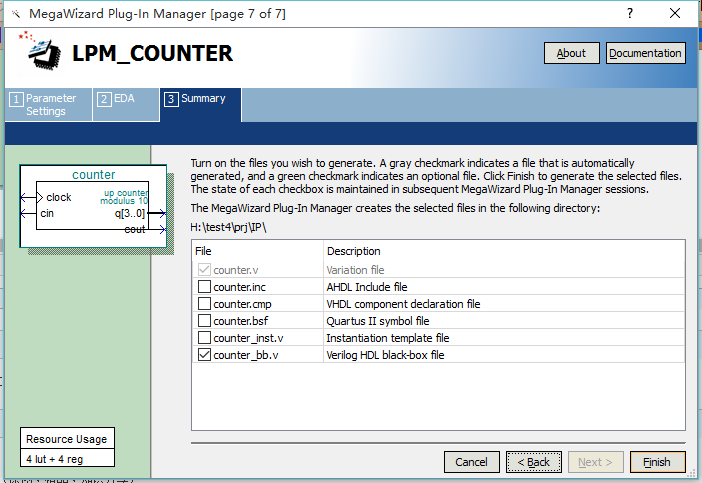

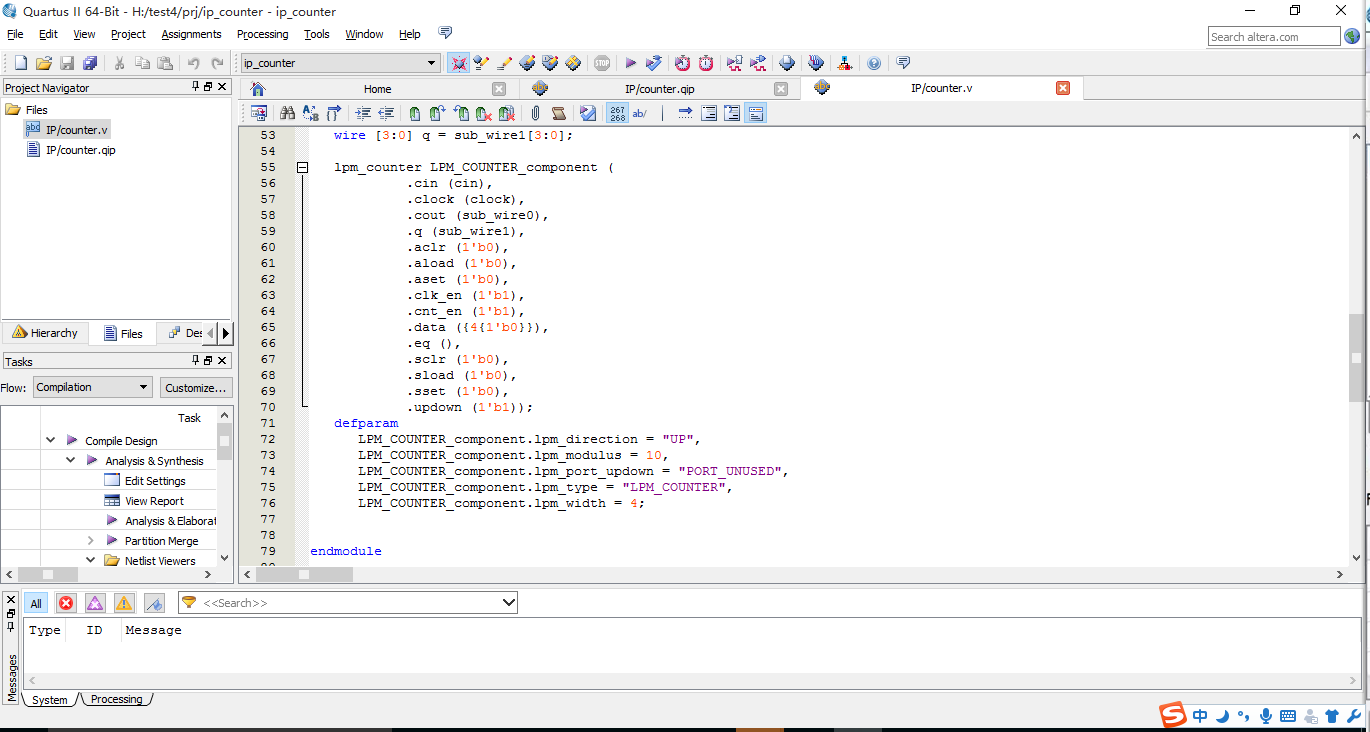

创建成功后的IP核的文件信息

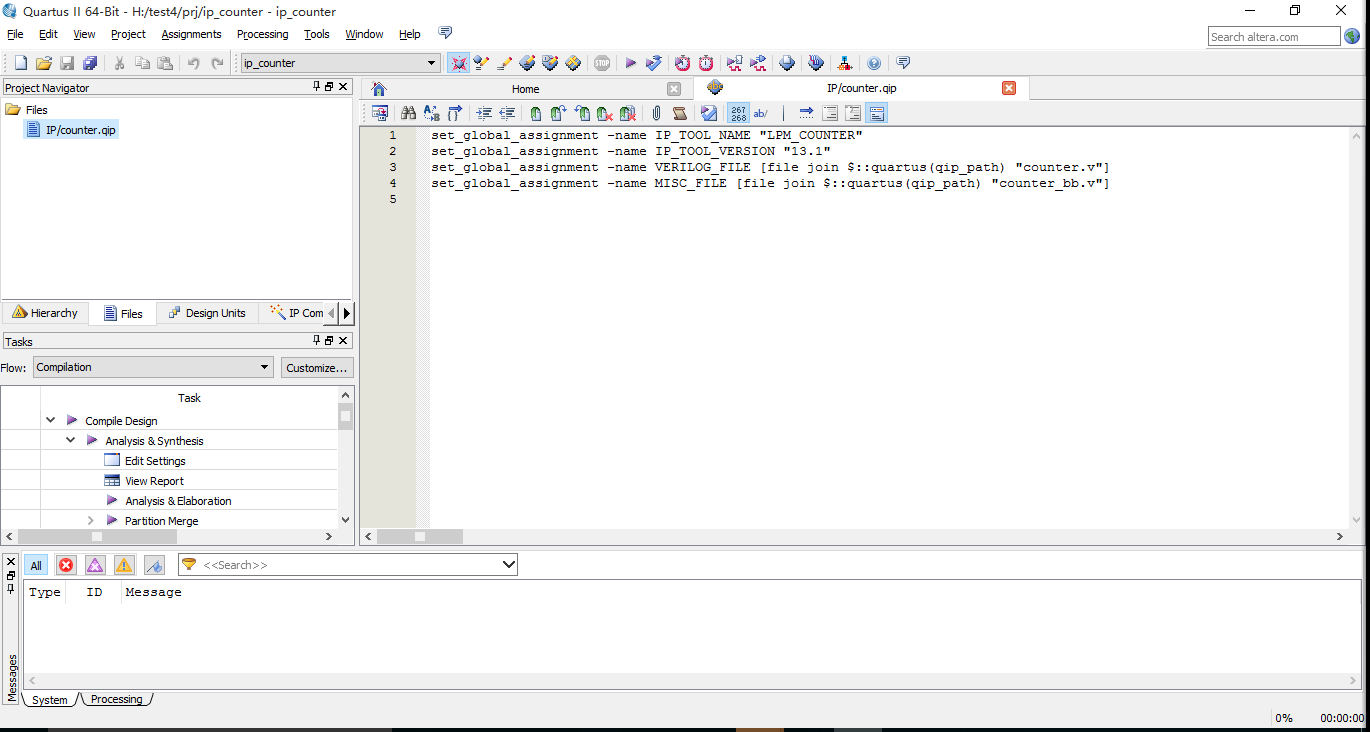

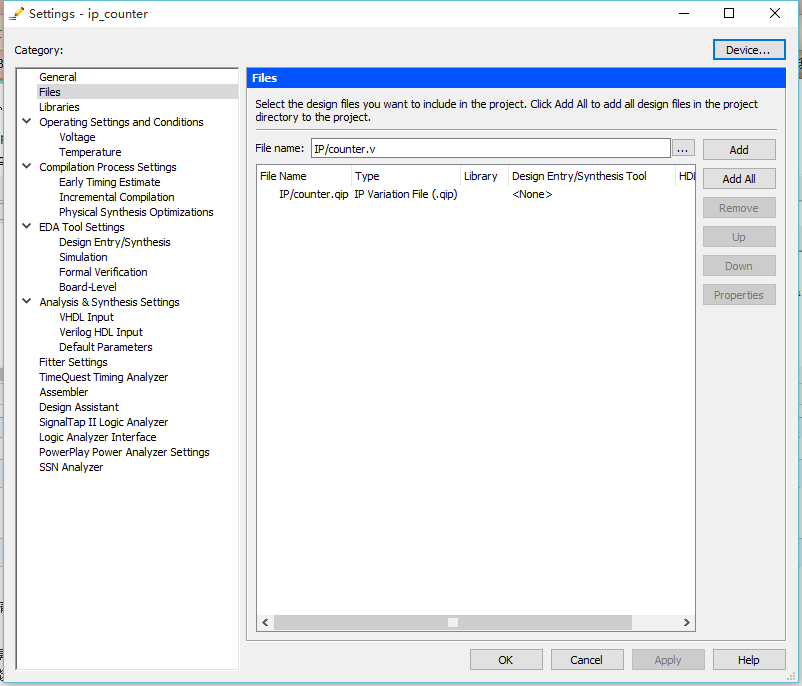

将counter.v文件加载到软件中

打开可以看到其中的接口文件。

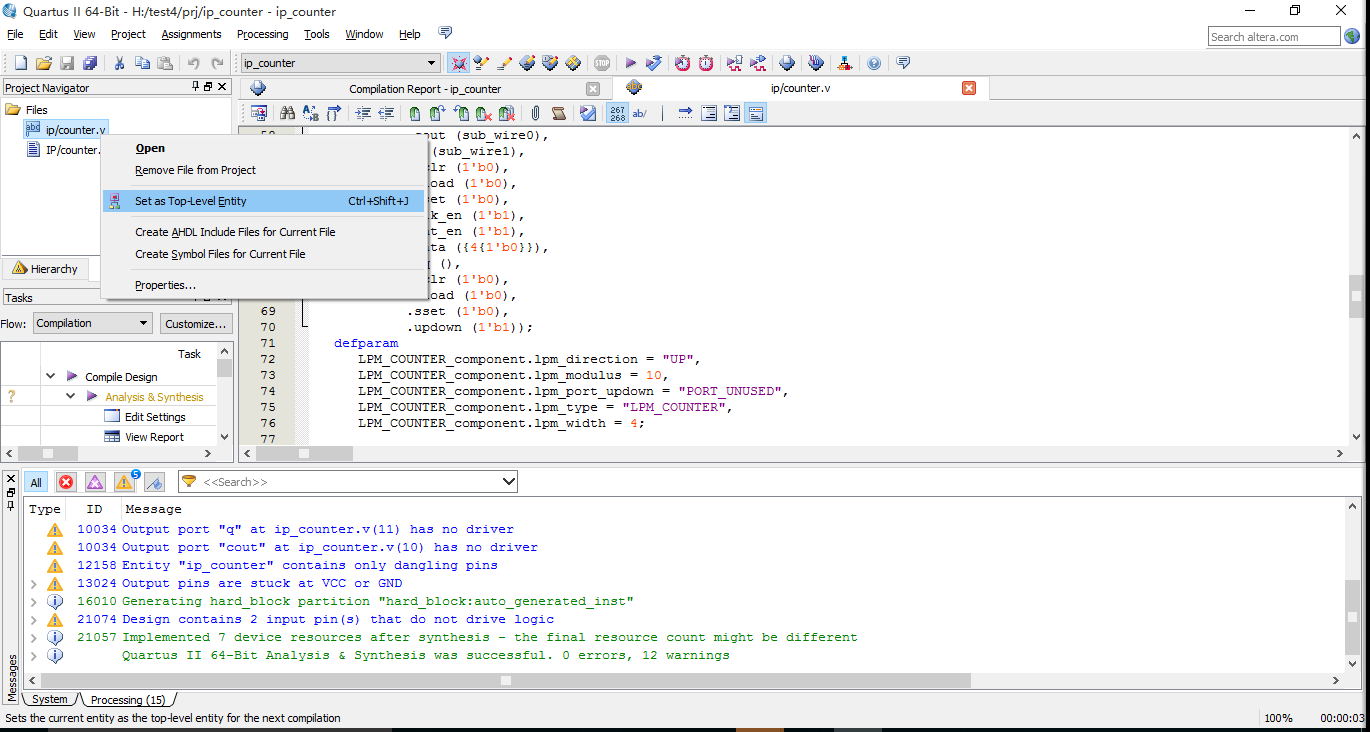

把ip_counter设置为顶层文件后进行编译。

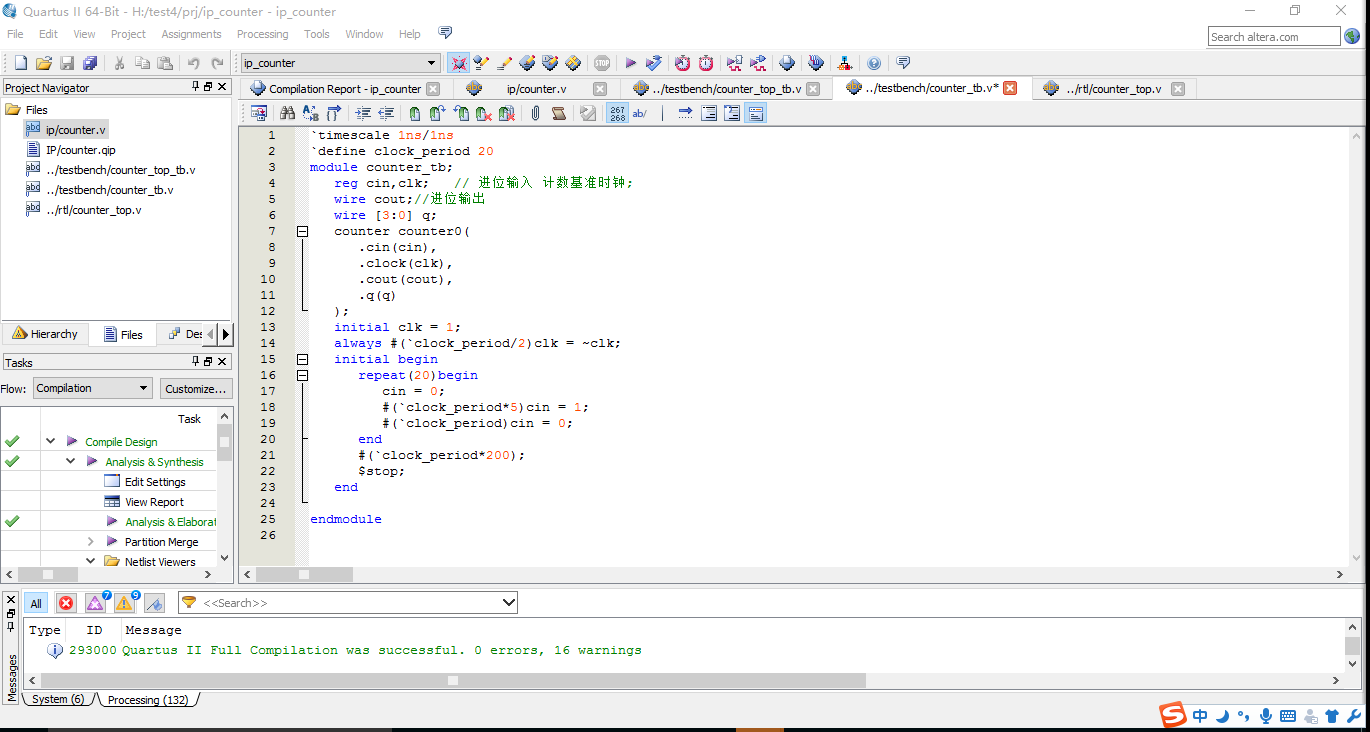

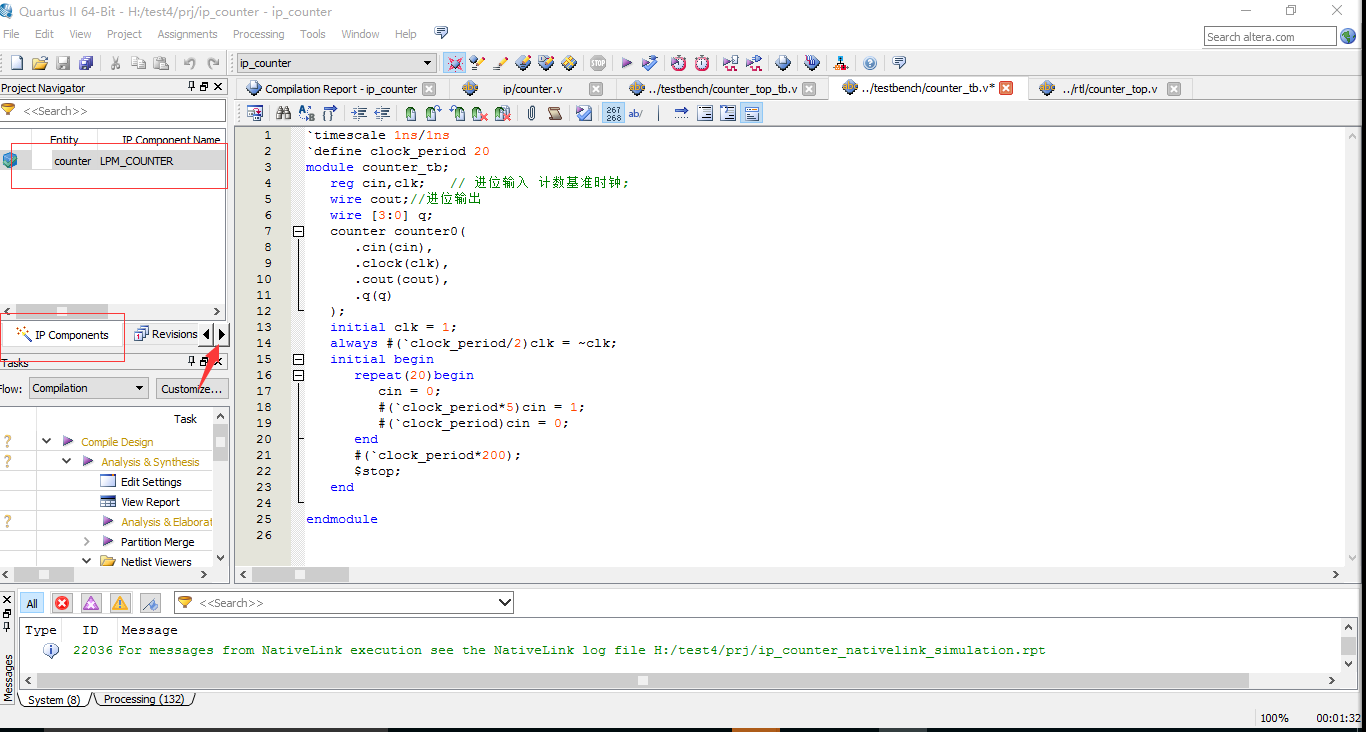

编写testbench文件

`timescale 1ns/1ns

`define clock_period 20

module counter_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [3:0] q;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout),

.q(q)

);

initial clk = 1;

always #(`clock_period/2)clk = ~clk;

initial begin

repeat(20)begin

cin = 0;

#(`clock_period*5)cin = 1;

#(`clock_period)cin = 0;

end

#(`clock_period*200);

$stop;

end

endmodule

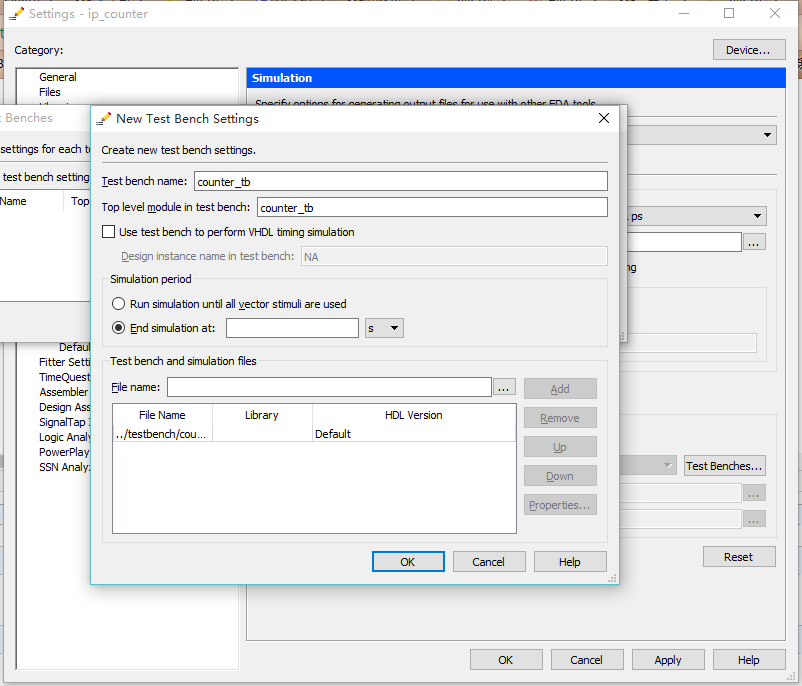

设置仿真链

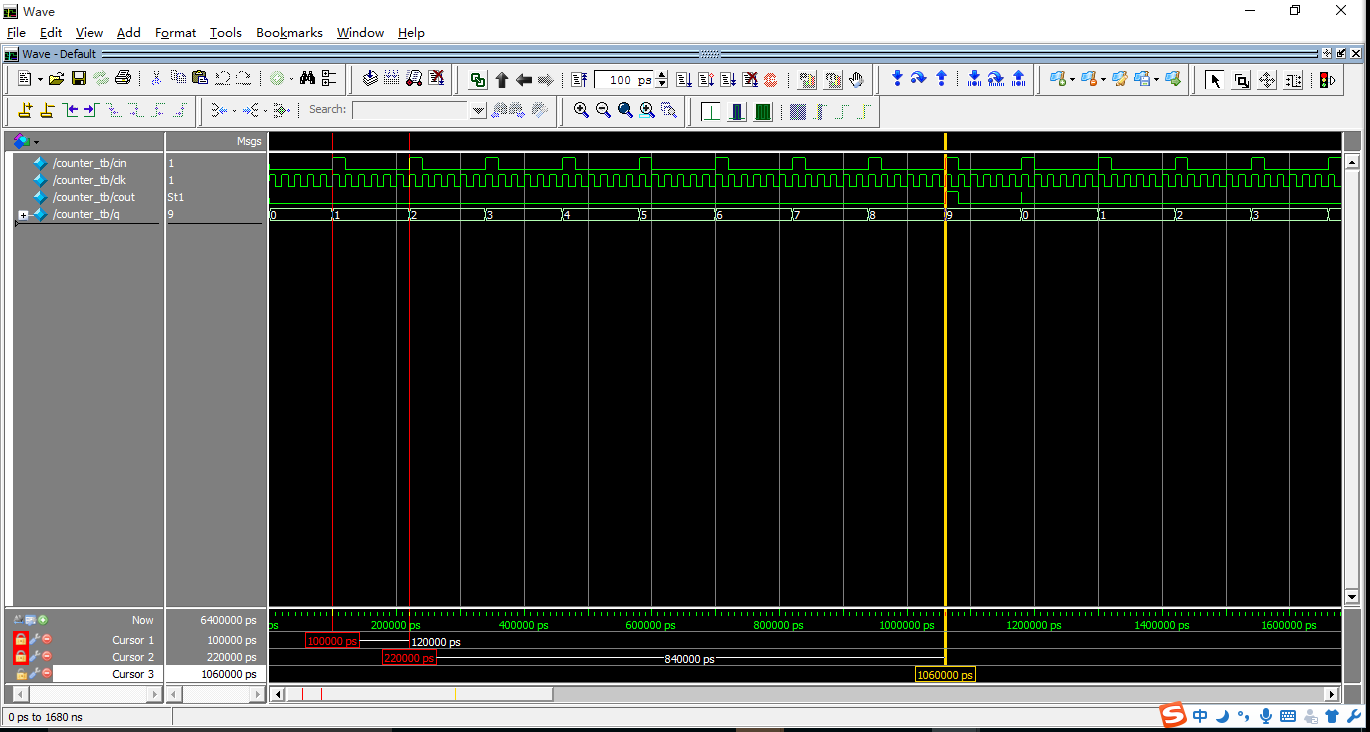

运行 仿真,可以看到每隔5个clk有一个cin信号,计数器完成一次计数,到计数到设定的模值10时会产生一次c_out信号,然后计数器重新开始从0开始计数,与设计的期望。

在软件中点击箭头指向的方向键,左右切换显示到IP components,双击方框中的文件可以修改IP核的设置。

但是,IP核设置的位数是有上限的,为了提供更好的方法,下面提供一种级联的方法对计数值进行拓展。

在IP核中将计数模值改为直接技术模式

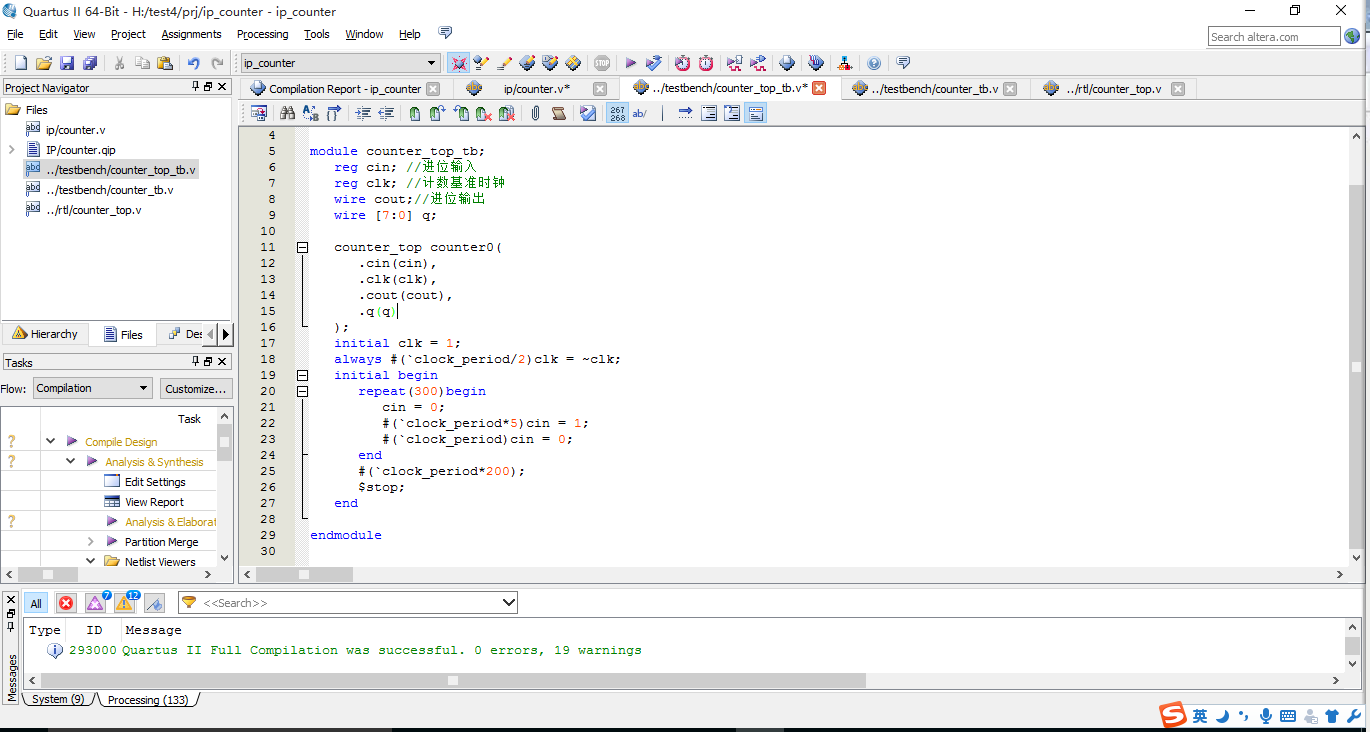

新建Verilog文件进行编程如下。

module counter_top(cin,clk,cout,q);

input cin;

input clk;

output cout;

output [7:0]q;

wire cout0;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout0),

.q(q[3:0])

);

counter counter1(

.cin(cout0),

.clock(clk),

.cout(cout),

.q(q[7:4])

);

endmodule

这里的原理是将前一级的c_out作为下一级计数的c_in,此时即将两个计数器级连起来了,这样就将一个四位的计数器转换成了一个八位的计数器。

将这个文件设置为顶层文件

编写testbench如下

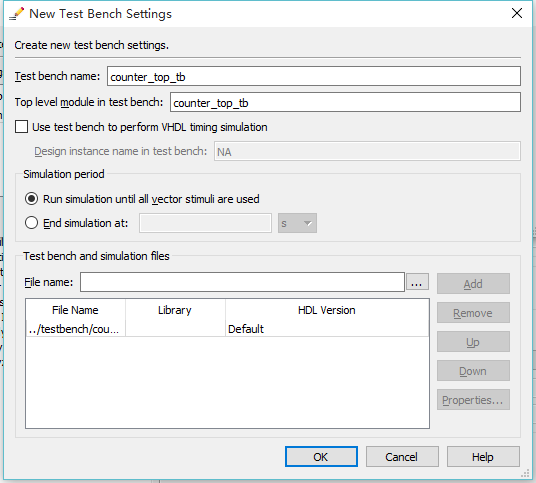

设置仿真脚本

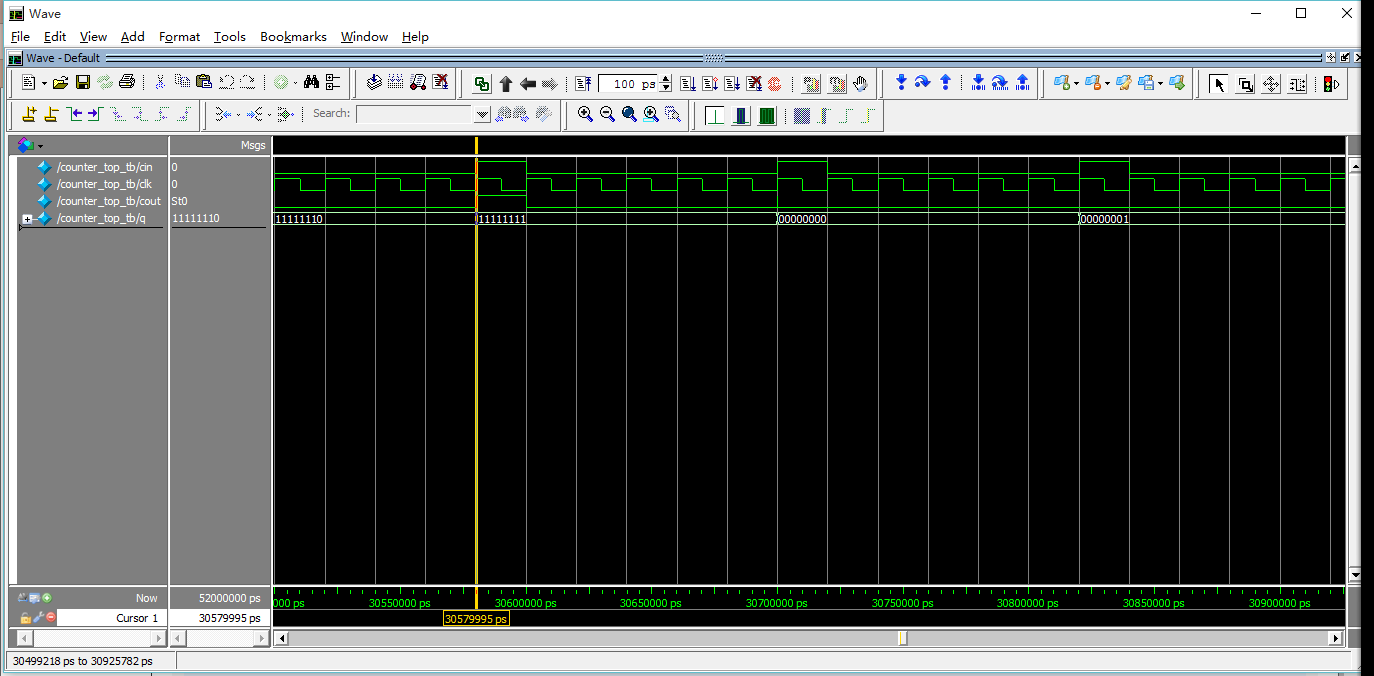

点击仿真工具进行仿真可以看到计数为8个1时输出c_out ,这与我们期望的是一样的。

至此,基于IP核设计一个计数器的方法就设计完成了。可以对应的将c_out,输出到LED上进行观察,这里就不再实际操作了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号