基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器。

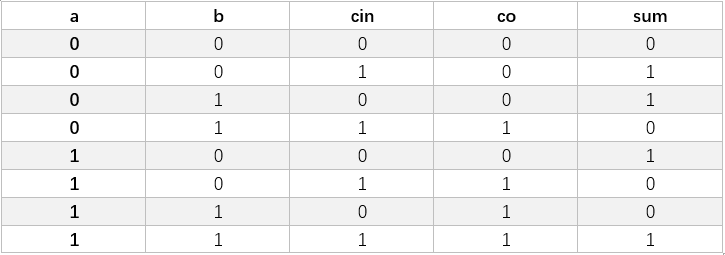

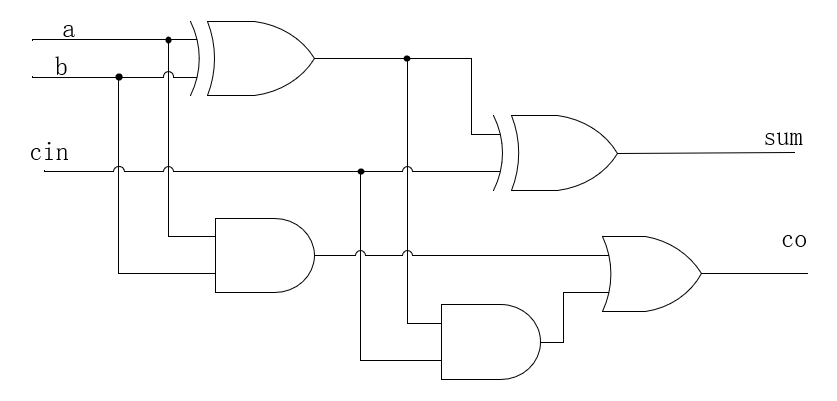

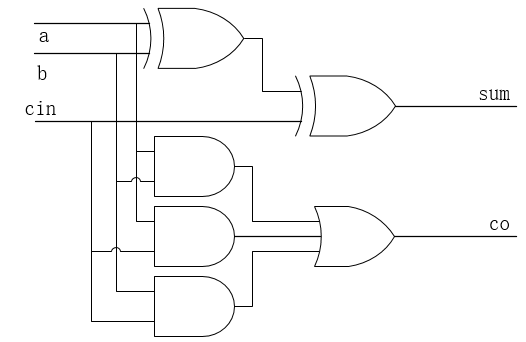

全加器的两个逻辑表达式

sum = a ^ b ^ cin;

co = a & b | (a ^ b) & cin;

sum = a ^ b ^ cin;

co = a & b + a & cin + b & cin;

这两个公式的电路图看起来不一样,但其实是一样的,同一个功能的电路可以有不同的描述方式。而且把co这两个表达式展开,观察其最小项表达式(画卡诺图),最终的结果也是一样的和真值表完全相符。

四位超前进位全加器

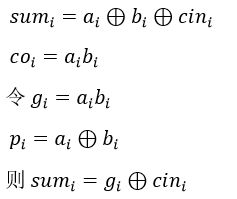

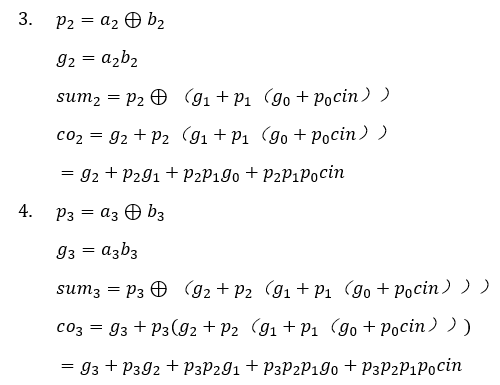

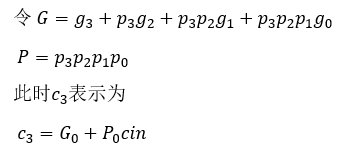

根据一位全加器的表达式可以推理出,四位全加器每一位的计算通式。

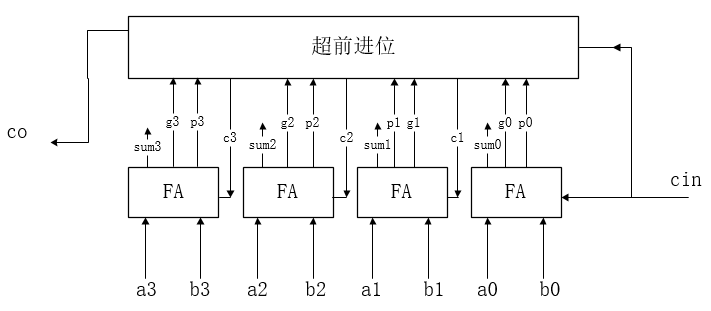

为了达到并行的效果,通过公式化简,得到co和sum的表达式,每一位之间的运算都是独立的,和低位的运算没有关系,这样做达到完全并行,这就是四位超前进位全加器。

有了四位全加器,我们可以以通过四位超前进位全加器设计出16位、32位、64位超前进位全加器,有些设计方法是将四个四位超前进位全加器串联起来,即将低四位的co连接到高四位的cin上,但这样并不能算得上是真正的并行,每四位是并行的,但每四位之间是串行的,博主目的是要达到完全并行的设计,继续往下看吧。

这里的g是generation(生成)的意思,当a和b同时为1时,1位全加器必然产生进位,p表示propagation(传到)的意思,当a或b中有一个是1时,如果进位cin位1,1位全加器必然产生进位,利用这个原理即可做出四位超前进位全加器之间的超前进位。

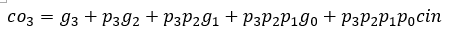

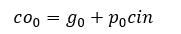

四位超前进位全加器的co进位输出端为

这与一位全加器的进位类似,

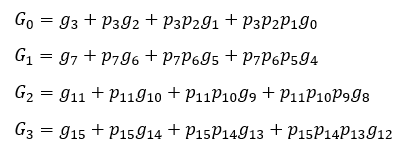

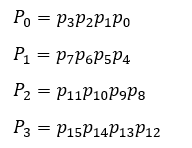

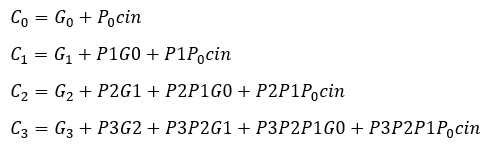

我们可以推出如下关系式

我们通过调用四个超前进位全加器即可实现16位超前进位全加器,那么实现64位超前进位全加器其实也是和这个实现方法一样了,调用4个16位超前进位全加器就可以实现64位超前进位全加器。不过实际中CPU采用的是超前进位和串行进位集合,并行设计占面积,串行设计速度慢,尽量做到面积与速度之间的权衡。

博主最近要学Verilog设计一个32位的简易CPU,其中ALU中想用上32位超前进位全加器。对于32位超前进位全加器,也是一样的方法。我选择的是三级并行设计,即四个四位超前进位全加器组间并行实现16位超前进位全加器,两个16位超前进位全加器组间并行实现32位超前进位全加器,至于两级并行还是多级并行看自己选择了。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8798972.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号