全网首创ISE入门级教程

转眼间我已经大三了,现在成为了实验室的负责人,对于下一届学生的纳新重任就交到了我的手上,想采取不同的方法暑假尽可能对他们进行一些培训,所以制作了此教程,说实话,在网上还没有找到关于ISE的入门级使用教程呢!可谓是全网首创啊!话不多说,我们赶紧看看我的处女视频教程吧!

互联网是最好的学习平台,让贫富之间的教育资源差距减小,对于FPGA来说晚上的教学资料、视频非常多,但是多数为Altera的QuartusII开发套件使用,而Vidado的使用貌似这两年也多了起来,那么ISE被抛弃了吗?之前有过一个前辈做过关于ISE的使用教程,但那都涉及到摄像头驱动的FPGA进阶阶段了,所以今天这套FPGA入门第一课的视频教程,可真谓是全网首创关于ISE软件的使用教程。这是西邮电院FPGA创新小组的纳新公开课,FPGA入门第一课一位全加器的设计(ISE使用教程的百度云盘链接在文章第五部分)。

一、 FPGA创新小组纳新公告

FPGA创新实验室处于西安邮电大学2号实验楼(电子工程学院实验楼)107实验室。主要学习方向为数字集成电路设计(FPGA),每年九月份中旬进行纳新,主要面向微电子系(集成电路和微电子专业)的16级学生。为了使纳新结束后大家能够快速进入学习状态,我们暑假会针对纳新考核进行相应的培训,让大家提前有一个对FPGA的认识并且能设计出一些简单的电路。群文件有相关资料,请大家自行下载学习。前期需要大家将软件下载安装(链接如下),学习一些数电基础知识(群文件有数电电子书康华光版),Verilog基本语法(请看群文件),后面的线上课程会再通知。大家有什么疑问可以直接在群里提出。

二、 FPGA是什么

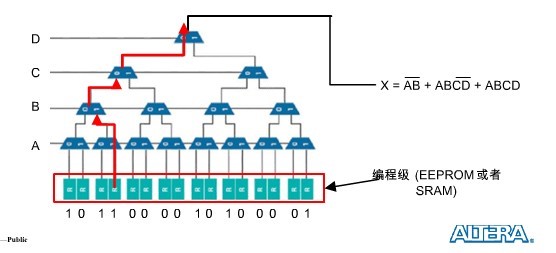

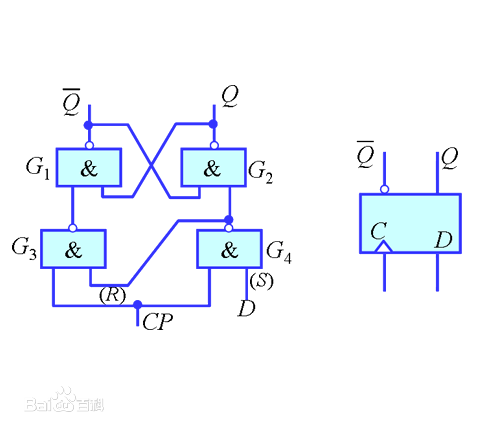

FPGA(Field-ProgrammableGate Array),即现场可编程门阵列,使用Verilog HDL(Hardware Description Language)进行描述,FPGA可以理解为把数字电路的元器件都集成到FPGA芯片内部,与门、或门、选择器、D触发器。实际上它内部构造是用FPGA利用小型查找表(LUT)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O(input/output),由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

图 - LUT实现原理图

图 – D触发器

总的来说,它是利用verilogHDL硬件描述语言来描述数字电路,你所写的代码,映射到板子上实际上就是一些数字电路。

FPGA公司主要是两个Xilinx和Altera(现intel PSG),我们目前用的ISE是Xilinx的开发套件,现在ISE更新到14.7已经不更新了,换成了另一款开发套件Vivado,也是Xilinx的产品,intel的开发套件是Quartus II系列,我们实验室这两款公司的开发板都有,不用对于入门来说,选择ISE有两个原因,一是它比Vivado快多了,二是它和Quartus II相比不用自己写测试文件(激励)。实验室的板子这两个公司都有,代码都是可以移植的,学习的话都要学的,软件不是问题,重点是FPGA的设计思想。

三、 FPGA与单片机的区别

对于单片机和FPGA的主要区别。单片机可以理解为跑程序的微型电脑,麻雀虽小五脏俱全,所以写的代码相当于程序,应该属于软件范畴。单片机写出来程序,用编译器编译后实际上是一条条指令,控制单片机去控制它的外围器件。

FPGA则应该理解为可编程的数字逻辑电路集成芯片,所以写的代码其实是在描绘一个数字逻辑电路。

两者最大的区别应该是在速度上的区别,FPGA内部是并行的,所有的电路逻辑都是在同一个时钟触发下工作的,而单片机属于单线程,内部属于顺序执行,一个执行完了再执行下一个。速度肯定要慢。

FPGA主要用于通信、图像处理等领域,ASIC的设计验证,就在去年到今年还有一个新的领域AI,用FPGA加速深度学习算法,BAT也都部署了FPGA云服务器。因为其速度快的优点,所以用来处理数字信号是所擅长的。最经典的是2008年北京奥运会开幕式的画卷显示屏用的就是Altera Cyclone II FPGA驱动的。

在初学FPGA的时候容易的是把VerilogHDL当C语言来写,把FPGA但单片机来用。写的代码不能称之为程序,应该称之为代码,以区别和软件的不同。

图 – CPU与FPGA

四、 一位全加器的设计

需要基础知识:二进制的加法运算、真值表、卡诺图、Verilog HDL基本语法

1 + 1 =1 0; 1 + 0 = 1; 0 + 0 = 0;

全加器(Full Adder)

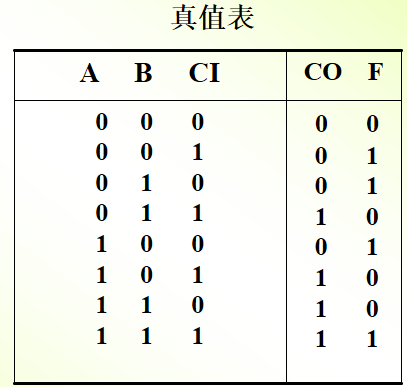

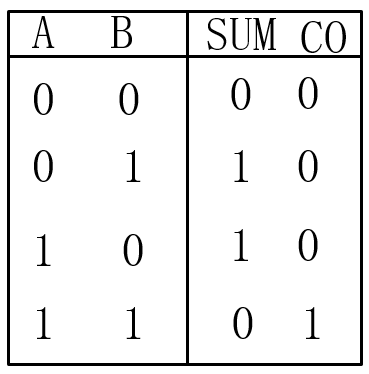

图 - 一位全加器真值表

上图是数电书上的全加器真值表,下图是我自己画的。

A和B为两个加数,CI表示低位向本位的进位,CO本位向高位的进位。我们在这里设计中用不到CI,设计超前进位加法器会用到。所以看右边的图就可以了。

Verilog有四种描述风格:晶体开关级描述风格、门级描述风格、数据流风格、行为级描述风格。

开关级描述风格太老我们不学。门级描述风格也太原始,交给你们数电老师去教。数据流描述风格虽然不常用,但是为了更加深刻理解组合逻辑的设计,所以后续课程在进行讲解。今天我们就用最简单,最迅捷的行为级描述来描述这一个一位加法器。

五、 ISE14.7使用流程

-

FPGA创新小组纳新公开课class1:百度云链接:http://pan.baidu.com/s/1bpAgmtD 密码:psx2

视频中有详解

-

ISE14.7与Notepad++级联:http://www.cnblogs.com/ninghechuan/p/6172237.html

-

注意

(1) Wire型数据只能能在assign语句里赋值

(2)Reg型数据只能在initial块,always块,for赋值

六、 课后练习

-

重新新建一个工程,自主设计一个四位全加器,要求有仿真。最终将工程打包发送至我的邮箱ninghechuan@foxmail.com,可以编写一份文档对设计进行概述和说明,附加学习心得和感想

七、 你能得到什么

-

首先是提高动手能力,很多东西自己动手做一遍和你从课本上学理论的感受是不一样的。

-

我们实验室每年都会组织参加各类电子竞赛,增强项目实践能力。

-

增加考研就业竞争力,

-

实验室有空调,有空调,空调,调。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:NingHeChuan

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/7171791.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· 从HTTP原因短语缺失研究HTTP/2和HTTP/3的设计差异

· 三行代码完成国际化适配,妙~啊~