EDA设计(verilog)——七裁判逻辑电路

描述:现在有7个裁判对选手进行评判,裁判可以选择通过和不通过两个状态,(用0表示通过,用1通过),当选择通过的裁判数目大于一半时(4或4以上)就让选手晋级,否则淘汰(用1表示选手晋级,0表示选手淘汰)。

测试样例:

| 输入电平样例 | 输出电平样例 |

|---|---|

| 0000000 | 0 |

| 11111111 | 1 |

| 0000111 | 0 |

一、综合代码

module decision_circuit_7(a,out);

input[6:0] a;

output out;

wire[2:0] out1;

add_7 ad(a,out1);

assign out=(out1>=4)?1:0;

endmodule

module add_7(a,out);

input[6:0] a;

output[2:0] out;

assign out=((a[0]+a[1])+(a[2]+a[3]))+((a[4]+a[5])+a[6]);

endmodule

二、测试代码

`timescale 1 ps/ 1 ps

module decision_circuit_7_vlg_tst();

reg [6:0] a;

wire out;

decision_circuit_7 i1 (

.a(a),

.out(out)

);

initial

begin

$display("Running testbench");

#0 a[0] = 1; a[1] = 1; a[2] = 1; a[3] = 1; a[4] = 1; a[5] = 1; a[6] = 1;

#1 $display("input:%b -- out:%b", a, out);

// 这里的输出之前一定要加延迟,否则输出的是上一时刻哦。

#9 a[0] = 1; a[1] = 1; a[2] = 1; a[3] = 1; a[4] = 1; a[5] = 1; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 1; a[1] = 1; a[2] = 1; a[3] = 1; a[4] = 1; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 1; a[1] = 1; a[2] = 1; a[3] = 1; a[4] = 0; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 1; a[1] = 1; a[2] = 1; a[3] = 0; a[4] = 0; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 1; a[1] = 1; a[2] = 0; a[3] = 0; a[4] = 0; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 1; a[1] = 0; a[2] = 0; a[3] = 0; a[4] = 0; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9 a[0] = 0; a[1] = 0; a[2] = 0; a[3] = 0; a[4] = 0; a[5] = 0; a[6] = 0;

#1 $display("input:%b -- out:%b", a, out);

#9;// 这里的#9是为了让波形持续10的单位,否则代码会立即结束,最后一个波形只有一个瞬间

end

endmodule

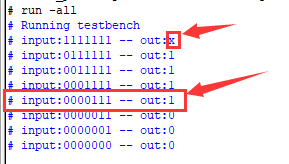

三、测试结果

控制台输出

波形图

$display()没有加延时的错误输出

浙公网安备 33010602011771号

浙公网安备 33010602011771号