这几天一直在看SOPC Builder的用户手册,从中看到了很多Avalon接口的高级特性。之前一直对Avalon Memory-Mapped Bridges的作用以及用法不是很了解,今天猛然发现这确实是个好东西,可以提高系统性能的同时降低FPGA资源的利用率。

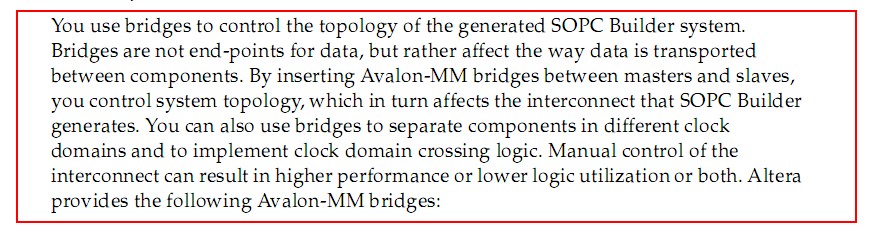

那这个bridge究竟实现了这么样的一个功能呢?

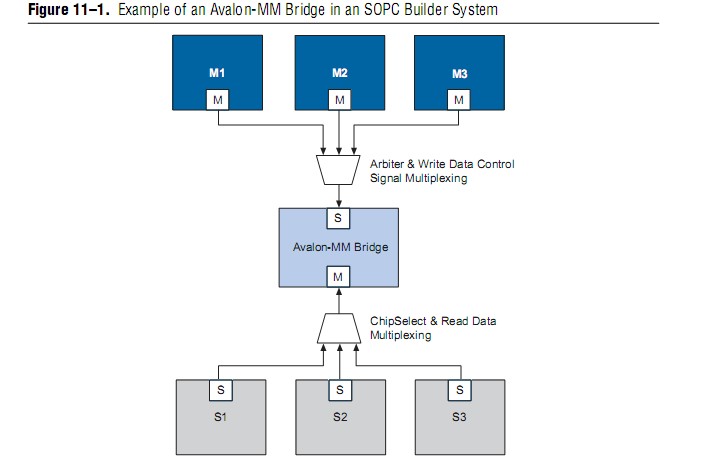

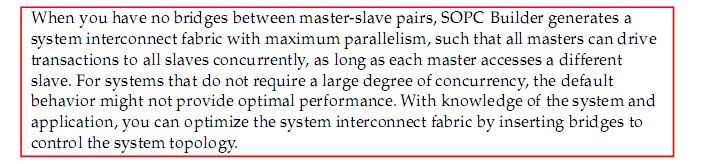

为什么我们要使用这个bridge,它能给我们带来哪些好处呢?

如果没有添加bridge,就像下面这个图中显示的那样,整个系统显得很繁琐

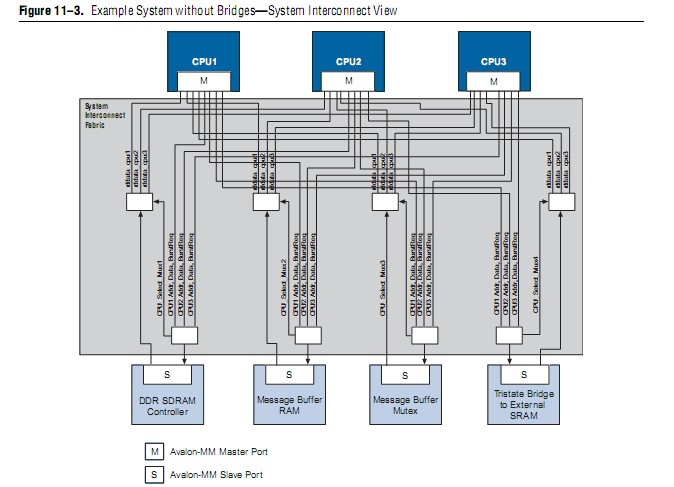

现在我们来看看 Avalon-MM clock-crossing bridge和Avalon-MM pipeline bridge能给我们系统带来的利好

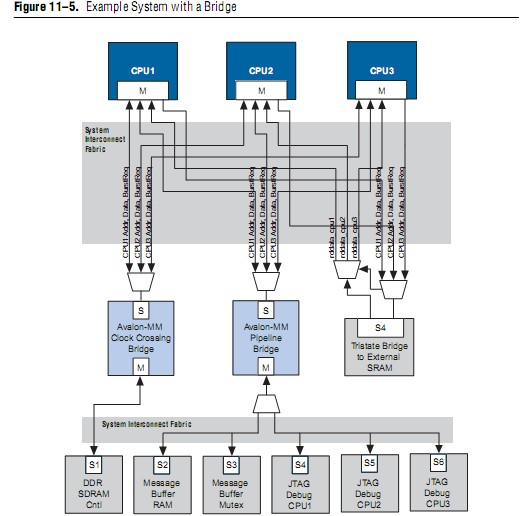

同样的一个系统,添加了这两个bridge后样貌大不一样了,是不是感觉系统结构更清晰了

这个性能的提高就需要我们来具体验证了,看来我们不光要实现功能,还要在结构与性能上追求更完美