【原创】SystemVerilog中的typedef前置声明方式

SystemVerilog中,为了是代码简洁、易记,允许用户根据个人需要使用typedef自定义数据类型名,常用的使用方法可参见“define和typedef区别”。但是在SystemVerilog引入面向对象编程后,经常会遇到在编写某个类或者类型的定义之前需要先使用对变量进行声明,往往这种情况下编译都会报错,为此本文示例typedef的另外一种用法,可以称之为“forward typedef”。

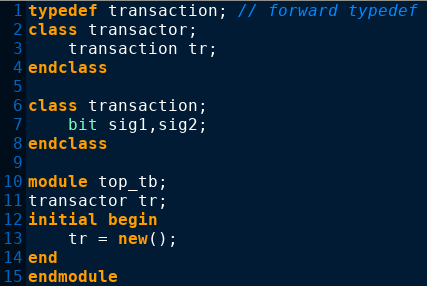

【示例】未使用forward typedef

【仿真结果】

示例中,因为transaction的定义出现在使用该类型的transactor之后,所以在编译时,仿真器编译到transactor中的transaction时,发现已经变异的库中并没有对应文件的定义,所以此时编译会报错,认为transaction还没有定义。但是往往在进行验证环境设计搭建时,经常需要像示例中的方式使用,为此SystemVerilog中可以通过typedef将要使用的类型进行前置,如下例。

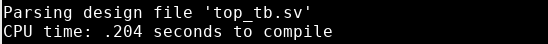

【示例】

【仿真结果】

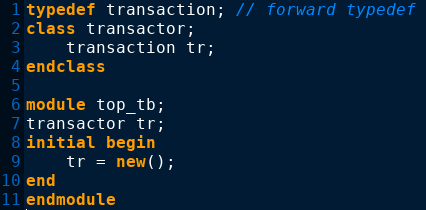

但是使用时必须要注意,如果使用“forward typedef”,那么被typedef前置的类型的定义必须在当前代码的后续编译过程中出现其定义,否则还是会报错,如下例。

【示例】

【仿真结果】

除了上述用法外,typedef还可以用于具有参数的class。

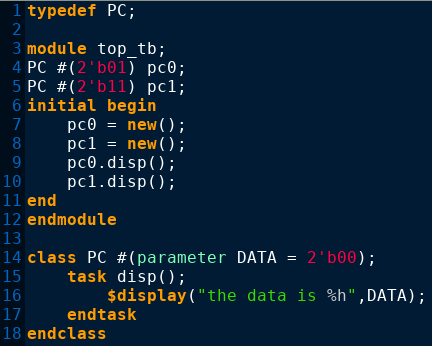

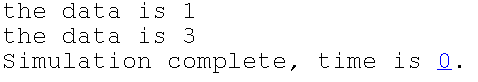

【示例】

【仿真结果】

通过上述示例,typedef可以用于将一些数据类型进行前置声明(forward declaration),这样仿真工具允许该类型的定义在后续的编译过程中再出现,特别是对于比较复杂的验证环境的构造过程中,该种用法还是比较多的。但是这里需要注意的时,一旦使用typedef的前置声明方法,那么在后续的编译过程中,必须要出现前置声明的类型的具体定义。

更多技术内容,可关注下图个人技术微信公众号,欢迎朋友们关注沟通!

浙公网安备 33010602011771号

浙公网安备 33010602011771号