记一次基于FPGA的VGA显示四操作数计算器工程的开发流程——(1)从顶层设计说起

首先值得说明的是,在这个项目几乎完成之际,笔者才愈发体会到了硬件思维和软件思维的云泥之别。不幸的是,在此项目的实现过程中,绝大部分代码的思维仍然是软件思维,因此该项目主要模块的设计部分可能并不能体现硬件操作的独到之处,不符合硬件工程师的基本设计思维,所以此主题文章仅用于学习交流以及记录一次FPGA项目设计的过程和细节,内部的时序逻辑、算法细节等都很难经得起推敲,仅供参考。

先给出这个设计的题目:

设计一个计算器。至少能够实现四个操作数的加减乘除,中间可以任意添加括号,使用VGA实时显示输入的内容和最终的计算结果,并通过串口输出数据到从机,在其上的数码管上显示结果。

在这个项目中,除了给组员分工了VGA显示,其他所有模块均由笔者来完成,因此可以说笔者几乎是全权负责了此工程的设计,所以经验收获颇丰😂www

首先,拿到一个工程,笔者一般遵从顶层到底层的设计原则,即先根据题目要求设想整体上实现功能大概需要哪些模块,每个模块的功能是什么,各模块之间如何连接和通信等。然后再针对各个具体的模块逐个击破,最后在顶层进行模块连接和整体封装。

所以先审题,得出这个计算器的具体过程是:用户通过矩阵键盘输入一个数学式子,如果式子合法,则按照数学规定的优先级执行计算,最后得到结果。不难看出,首先要解决的就是如何将用户的输入存入板子;然后识别该输入的内容,并判断该输入是否符合数学式的规则,最后根据识别的结果进行优先级计算。所以各主要模块的功能就很清晰了:

(1)录入模块:负责将用户的输入进行编码并存入到buffer中,并且可以实现功能按键相应的功能,如回退,左移,右移,清零(复位),等于(确认)。

(2)识别模块:根据编码识别录入模块输出buffer中的各元素,如操作数,运算符,各部分的位置信息等,形成为一个完整的数学算式,并且可以判断该输入是否合法。

(3)计算模块:根据识别模块输出的算式信息(如括号位置、运算符类型和操作数等)进行优先级判断,然后进行计算,输出计算的结果。

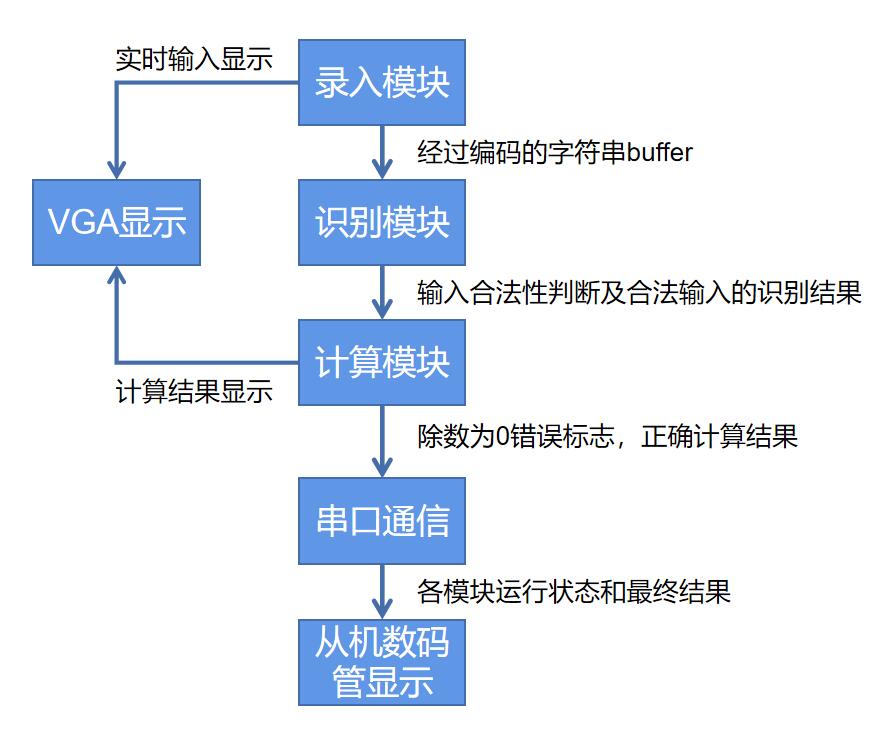

简单画了下各模块的执行过程:

各模块的执行框图

以上便为初步的顶层设计结果,看似简单明了,实则是经过一系列思考和优化总结来的(笑),下面记录一下设计初期的一些思考过程。

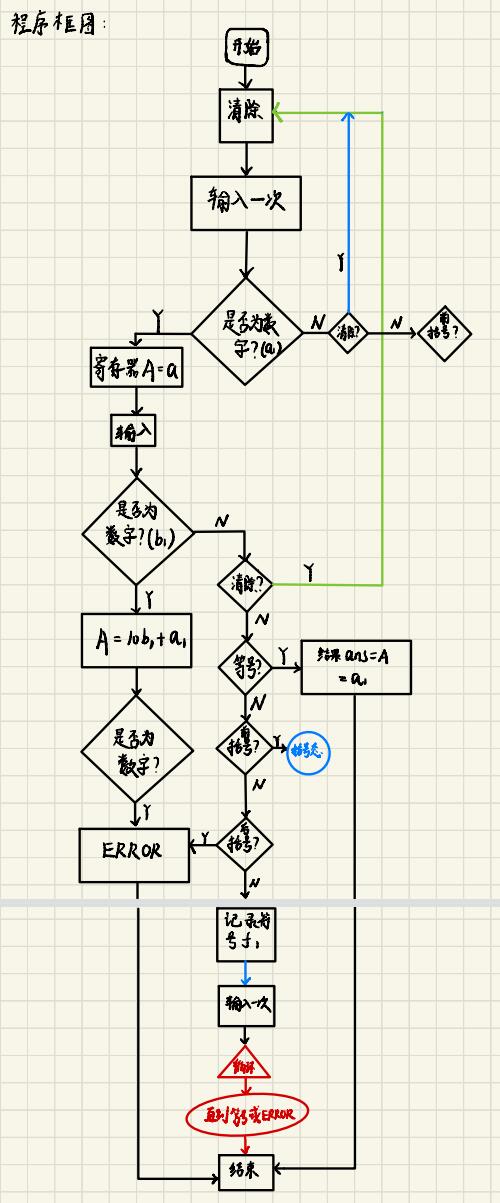

开始时笔者并没有将录入和识别模块区分开,而是先进行了整体实现流程的分析,整理出了如下框图:

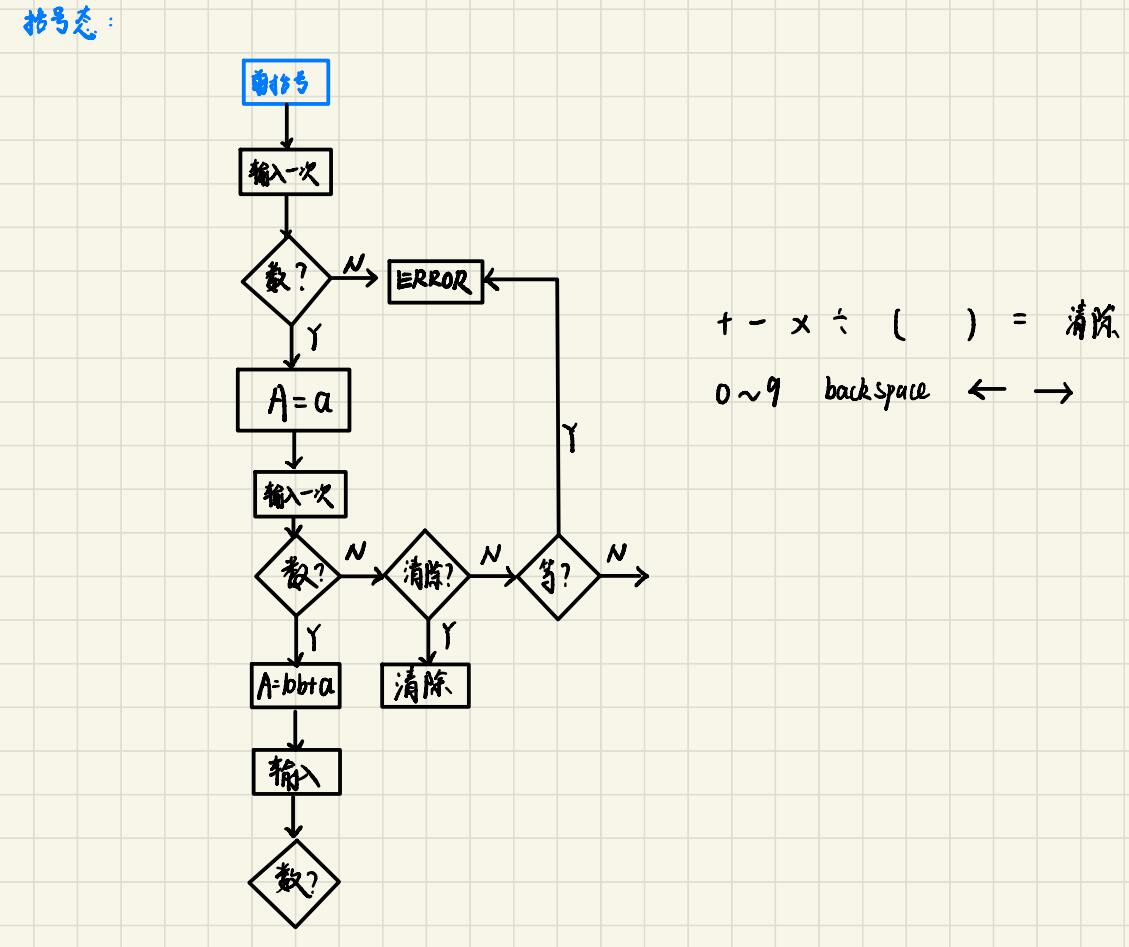

该框图的思路是,首先规定每个操作数上限为两位数,然后每次执行输入,则进行判断,如果是清零则回到初始状态;如果是数字则进行组合,如输入依次为7、1,那么存入寄存器变量A=7*10+1=71;如果是运算符则记录该运算符并重新进入读取输入状态;如果是括号则进入括号状态,括号状态如上图所示,实际上就是重复之前的判断过程。然后重复执行上述过程,直到读到等于号为止。

该过程相当于前文所述的录入和识别模块同时进行,但深入思考后会发现,该思路仅对于形如12+52*76/62之类没有括号或只有极少括号的算式比较适用,一旦有多个括号,就容易陷入逻辑混乱,而且代码的编写难度也会大大增加,不但难以执行之后的优先级判断,更难以进行输入合法性的判别,因而不能满足需求。

于是经过后续思考,笔者将上述过程分割为了录入模块和识别模块两个部分,分别执行录入字符串和识别合法算式的功能,这一思路在后续实践过程被证明是合理可行的。

以上便是此计算器项目开发流程的第一篇记录,后续将对各个模块的编写细节进行深入阐述。

这篇文章同时也是笔者的第一篇blog,因此可能编辑手法不熟练,语言逻辑不清晰,行文思路不明了,希望能在以后的撰写过程中慢慢进步(〜 ̄△ ̄)〜

——洩矢诹团子 2023.5.13