组成原理(七)IO系统

第七章 IO系统

7.1 IO系统基本概念

-

IO设备编址方式

(1)统一编址 : 和主存统一编址

(2)不统一编址 : 有专门的IO指令 -

设备选址

用设备选择电路识别是否被选中 -

传送方式:串行和并行

-

联络方式:

(1)立即响应

(2)异步工作采用应答信号

并行:![image_1atqbcuublfo1uvl1vmd1om03r49.png-5.7kB]()

串行:想象网络传输的包

(3)同步工作采用同步时标 -

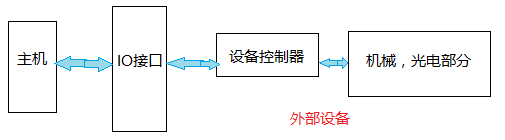

IO设备与主机的连接方式

(1)辐射式连接:每台设备都有一套控制线和一组信号线。不便于增删设备

![image_1atqbodvc19st63d1v40186djd3m.png-5kB]()

(2)总线连接:便于增删设备 -

IO设备分类

(1)人机交互设备:键盘鼠标

(2)计算机信息存储设备:磁盘光盘

(3)机机通信设备:网络传输

![image_1atqe8jcdsv31r2d1cpkgjd1elh1t.png-7.3kB]()

7.2 CPU对IO设备的控制

-

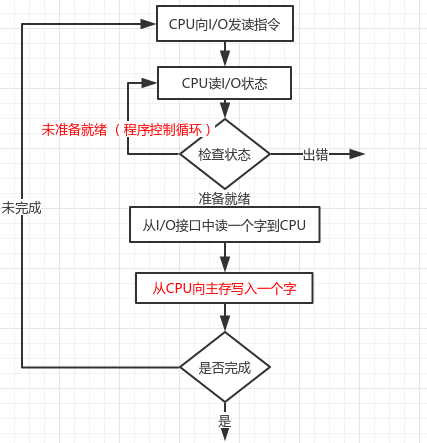

程序查询方式

(1)由软件控制查询IO设备的状态,只要设备没准备好,CPU就会意志询问状态

(2)每次只能传输一个字,继续传输CPU就要走下一个IO询问

(3)踏步等待,串行传输,大量浪费CPU时间

![image_1atqcj49h1hdug3e152m1k4s1oe013.png-30.6kB]()

-

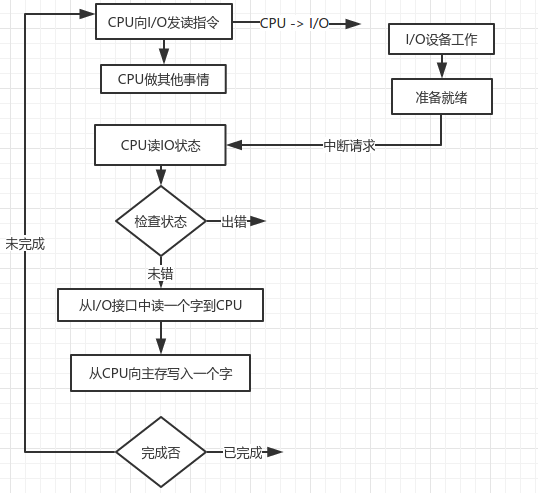

程序中断方式

(1)CPU只发出IO请求,启动设备,然后继续执行其他工作。IO设备传输数据到缓冲寄存器中,存满则对CPU发出中断请求,请求把数据传输到CPU.

(2)IO操作和CPU的其他工作是并行进行的。没有踏步等待,IO传输开始会中断现行程序

![image_1atqdpb4pin61aicnqsv181ck61g.png-36.8kB]()

(3)中断服务程序,解决中断酸发生的问题。(保留中断前程序执行的现场,回复中断后程序执行的现场)

(4)引起中断的方式

人为设置的中断:转管指令

程序性故障:溢出,操作码不能识别

硬件故障

I/O设备

外部事件用键盘中断现行程序

(5)中断系统需要解决的问题

各中断源如何向CPU提出中断请求

各中断源同时提出中断请求怎么办

CPU什么条件,什么时间,以什么方式响应中断

如何保护现场

如何寻找入口地址

如何恢复现场,如何返回

处理中断的过程又出现新的中断怎么办?

(6)中断响应的条件

中断源提出中断请求

中断未被屏蔽

中断源具有较高的优先级

CPU允许中断

一条指令执行完毕

没有更高级的中断服务程序正在执行

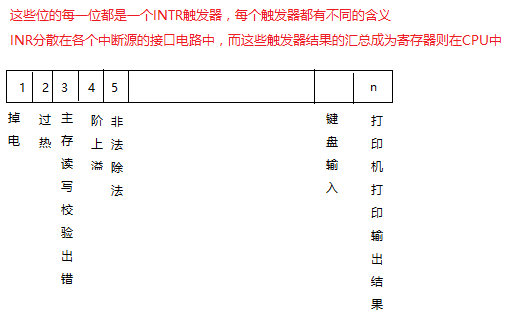

(7)中断请求标记和中断判优逻辑

中断请求标记:INTR。INTR是一个中断请求标记触发器,多个INTR触发器组成一个中断请求寄存器。:

![image_1atsjsu6kffhn9phg51n7n1peqm.png-19.9kB]()

(a)硬件实现排队器(进行中断判优)

分散在各个中断源的接口电路中,形成链式排队器

![image_1atskoeo11t8oqot142kt49ep720.png-14.1kB]()

(b)软件实现:按照优先级的顺序一次查询这些设备是否有请求

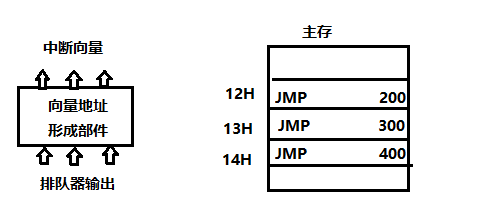

(8)中断服务程序的寻址

硬件向量法:

把上面排队器的输出接入到乡里那个地址形成部件,输出一个主存地址。这个地址上的内容是提前服务程序

排队器的输出又称”向量地址“,向量地址形成部件输出的物理地址又称”中断服务程序的入口地址“

![image_1atsl9jl12c355e1ksq1iptqtb2t.png-9.7kB]()

(8)中断处理过程:

(a)执行中断隐指令:

硬件关中断:

保存断点:保存当前程序断点PC.到特定地址(0号地址),断点进栈

寻找中断服务程序入口地址:向量地址->PC(硬件向量法)

中断服务程序入口地址M -> PC (软件查询法)

(b)转入中断服务程序:

保护现场:保护CPU的主要状态,PCB保存等。通用寄存器入栈保存

开中断:为了响应其它优先级更高的中断请求。另外在小中断服务程序执行完毕后,再次响应

中断处理。

结尾部分:关中断,以防止在恢复现场的过程中被新的中断打断。

恢复现场

开放中断

中断返回

【注】:保护现场和恢复现场只是一半指令的叠加,例如PC值入栈等操作。这些操作计算并不能意识到是他个数的操作,所以要先关闭中断,在进行保存和回复操作.

(9)中断屏蔽技术

(a)多重中断的概念:在执行中断服务程序的时候,该程序被优先级更高的中断请求中断。前提是先开中断

(b)屏蔽技术 :

I. 中断的优先级是硬件电路实现的,所谓屏蔽,就是在每个电路上,加上mask掩码电路。

ii. 通过设置mask掩码电路的值,和原中断优先级的判断进行与操作,来对中断进行屏蔽。

iii. (因此,mask值为1不进行屏蔽,为0进行屏蔽)

V. 中断屏蔽字的编码:把所有中断操作列出01序列,优先级高的位设置为0。eg:中断屏蔽字为A:1111,B:0100,C:0110,D:0111。中断优先级为:ADCB(0的个数依次增多)

-

DMA方式:

(1)概念:

(a)在数据准备阶段,CPU与外设并行工作。数据传输阶段,DMA方式在外设和主存之间开辟一条”直接数据通道“,数据不再经CPU转存

(b)DMA是纯硬件方式进行成组信息传送的IO方式

(c)因为数据不再经CPU转存,所以也就不会有CPU保护恢复现场的操作,因此,DMA也称数据直接存储

(2)总线征用方式:因为CPU和DMA控制器都能向总线传输数据,所以会导致总线冲突

(a)停止CPU访问主存

(b)DMA与CPU交替访问主存

(c)周期挪用

(3)DMA传送过程

(a)预处理:由CPU完成一些准备工作。测试IO设备状态,启动设备等。当IO设备准备好发生的数据或接受的数据后,设备向DMA控制器发送DMA请求,然后DMA控制器向CPU发送总线请求

(b)数据传送:完全有DMA控制器协调主存和外设进行传输数据

(c)后处理:当数据传输完毕,DMA控制器向CPU发送中断请求,CPU执行中断服务程序校验传输数据是否准确,是否需要继续传输其他块等

【注】:DMA方式,只有预处理和后处理需要CPU进行干预。

DMA和CPU同时向主存写入数据时,DMA优先级高于CPU。先让DMA写入数据

不竞争的情况下,CPU在执行完指令后,会空出一个存储周期,用于DMA中断

7.3 输入输出设备

-

输入设备

(1)键盘:将此键翻译成ASCII码(编码键盘) -

输出设备

(1)显示器:

分辨率:显示器所能显示的像素个数

灰度级:像素点的亮暗差别(黑白)颜色。每个像素对应的舒心存储器的位数

刷新:反复不断的扫面整个屏幕

刷新存储器:容量 = 分辨率*灰度级 -

外存储器:硬盘

(1)按序存储,不能随机存储

(2)存储密度:

道密度:沿磁盘半径方向单位长度上的磁道数。单位是道/英寸

位密度:磁道单位长度上能记录的二进制字节数。单位是位/英寸

面密度:位密度和道密度的乘积,单位是位/平方英寸

![image_1atsejm0mkun1drbbkd12dd3tr9.png-14.3kB]()

(3)磁盘总的平均存取时间

存取时间\(T_a\):存取时间是指从发出读写命令后,磁头从某一个起始位置移动到新的记录位置,到开始从盘面读出或写入信息加上传送数据所需要的时间。

平均找道时间\(T_s\):将磁头移动到所要求的磁道上所需的时间(磁臂移动到哪个同心圆)

平均等待时间\(\frac{1}{2r}\):在同心圆上,移动到哪个圆弧段。(用磁盘旋转一周所需时间的一半)

数据传输时间\(\frac{b}{rN}\):磁盘存储器在单位时间内向主机传送的字节数。

设磁盘转速为r转/秒,每条磁道容量为N个字节,数据传输率为\(D_r = rN\)字节/秒

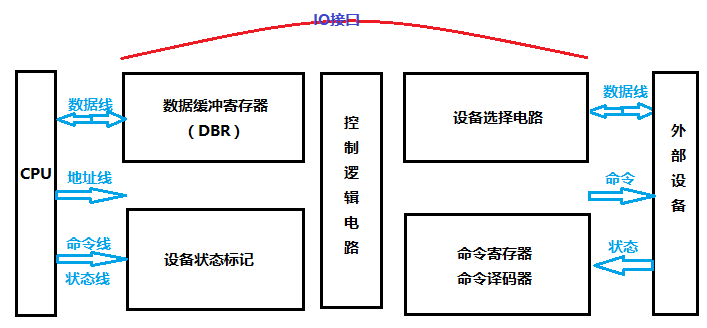

7.4 IO接口

-

IO接口又称作IO控制器,是主机和外设之间的交接面。用来实现主机和外设质检的信息交互。主机和外设的工作方式和工作速度具有很大差异,接口正是为了解决这些差异而出现的

-

IO接口的功能

(1)实现主机和外设的通信联络控制

(2)进行地址译码和设备选择:把CPU传来的地址号转换为制定设备

(3)实现数据缓冲

(4)电平信号转换:外社和主机的电平信号不同,要通过转换

(5)传送控制命令和状态信息:接收CPU传来的启动设备命令,和向CPU传递设备准备就绪信号 -

接口的逻辑电路

(1)CPU同外设之间的信息传送实质是对接口中某些寄存器(端口)进行读写。eg:传送数据就是对DBR读写

(2)内部接口:与系统总线相连,实质上是与内存,CPU相连。数据传输方式只能是并行传输

外部接口:外部接口通过接口电缆和外设相连,外部接口的数据传输方式是串行传输。

因此,接口要有串并转换功能

![image_1atstr2bfac2qon1qe370j1tfg3a.png-25.8kB]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号