上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来。生成IP核后打开example design,先看看工程中包含的文件结构。

顶层文件下包含了gtp ip核系统顶层文件、frame_gen以及frame_check三类模块。frame_gen和frame_check用于测试过程中的数据包产生和接收检测(由于我在配置IP核时使能了两个通道,因此工程中有两组frame_gen和frame_check模块),gen模块读发送样式,check模块则将接收到数据与本地存储样式对比,从而判断数据传输是否正确。下面截取一段gen模块内代码:

发现gen模块是通过系统函数$readmem读取gt_rom_init_tx.dat文件来初始化rom,发送数据则直接从rom中读取。虽然$readmem和initial是不可综合语句,但其功能与.mif文件初始化ROM IP核是类似的。check模块与gen模块类似,但有一点比较值得借鉴。

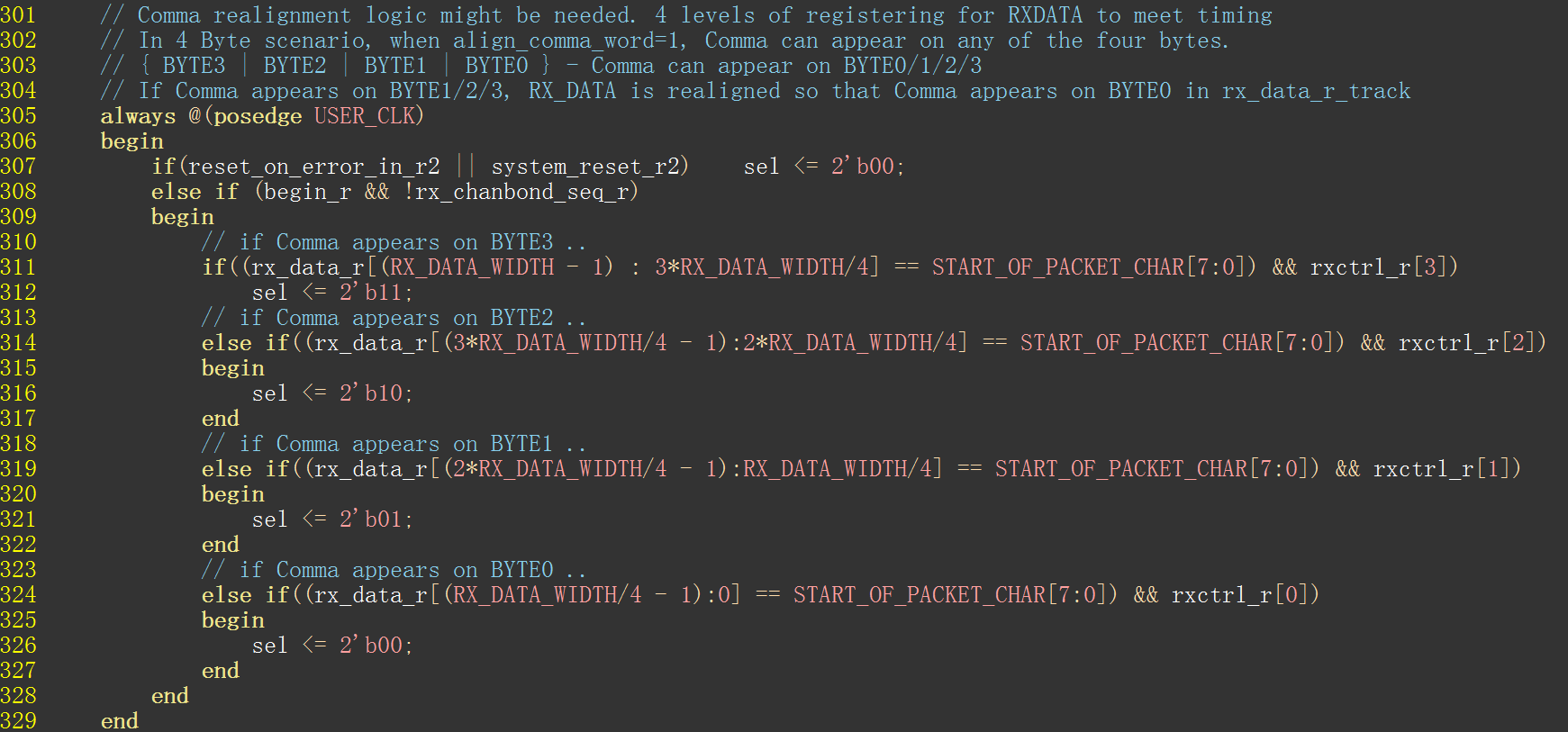

根据上边的注释可以看出,这个IP核在使用32bit用户数据位宽时,会发生错位现象。因此发送数据时所有comma码要放在32bit数据四个字节的同一字节中,最常见的是均放在最低字节,这样接收端可以根据控制字指示信号为1的位置找出错位情况,进而读数据进行重新对齐。比如当rxctrl == 4'b1000,则错误情况和重对齐方式如下:

d0'代表上一个数据的最低字节部分。其他错位情况的重对齐方式同理,现在看下check模块中根据sel信号对接收数据重对齐的逻辑。

可以看出重对齐方式与刚才讲的方法一致。因此当测试完毕后,去除frame_gen和frame_check模块并将gt数据端口开放到顶层后,接收端用户侧也要有类似的逻辑防止数据错位。

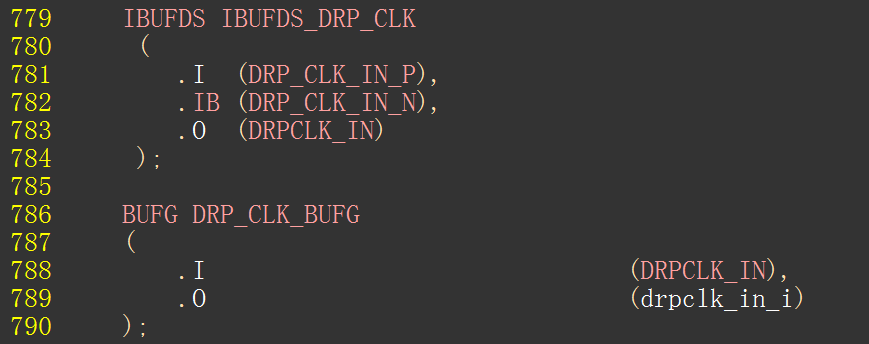

再来看下顶层文件中关于原语的使用:

IBUFDS是差分信号输入缓冲器,用来将差分信号变为单端信号。而BUFG是全局缓冲,其输出到达FPGA内部CLB IOB RAM的时钟延迟和抖动是最小的,从而使系统工作稳定。

最后,为保证最基本的通信功能,还需做三件事:

1. 去除gen和check逻辑块,并将用户数据端口开放到工程顶层;

2. 接收端用户侧例化数据重对齐模块保证接收正确;

3. 例化PLL产生100MHz时钟信号作为GTP子系统工作时钟;

浙公网安备 33010602011771号

浙公网安备 33010602011771号