<DC guide ---6>

前面说了怎么 get_* ,下面就是怎么把 约束加载到指定位置上。

Specifying an Area Constraint

set_area_max 245000

把最大面积约束,自动的施加在current_design上。 一般xxxx的单位,有可能是与非门的个数或者是晶体管数目、或者是mm2、 um2等概念、

这个要看具体的工艺库.DC没有信息能反馈单位,

Specifying Setup-Timing Constraints

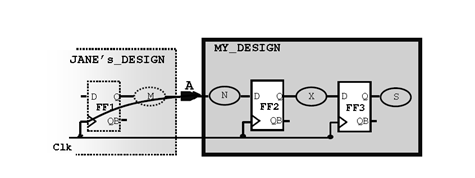

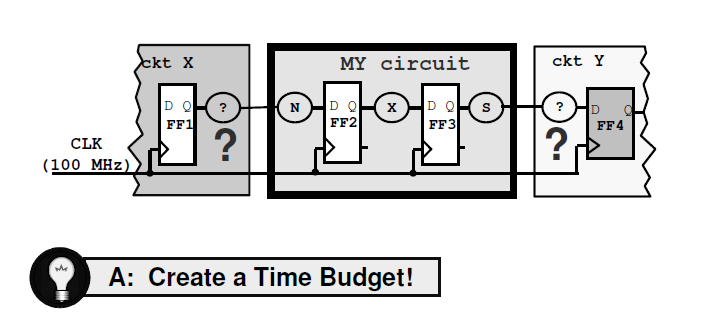

我和JANE、JOE一起合作一个项目,我负责中间的那一块电路。理论上像上图一样。 该怎么约束?约束什么?

我们知道了寄存器自己本身有setup_time、holdtime ,即D要提前时钟一些,提前稳定好。 时钟上升沿之后,D应该保持稳定一段,以便正确打入寄存器。

对于我们的小模块来说,都假设从0时刻开始. 假设时钟是100M , 输入信号经过组合逻辑N, 耗时了t1,那么应该保证 t1< 10ns -setup 。即D提前一段时间稳定。

两个寄存器之间的组合逻辑x最大是多少?

假设时钟是100M, 而组合逻辑是 15ns, 当FF2输出一个信号, 需要经过15ns才传回D_FF3, 显然FF3会抓到一个中间状态,这个状态有正在跳转,这个即使综合器也无法

确保,在中间状态维持一段时间稳定. 因此,要把这个组合逻辑x约束在一个Period内.

两个寄存器之间的组合逻辑x最小是多少?

实际应用中,我们经常会中间没有组合逻辑.那为什么要提这个概念呢?

对于两个寄存器来说,在同一节拍, FF2的数据输出,如果马上跳变了,会不会恰好发生在FF3的hold_time时间内呢?如果发生了,显然会引起亚稳态.

所以说: FF2的单bit数据,跳变后,经过一个组合逻辑x, 安全度过FF3的hold_time之后,才最终完成组合逻辑x。这样就能保证FF3的hold_time了。

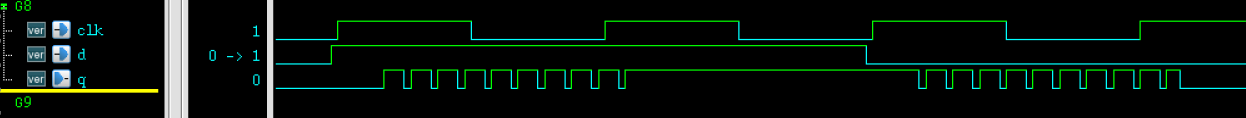

下面是一个我用与非门答的 寄存器电路,仿真了下 关于setup\hold期间跳变的现象。

未满足setup的情况:

未满足hold的情况:

可以看出,q输出端确实会有震荡的现象。这也是我们为什么要关心这个setup/hold的原因。

怎么才能告诉DC,我所允许组合逻辑x的最大最小值? 我如果是直接告诉DC.那么是不是所有路径都得告诉DC才能?

显然是太啰嗦的,我们只需要告诉DC 时钟的周期.DC自己就能算出来,(工艺库DFF的setup/hold时间固定),

create_clock

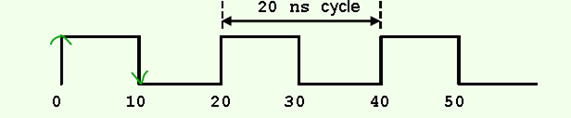

Creat_clock –name xxx -period 20 –waveform { rise nege} [get_* ]

先get_*获得某个pin、prot,然后起名xxx,定义它的周期是20,-waveform决定了时钟的相位。 -add选项后面再讲。

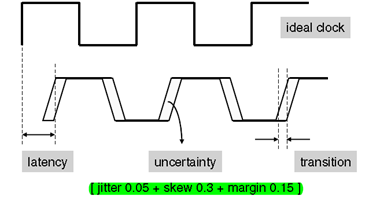

当然了这是一个理想的时钟, 绝对的周期,绝对的占空比. 但在现实中是不存在的, 所以我们要尽量的描述的和现实中的一样.

(1) 时钟占空比40%,很难精确. (2) 时钟信号从0-1-0的跳变不是瞬时完成的,有一个过程。

(3) 时钟到达DFF2和DFF3的时间,有可能受到布线长度等影响,不是严格对齐的。

(4) 时钟存在jilter,比如时钟的上升沿,时而超前、时而滞后的偏移称为时钟抖动

怎么样,把这几个方面也考虑进去,才能说 大致构造一个真实的时钟模型.

Set_clock_uncertainty: 时钟的uncertainty = skew +jitter

时钟skew是表示: 时钟到达每个寄存器的时刻不是严格对齐的,受到布局布线影响,所以我们需要提前把这些因素考虑进来。

时钟Jitter是表示 : 由于物理热运动,时钟的沿跳沿,会时而提前时而滞后的自然现象。

Clock_uncertainty主要考虑的是skew,顺带着把jitter加进来。

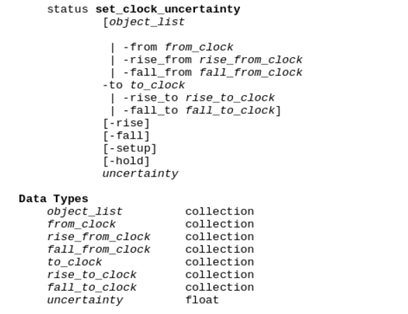

仔细看语法:

-rise –fall选项已经废弃了。

-setup : 是说该uncertainty值只用在setup时序分析上。

-hold : 是说该 uncertainty值只用在hold时序分析上。 (后面会说 uncertainty的值到底会怎么影响 setup\hold分析)

上面的例子,就是说:在分析CLK路径 的setup时候,需要考虑unvertainty = 0.65

在分析CLK路径 的hold时候,此时unvertainty = 0.45

-from CLK1 -to/-rise_to/-fall_to CLK2

-rise_from CLK1 -to/-rise_to/-fall_to CLK2

-fall_from CLK1 -to/-rise_to/-fall_to CLK2 还没弄清楚具体什么意思。后面用到了再学习。慢慢来

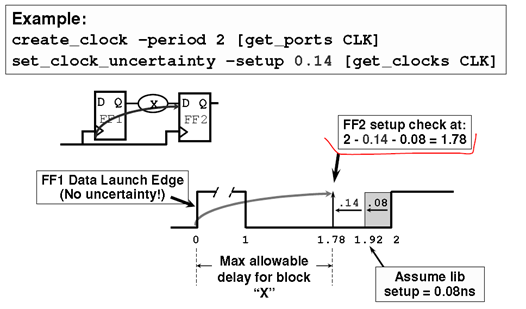

看一下设置之后的效果:

时钟是2ns,在分析setup时候,因为设置clock_uncertainty setup = 0.14 。即上升沿有可能提前或滞后0.14ns。

如果是滞后0.14,相当于 放松了约束。如果是提前0.14,那么组合逻辑x的最大延迟就变相严谨了。

DC要保证所有情况,故只会考虑提前0.14ns的情况。 2-0.14-0.08-delay(FF1) = max( x )

故而对组合逻辑x的约束更加严厉了。这符合我们的预期目的。

set_clock_latency

时钟从晶体出来,到CLK_Port,耗时称为source_latency.

从CLK_port,再到寄存器,耗时称为 network_latency.

这两个值,都通过set_clock_latency

感觉这个值,对于MY_DESIGN内的综合,没有起到约束作用。但是呢或许是模块键的组合逻辑会有帮助。

set_clock_transition

时钟从来都是,瞬间完成跳变的。当时钟电压值,达到80%时,认识CLK为高。所以综合时,需呀把这个因素考虑进去。

一般可以用set_clock_transition设置最大最小值。比如DFF2最慢变,DFF3最快变,这样setup就又严谨了一丢丢。

通过这几个命令: 我们把理想的idea clock变成了较为真实的时钟。

继续回到MY_DESIGN上:

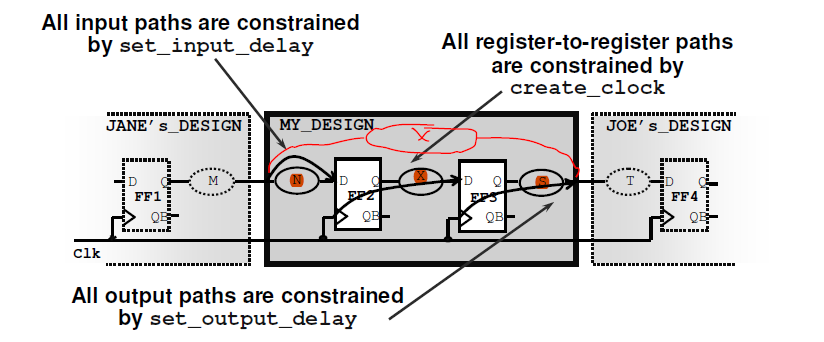

我们通过creat_clock以及配置波动参数,能够让DC明白,组合逻辑X的最大最小延迟。那对于组合逻辑N,能使用一样的约束吗?

我们通过补全,JANE’s DESIGN,可以把M+N看作一个整体,这样就跟组合逻辑X一样了。但是现实中,我们经常只综合自己的模块,并不知道

组合逻辑M。怎么能虚构一个信息,让它替代FF1_cell + M的时间 ?

set_input_delay :

指定 port_pin,相对于某个信号、某个时钟,延迟多久。

我们一般用:

Set_input_delay -max 0.6 –clock [get_clock*] [get_input *]

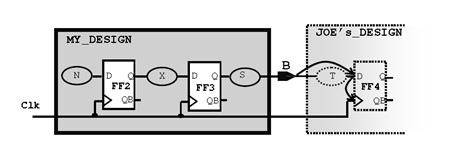

set_OUT_delay :

需要理清楚一点: set_output_delay: 是模拟 JOE模块的。

因为我们告诉DC所有的信息,都是为了让他能计算出组合逻辑S的范围。

set_output_delay 值是 = 端口B---到FF4的时间。

比如 set_output_delay 4 ,意味着 组合逻辑只有 6ns的延迟上限。

为了方便JOE综合她的模块,我们需要提供我们的组合逻辑S的延迟信息。

其实这也是,为什么很多代码风格,要求输出信号全部都是寄存器输出的原因。环境独立,不受其他的模块影响。

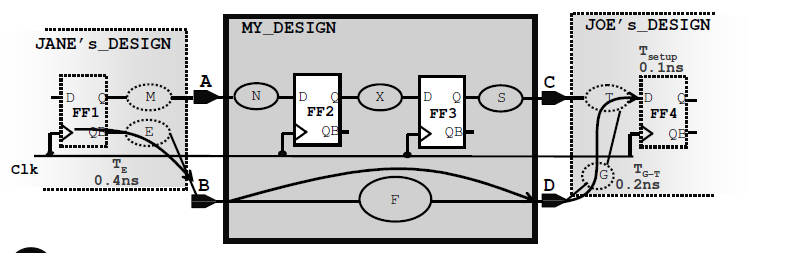

纯组合逻辑约束

讨论下这种情况,约束组合逻辑F的时候,需要考虑B的输入delay时间。需要告诉JOE关于D的输出delay

从图上,可以看到寄存器时刻----到输入口B,总共耗时0.4ns。

FF4需要至少提前0.3ns,才能确保setu. 所以组合逻辑的最大延迟为 2-0.4-0.3 = 1.3ns

再考虑一种情况:

这个时候,MY_DESIGN是纯组合电路。我们的set_input_delay、set_output_delay都是相对于时钟上升沿时刻来说的。

这个时候没有时钟做参考怎么办 ?

我们可以自己虚拟一个跟CLK一样的时钟。 creat_clock -name my_clk -period 2 .剩下的事给之前一样处理。

综合以上,如果我们知道input_delay的时间,我们就能够约束 DFF之间的组合逻辑、input----DFF的组合逻辑、DFF--output的组合逻辑、Input---Output的组合逻辑。

这也是我们为什么能够把时序路径划分成 start_point(input\DFF_clk)到endpoint(output\DFF_in)的原因。

假如我们不知道JANE'的输出延迟信息。我们的input---DFF、Input----Output的组合逻辑块就没有办法保证了。

这种情况下:我们可以去直接问JANE、或者我们进行一个预估。预估的原则是什么?

假设: 三个设计,都做一样的约束处理: 设置set_output_delay 60% of clk 。那么留给我们组合逻辑S的只有40%时间上限了。

同时 set_input_delay 60% of clk ,对于我们的组合逻辑N而言,只有40%的最大上限。

如果三个模块都这样设计: 第一个的?组合逻辑,只有40%的上限,我们的N也只有40的上限,这样就能确保有20%的冗余时间足够保证设计可靠性。

这个原则适用于所有的 小模块的综合。

现在我们可以说:我们基本能能够约束 DFF之间的组合逻辑、input----DFF的组合逻辑、DFF--output的组合逻辑、Input---Output的组合逻辑。

这也是我们为什么能够把时序路径划分成 start_point(input\DFF_clk)到endpoint(output\DFF_in)的原因。

组合逻辑N、X、S,以及纯组合逻辑Y都能有效的进行约束了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号