What is Fermi?(5)

GPU最小执行单位Core

CUDA核心架构解析

在最新的GF100当中,每个流处理器(NVIDIA称之为CUDA Core,等同于之前的流处理器,为了方便读者理解,我们仍然沿用流处理器的名称)仍然采用标量架构(也就是1D架构),能够对各种向量尺寸数据实现全速运行(例如Z缓冲区数据的1D向量可以由单个Core完成,而对于纹理存取的2D向量则可以通过两个Core合作完成),而不会出现部分流处理器在某一时钟周期内无法工作的情况。这一点实际上NVIDIA从最早的G80当中就已经开始采用,这也是NVIDIA在核心架构设计上与ATI出入最大的地方。

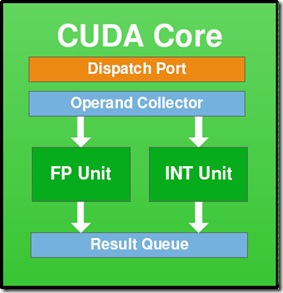

在每个流处理器当中,包含有Dispatch Port(分派端口)、Operand Collector(运算对象收集器)、FP Unit(浮点运算单元)、INT Unit(整数算术逻辑单元)以及Result Queue(结果队列)几大部分。

每个流处理器当中,均能够支持最新的IEEE754-2008浮点标准,也就是说,它能够支持单精度以及双精度的乘法(MAD)、加法(FMA)指令。那么IEEE754-2008的优势究竟在哪里?在之前的算法当中,每条MAD或FMA计算指令完成后都会对结果进行四舍五入,然后再继续进行计算,对计算结果再次四舍五入,导致最终结果很有可能会造成较大的数据偏差。而最新的IEEE754-2008浮点标准则规定,只有在每条FMA指令全部计算完成后,才会进行一次四舍五入,因此计算结果的精度将会大幅提升。

另外,在GF100中,全新设计的整数ALU支持所有指令全32位精度,符合标准编程语言的要求。整数ALU还经过了优化,可有效支持64位以及更高精度的运算。它支持各种指令,其中包括Boolean、移位、移动、比较、转换、位字段提取、位反 向插入(Bit-reverse Insert)以及种群统计。