Stratix® 10 SX SoC FPGA结构图— 1SX040HH3F35E2LG 1SX040HH3F35E3XG 1SX040HH3F35I1VG 1SX040HH3F35I2LG 1SX040HH3F35I3XG功能

Stratix® 10 SX SoC FPGA结构图

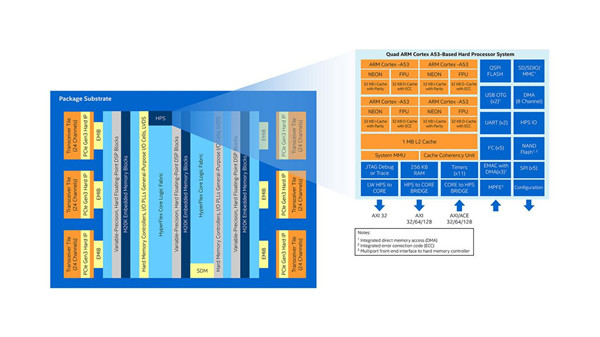

英特尔® Stratix® 10 SoC FPGA 结合了四核 ARM* Cortex*-A53 MPCore* 硬处理器系统与革命性的英特尔® Hyperflex™ FPGA 架构,为嵌入式应用提供了必要的嵌入式性能、功效、密度和系统集成。

针对数百万个逻辑元件 (LE) FPGA 设计优化的全新引擎可显著降低设计迭代次数,英特尔® Stratix® 10 SoC FPGA 虚拟平台支持早期软件开发和认证,基于 C 语言的设计输入(使用面向 OpenCL™ 的英特尔® FPGA SDK)提供了一个易于在 SoC FPGA 上实现的设计环境。借助采用 ARM* Development Studio 5* (DS-5*) 英特尔® SoC FPGA 版工具包的英特尔® FPGA SoC FPGA 嵌入式开发套件 (EDS),开展异构调试、分析和整体芯片可视化。

产品:

1SX040HH3F35E2LG - SRGS7

1SX040HH3F35E3XG - SRGSB

1SX040HH3F35I1VG - SRGP8

1SX040HH3F35I2LG - SRGP9

1SX040HH3F35I3XG - SRGPC

——明佳达供求Stratix® 10 SoC FPGA

规格:

逻辑元素(LE):378000

自适应逻辑模块 (ALM):128160

自适应逻辑模块 (ALM) 寄存器:512640

结构和 I/O 相锁环路 (PLL):8

最大嵌入式内存:32 Mb

数字信号处理 (DSP) 区块:648

数字信号处理 (DSP) 格式:乘累加,可变精度,定点(硬IP),浮点(硬IP)

硬处理器系统 (HPS):四核64位ARM* Cortex*-A53

硬内存控制器:是

外部内存接口 (EMIF):DDR4, DDR3, DDR2, DDR, QDR II, QDR II+, RLDRAM II, RLDRAM 3, HMC, MoSys

I/O 数量:392

封装:1152-FBGA

功能:

最高 1.5 GHz 的四核 ARM Cortex-A53 MPCore* 处理器集群

矢量 (VFPU) 单精度和双精度,面向每颗处理器的 ARM Neon* 媒体处理引擎

带奇偶校验的 32 KB 一级指令高速缓存,带纠错码 (ECC) 的 32 KB 一级数据高速缓存

带 ECC 的 1 MB KB 共享二级高速缓存

256 KB 片上 RAM

系统内存管理单元支持统一的内存模式,将硬件虚拟化扩展为在 FPGA 结构中实施的外围设备。

提供单向 (I/O) 一致性,使主 CCU 能够查看 ARM* Cortex-A53 MPCore CPU 的一致内存

8 通道直接内存访问 (DMA)

3 个 配有集成 DMA 的 10/100/1000 EMAC

两个配有集成 DMA 的 USB OTG

2 个 UART 16550(兼容)

4 个 SPI

5 个 I2C

1 个带有 DMA 和 CE-ATA 支持的 eMMC 4.5

1 个 ONFI 1.0 或更高版本 8 位和 16 位支持

最高 48 个软件可编程 GPIO

4 个通用计时器,4 个监视计时器

包含内存映射控制和状态寄存器与逻辑,以控制系统级功能和其它 HPS 模块

在 HPS 和 FPGA 结构中基于来自源的重设请求重新设置信号,并将软件写入模块重设控制寄存器

提供软件可编程时钟控制,以配置在 HPS 中生成的全部时钟

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

浙公网安备 33010602011771号

浙公网安备 33010602011771号