TMS320C55x DSP CPU内核与TMS320VC5509AGBBR、TMS320VC5509AZAYR、TMS320VC5509APGE特性

TMS320VC5509A定点数字信号处理器(DSP)基于TMS320C55x DSP一代CPU处理器内核。C55x DSP架构通过提高并行性和专注于降低功耗来实现高性能和低功耗。CPU支持内部总线结构,该结构由一条程序总线、三条数据读总线、两条数据写总线和专用于外设和DMA活动的附加总线组成。这些总线能够在一个周期内执行多达三次数据读取和两次数据写入。并行地,DMA控制器每个周期最多可以执行两次数据传输,与CPU活动无关。

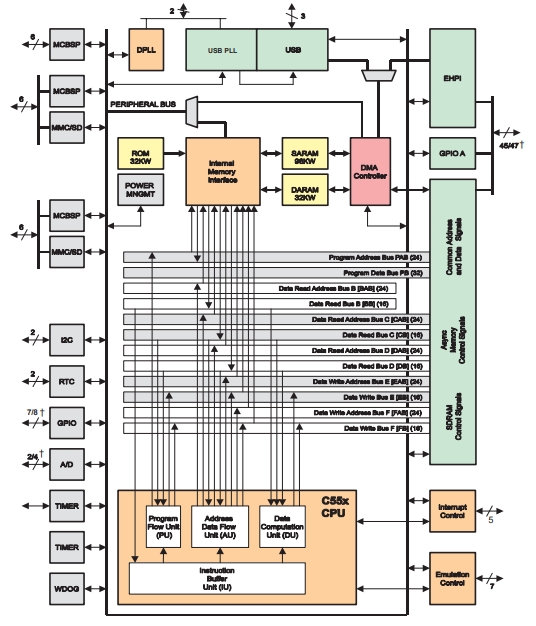

框图

1、TMS320C55x的基本结构:

TMS320C55x DSP由多个核心组件构成,包括中央处理器(CPU)、程序存储器、数据存储器、外围接口和专用硬件加速器。CPU采用改进的哈佛架构,拥有独立的程序和数据总线,以提高数据处理速度。此外,还包括一个高效的算术逻辑单元(ALU)和浮点运算单元(FPU),支持定点和浮点运算。

2. CPU体系结构:

C55x CPU的体系结构基于增强型5级指令流水线,这使得处理器能同时执行多种操作,显著提升了处理效率。流水线包括取指、解码、执行、访存和写回五个阶段。这种设计允许指令在不同的阶段并行处理,减少了等待时间,提高了吞吐量。

3、TMS320VC5509A的主要特性:

TMS320VC5509A是C55x系列的一个具体型号,具有以下特点:

- 高性能:提供高达333MHz的运行频率,能够执行复杂的计算任务。

- 低功耗:通过优化的工艺技术实现低能耗,适合电池供电或节能应用。

- 扩展性:具备丰富的外围接口,如串行端口、GPIO、定时器和模拟外设,便于与其他系统集成。

- 内置模拟功能:集成模数转换器(ADC)和数模转换器(DAC),可直接处理模拟信号。

- 强大的存储支持:配备大容量的片上RAM和ROM,以及扩展存储接口。

产品:

TMS320VC5509AGBB

TMS320VC5509AGBBR

TMS320VC5509AZAY

TMS320VC5509AZAYR

TMS320VC5509APGE

——明佳达供求数字信号处理器

特性

高性能、低功耗、定点TMS320C55数字信号处理器

9.26纳秒、6.95纳秒和5纳秒指令周期时间

108、144、200 MHz时钟速率

每个周期执行一/两条指令

双乘法器[每秒高达4亿次乘法累加(MMACS)]

两个算术/逻辑单元(alu)

三条内部数据/操作数读总线和两条内部数据/操作数写总线

128K × 16位片内RAM,包括:

64K字节的双存取RAM (DARAM) 8块4K × 16位

192K字节的单次存取RAM (SARAM) 24块4K × 16位

64K字节的单等待状态片内ROM (32K × 16位)

8M × 16位最大可寻址外部存储器空间(同步DRAM)

16位外部并行总线存储器支持:

外部存储器接口(EMIF ),具有GPIO功能和无缝接口:

异步静态RAM (SRAM)

异步EPROM

同步动态随机存取存储器

具有GPIO功能的16位并行增强型主机端口接口(EHPI)

六个器件功能域的可编程低功耗控制

基于片上扫描的仿真逻辑

片内外设

两个20位定时器

看门狗定时器

六通道直接内存访问(DMA)控制器

三个串行端口支持以下组合:

多达3个多通道缓冲串行端口(McBSPs)

多达2个多媒体/安全数字卡接口

可编程锁相环时钟发生器

七个(LQFP)或八个(BGA)通用I/O (GPIO)引脚和一个通用输出引脚(XF)

USB全速(12 Mbps)从端口支持批量、中断和同步传输

内部集成电路(I2C)多主和从接口

带晶振输入、独立时钟域、独立电源的实时时钟(RTC)

4通道(BGA)或2通道(LQFP) 10位逐次逼近型模数转换器

IEEE标准1149.1(1) (JTAG)边界扫描逻辑

包装:

144引脚薄型四方扁平封装(LQFP) (PGE后缀)

179引脚MicroStar BGA(球栅阵列)(GHH和ZHH后缀)

179引脚无铅MicroStar BGA(球栅阵列)(ZHH后缀)

1.2V 内核(108 MHz),2.7V 至3.6V 输入/输出

1.35V 内核(144 MHz),2.7V 至3.6V 输入/输出

1.6V 内核(200 MHz),2.7V 至3.6V 输入/输出

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

浙公网安备 33010602011771号

浙公网安备 33010602011771号