FPGA与芯片设计差异

FPGA:系统规划->RTL设计->功能仿真->综合->逻辑块映射->布局布线->时序仿真->板级验证与仿真

综合(Synthesis):用EDA工具将RTL设计的代码翻译成物理电路世界的具体电路(AND/OR/NAND gate/Dflipflop),可用的EDA工具有Synopsys的Design Compiler或者Cadence的RTL Compiler. FPGA厂商的EDA工具如Xilinx的Vivado和Alteral的Quartus也可以执行该操作。

验证一般占到整个芯片设计流程时间的60%-70%,目的就是尽可能的对芯片功能进行充分的验证,尽早暴露出问题,解决问题,以保证芯片功能完全正确。

相同点:

1.前后仿真都在数字功能验证工程师的工作范畴之内,且都涉及到验证环境的搭建,需要耗费大量的时间,需要用到的仿真器工具也都一样:Synopsys的VCS;Cadence的NC-Verilog(IUS,早期,较弱)、irun(IES,现在,较强)、xrun(Xcelium,新的);Mentor的Modelsim;

根据执行仿真的不同方法,verilog仿真器可以分为以下3种类型:

① 解释型的仿真器。 解释型仿真器读入Verilog代码,在计算机的内存中生成数据结构,然后解释性地运行仿真,每次运行仿真时,进行一次编译,编译通常很快就可以完成。Cadence公司的Verilog-XL仿真器就是一种解释型的仿真器。

②编译型的仿真器。编译型的仿真器读入Verilog代码,然后把它转换为相应的C代码(或其他编程语言的代码)。接下来,用标准C编译器将该C代码编译成二进制可执行代码。执行这个二进制代码,就可以执行仿真器。编译型的仿真器的编译时间通常比较长,但其执行速度一般来说比解释型的仿真器快。Synopsys公司的VCS仿真器就是一种编译型的仿真器。

③本地编译型的仿真器。本地编译型的仿真器读入Verilog代码,然后把它直接转换成能在指定的机器平台上运行的二进制代码,机器的平台不同,编译的优化和调整过程也不同。这就是说,能在Sun工作站上运行的本地编译仿真器,不能在HP工作站上运行,反之亦然。Cadence公司的NC-Verilog仿真器就是这种本地编译型的仿真器。

前仿真(Per Sim):功能仿真、行为仿真,验证电路在理想环境下的行为和设计构想是否一致,电路功能是否符合Spec和设计要求。

后仿真(Post Sim):也可叫时序仿真,布局布线后仿真,主要针对布局布线之后的网表加入时序分析,对功能正确性进行仿真验证。侧重于关心器件参数以及考虑线的寄生问题,这就是为什么后端环节中需要进行寄生参数提取,因为导线本身就存在电阻和相邻导线之间的互感,耦合电容也会在芯片内部产生信号噪声、串扰和反射,这些效应都会产生信号完整性问题,导致信号电压波动和变化,如果严重的话就会导致信号失真错误,所以会提取寄生参数再次进行分析验证信号完整性问题。

1.解决的问题不同 前仿真主要验证的是功能正确性,而后仿真主要验证的是时序正确性。

2.侧重点不同 侧重于关心器件参数,不考虑电路门延迟与线延迟,没有器件内部逻辑单元和连线的实际延时信息,只是初步验证系统的逻辑功能;

3.流程环节不同 前仿真是在RTL代码设计环节进行,后仿真要在布局布线环节之后进行,布局布线之后,晶体管等各类器件的具体形状、尺寸、相互位置都已经确定了,这表示将来制造出来的芯片结构也就确定了

4.仿真结果不同 前仿真主要分析电路逻辑功能,相比于后仿真来说速度更快,后仿真引入了寄生分布参数的实际电路进行仿真,能够比较好的反映芯片的实际工作情况,是更接近于实际的仿真,消耗时间是要更长的。有时会出现前后仿真结果不一致,差别很大的情况

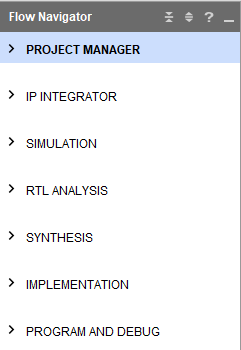

Vivado开发流程

1.Project Manager:项目管理器,对项目参数进行设置,主要功能接口:①添加或创建约束文件、设计文件或文件夹、仿真文件或文件夹 ②Verilog、VHDL、SystemVerilog、XDC以及Debug各类文件的模板浏览③IP库接口

2.IP Intergrator:图形化界面的IP集成器,主要以Block Design的方式进行embedded system design,包括硬核和软核,将需要的软核以及外围的IP添加进去,然后进行适当连线。System外围通用IP有SPI、UART、I2C、DDR3、ETHERNET、GPIO等,对应硬件平台的相应外设接口,这些外设通常在System以IP的形式用AXI连接到软核。还有一些第三方IP或者自建IP,除了和软核相连接的控制类总线AXI总线外,还有一些额外的控制或数据总线。该工具内部布局连线完后检查没有问题后,可以将block design设计文件生成一个wrapper文件,放到RTL工程中使用。将整个RTL工程完成综合、布局布线以及bitstream生成后,导出xsa文件,导入到vitis SDK中,在SDK中开发C工程即可,和一般的C驱动开发类似,SDK用的是eclipse的框架。接口有三个:①创建Block Design,构建带有IP核的框图 ②打开Block Design,打开之前已有的Block Design设计 ③生成Block Design,在创建完Block Design,添加完IP,完成连线后,点击其选项可以生成BD中各IP对应的RTL层次文件,将其完成HDL的封装,在高层次的HDL文件中实例化这个Block设计。注意到右键点击该Block design,有create HDL Wrapper选项,这样可以创建HDL封装,实例化一个更高的层次供外部调用

3.Simulation:仿真,包括行为仿真,综合后仿真以及布局布线后仿真

4.RTL Analysis:RTL分析,将用户的设计输入细化成逻辑电路,对后续工程无直接帮助

5.Synthesis:综合,类似于软件编程中的编译,是把RTL电路用FPGA内部资源实现的过程,会产生综合网表

6.Implemention:实现,把综合网表具体实现的过程,可以理解为将综合后的电路具体映射到FPGA内部资源的过程

7.Program and Debug:下载和调试,将最终实现的电路生成BIT文件或者MCS文件,可下载到进FPGA板卡中,BIT是load进SRAM中,断电易失,MCS是load到FPGA板卡中的FLASH中,上电后会自动载入SRAM运行,可以调试debug

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具