Verilog中信号定义位宽的一些问题

总是被Verilog中信号定义位宽的问题所困扰:

wire[7:0] data1 和 wire[0:7] data2有什么不一样

wire[7:0] data2[3:0]、wire[7:0] data2[0:3]、wire[0:7] data2[3:0]、wire[0:7] data2[0:3]又分别有什么不一样?

今天下定决心要把这个问题弄清楚

写了一段代码放到modelsim里跑:

module test;

wire[7:0] data1;

wire[0:7] data2;

reg[7:0] byte1[3:0];

reg[7:0] byte2[0:3];

reg[0:7] byte3[3:0];

reg[0:7] byte4[0:3];

integer i;

assign data1 = 8'b1001_1100;

assign data2 = 8'b1001_1100;

initial begin

for (i = 0; i<=3; i=i+1) begin

byte1[i] <= i+1;

byte2[i] <= i+1;

byte3[i] <= i+1;

byte4[i] <= i+1;

end

end

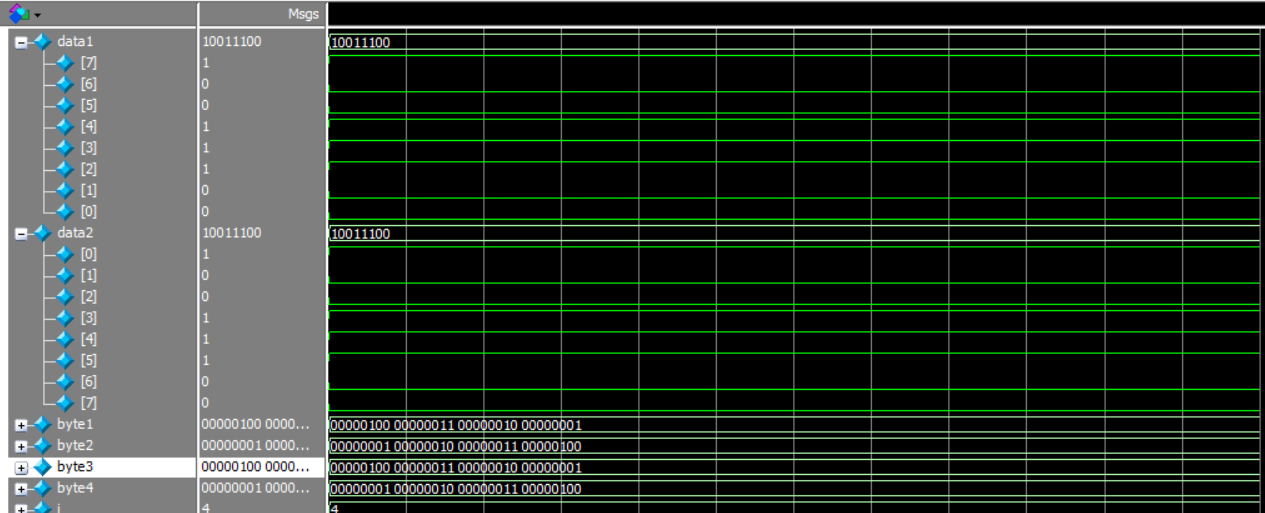

endmodule仿真结果如下:

可以看到data1和data2最后的赋值结果都是一样的,但是注意到最高位和最低位的顺序不一样 data1 最高位是7,最低位是0 ,data2最高位是0 最低位是7 data1[7:0] data2[0:7]

一般的数 二进制下 最左边为最高位,最右边为最低位,如:1001十进制为 9,所以声明信号赋值时习惯写成 wire[3:0] data; assign data = 3'b1001;这样最高位到最低位就对应起来了

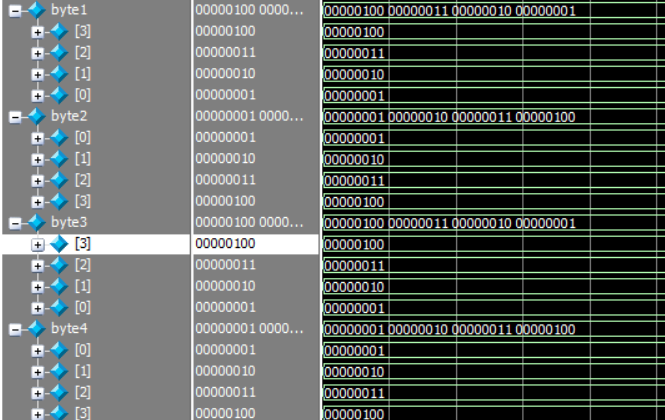

而byte也类似,[7:0] 高位是7,低位是0 [0:7] 高位是0,低位是7,而后面的[3:0]、[0:3]其实相当于是序号

总之,以后一维就统一 声明为 wire[n:0] data, 二维就统一声明为wire[n:0] data[m:0] 这样高位都在左边

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 使用C#创建一个MCP客户端

· ollama系列1:轻松3步本地部署deepseek,普通电脑可用

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 按钮权限的设计及实现