Testbench中的一些小问题

一些基本概念:

UUT: Unit Under Test

DUT:Design Under Test

两者应该是差不多的,只是DUT感觉在SV和UVM中提及比较多,而UUT在Verilog testbench中例化模块时经常提及。

刷HDLBits时,犯了个错误:

`timescale 1ps/1ps

module top_module ();

reg clk;

initial begin

clk = 0;

end

forever begin

#5 clk = ~clk;

end

dut uut

(

.clk(clk)

);

endmodule弄死过不了编译检查,跑去翻书才发现,forever循环语句与always语句的不同之处在于不能独立写在程序中,而必须写在initial块中。

`timescale 1ps/1ps

module top_module ();

reg clk;

initial begin

clk = 0;

forever begin

#5 clk = ~clk;

end

end

dut uut

(

.clk(clk)

);

endmodule这样写就直接过编译了

其实通常用 always #half_period clk = ~clk;或者是在initial块里写 forever #half_period clk = ~clk;就可以了。

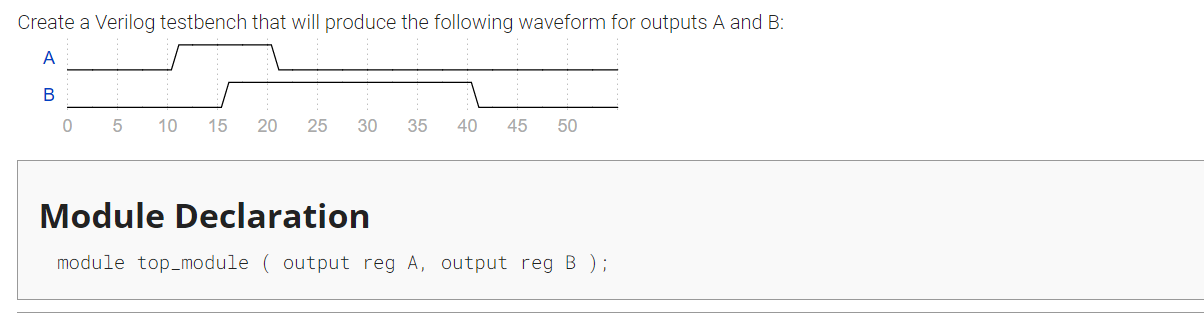

要完成上面A、B的波形输出,看似简单,其实要明白begin-end顺序块和#的延时含义,注意到该模块中#会一直暂停在这里,直达时间过去,才会进行后面的动作

module top_module ( output reg A, output reg B );

// generate input patterns here

initial begin//电路是并行执行的,但是begin-end是顺序块,#会导致一直阻塞在这里,等待完成以后其他部分才会跟着一起动作

A = 0;

B = 0;

#10 A = 1;//经过10 A跳变为1 即 A在0 共10,经历的时间为10

#5 B = 1;//再经过5 B跳变为1 即 B在0 共10 + 5 = 15,经历的时间为15

#5 A = 0;//再经过5 A跳变为0 即 A在1 共 10,经历的时间为15 + 5 = 20(相对于B),也可以是10 + 10 = 20(相对于A)

#20 B = 0; //再经过20 B跳变为0 即 B在1 共 25,经历的时间为20 + 20 = 40(相对于A), 也可以是15 + 25 = 40(相对于B)

end

endmodule其实把A、B分成两个initial块会更直观!因为initial块是独立并行执行的