第七章 ZYNQ-MIZ701 GPIO使用之EMIO

7.0难度系数★☆☆☆☆☆☆

7.1硬件截图

7.1.1 PCB上的位置

7.1.1 PCB上的位置

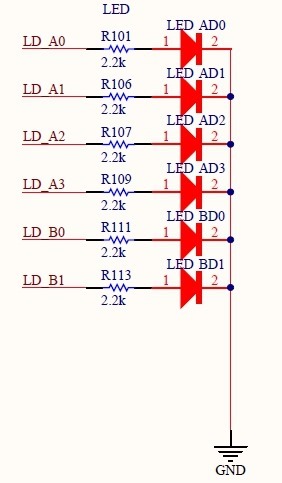

7.2电路分析

本次实验用到的是LD_A0~LD_A3,管脚定义如下表所示。

| LD_A0:F17 LD_A1:J15 LD_A2:G14 LD_A3:D18 |

7.3 EMIO 和MIO的对比介绍

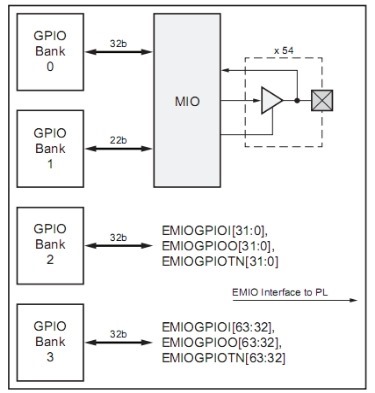

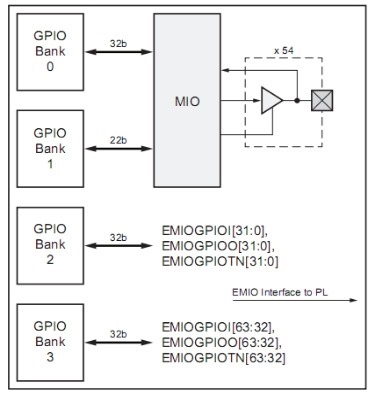

上次讲到MIO的使用,初步熟悉了EDK的使用,这次就来说说EMIO的使用。如你所见zynq的GPIO,分为两种,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)

MIO分配在bank0和bank1直接与PS部分相连,EMIO分配在bank2和接和PL部分相连。除了bank1是22-bit之外,其他的bank都是32-bit。所以MIO有53个引脚可供我们使用,而EMIO有64个引脚可供我们使用。

使用EMIO的好处就,当MIO不够用时,PS可以通过驱动EMIO控制PL部分的引脚,接下来就来详细介绍下EMIO的使用。

EMIO的使用和MIO的使用其实是非常相似的。区别在于,EMIO的使用相当于,是一个PS + PL的结合使用的例子。所以,EMIO需要分配引脚,以及编译综合生成bit文件。

7.4 ZYNQ核的添加及配置

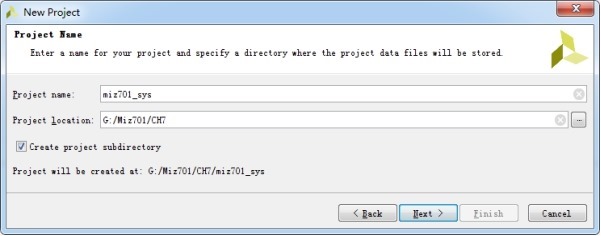

Step1:新建一个名为为Miz701_sys的工程

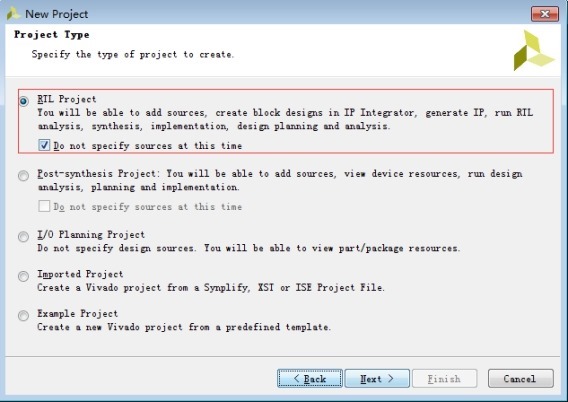

Step2:选择RTL Project 勾选Do not specify source at this time

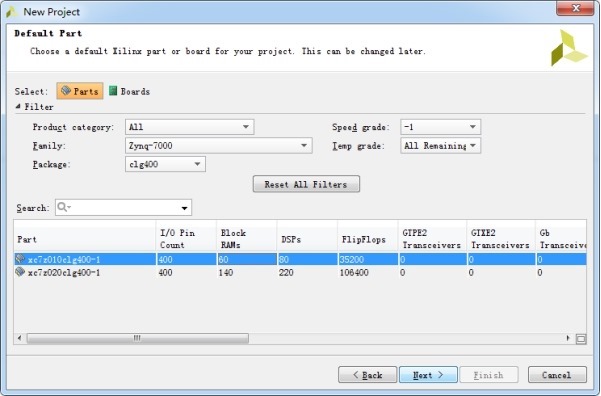

Step3:选择芯片型号xc7z010clg400-1

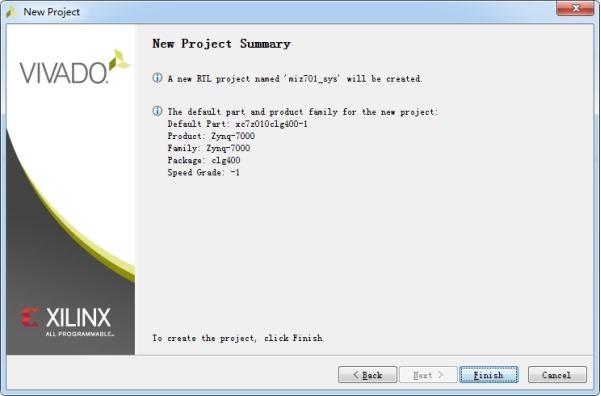

Step4:单击Finish

7.5使用IP Integrator创建硬件系统

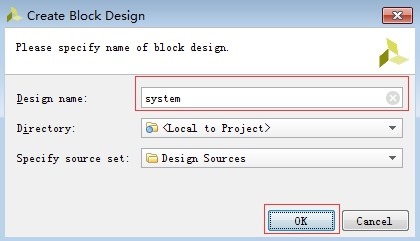

Step1:单击Create Block Design

Step2:输入system

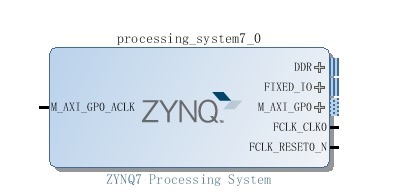

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

Step5:添加进来了ZYNQ CPU IP,双击ZYNQ CPU IP。

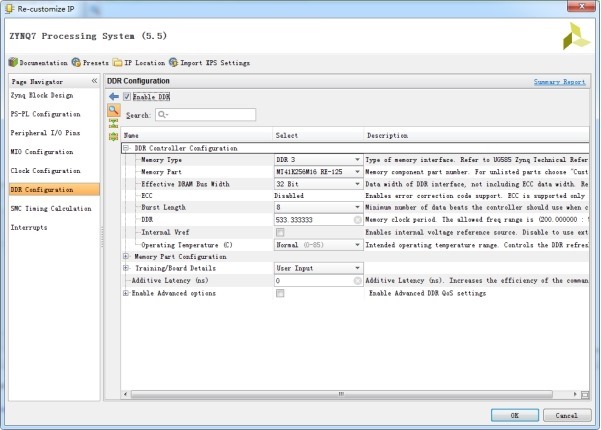

Step6: 修改时钟输入为50MHZ,可以看到ARM时钟为650MHZ DDR为525MHZ(1050MHZ),并且修改FCLK_CLK0 为100MHZ

step7:修改内存型号为MT41K256M16RE-125 M,单击OK。

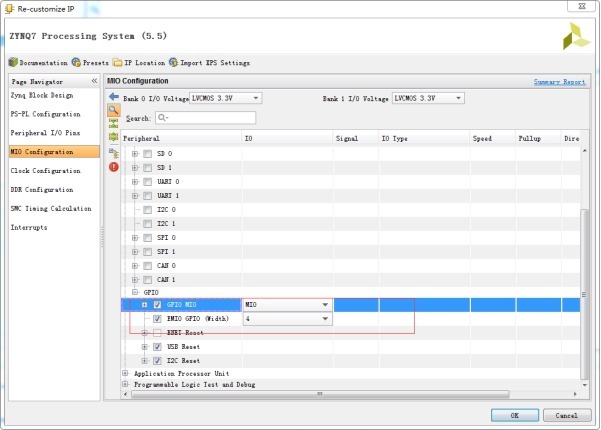

Setp8:选择MIO Configuration选项卡,再看到I/O Peripherals 中的GPIO一栏,勾选上其中的EMIO一栏,并选择4位引脚输出(最多可以选择64位,但是这个使用只需要4位足够了)。

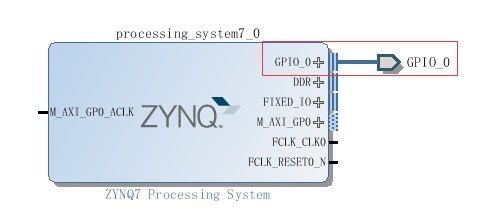

Setp10:按照上图设置好了之后,点击OK,仔细观察发现的zynq核心多出一组引脚名为GPIO_0,这个正是我们刚刚设置的一组EMIO,我们右击该引脚,选择make external把GPIO_0引脚引出(或者单击该引脚处,按快捷键Ctrl +t,也可以将引脚引出)。效果如下图所示:

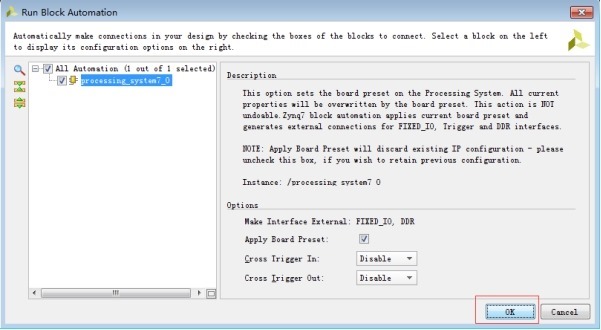

step11::单击Run Block Automation 进行自动连线,VIVADO软件会根据信号的命名规则智能连线。

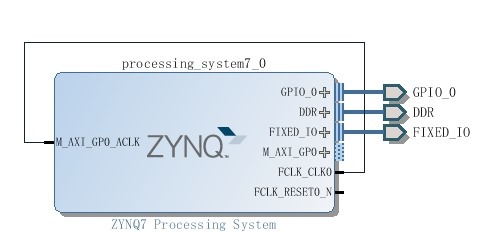

Step12:在你点击了OK后,你会发现DDR以及FICED_IO自动的延伸出来,然后把时钟FCLK_CLK0和M_AXI_GPI0_ACLK连接,其实就是给M_AXI_GP0_ACLK提供一个时钟。方法:当把鼠标靠近的时候会自动连接。

7.6产生HDL和约束文件

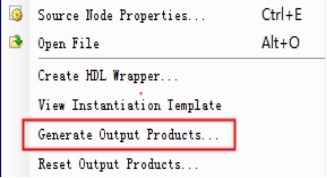

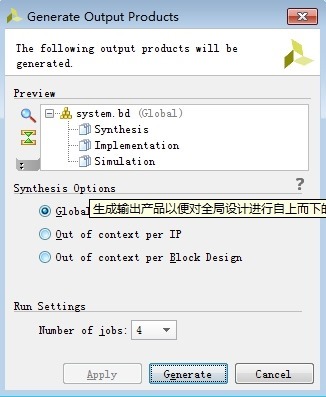

Setp1:接下来依然是,右键单击Block文件,文件选择Generate the Output Products,是文件得到一定的约束

Setp2:弹出如下对话框,直接点击Generate

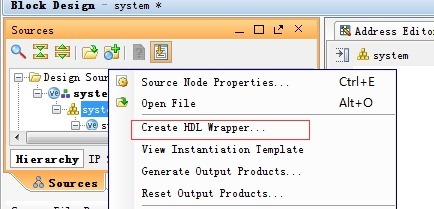

Setp3:继续右键单击Block文件,选择Create a HDL wrapper,根据Block文件内容产生一个HDL 的顶层文件:

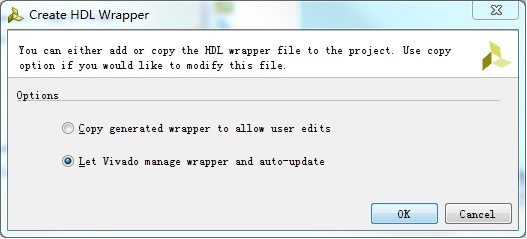

Setp4:并选择让vivado自动完成

Setp5:这里我们看到,Vivado给我创建了这样的顶层文件,其中的gpio_0_tri_io就是我们配置的EMIO

7.7 EMIO的管脚约束修改

我们发现,之前引出的EMIO叫做GPIO_0,到了顶层他的名字gpio_0_tri_io,而不是GPIO_0。所以分配引脚的时候就要注意了名字别错了,创建一个约束文件,分配引脚如下:

| set_property PACKAGE_PIN F17 [get_ports {gpio_0_tri_io[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {gpio_0_tri_io[0]}] set_property PACKAGE_PIN J15 [get_ports {gpio_0_tri_io[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {gpio_0_tri_io[1]}] set_property PACKAGE_PIN G14 [get_ports {gpio_0_tri_io[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {gpio_0_tri_io[2]}] set_property PACKAGE_PIN D18 [get_ports {gpio_0_tri_io[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {gpio_0_tri_io[3]}] |

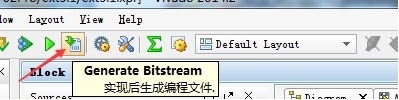

7.8 产生bit文件

此时可以,开始生成bit文件了:

7.9 导出bit文件

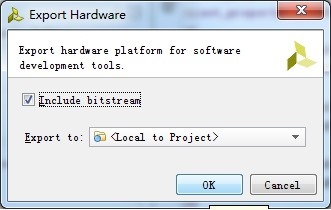

编译成功之后,依然是导出硬件:

7.10加载到SDK

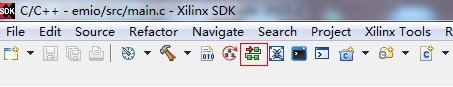

打开SDK,然后新建一个工程,以及添加一个main.C文件,具体过程参考前面章节。

添加程序如下:

| #include <stdio.h> #include "xgpiops.h" #include "sleep.h" int main() { static XGpioPs psGpioInstancePtr; XGpioPs_Config* GpioConfigPtr; int iPinNumber= 54; //想想为什么是54 u32 uPinDirection = 0x1; //1表示输出,0表示输入 int xStatus; //--MIO的初始化 GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID); if(GpioConfigPtr == NULL) return XST_FAILURE; xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr, GpioConfigPtr->BaseAddr); if(XST_SUCCESS != xStatus) print(" PS GPIO INIT FAILED \n\r"); //--MIO的输入输出操作 XGpioPs_SetDirectionPin(&psGpioInstancePtr, iPinNumber,uPinDirection);//配置IO输出方向 XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, iPinNumber,1);//配置IO的输出 while(1) { XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 1);//输出1 sleep(1);//延时 XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 0);//输出0 sleep(1);//延时 } return 0; } |

我们发现,驱动EMIO和MIO基本是一模一样的,唯一不同的地方就是iPinNumber此时的数字是54,上一节中是7。

再次看到这张图:

应为MIO和EMIO是同一编号的MIO共54个,从0~53。而从54开始就开始是EMIO了的范围了。之前我们应出了8个引脚gpio_0_tri_io[0]~gpio_0_tri_io[7],他们其实就依次对应54~61这几个序号,同时也对应了我们开发板上的8个LED(这是引脚约束的结果)。

你可以把iPinNumber的值从54换成55试试,看看实验结果有什么不同。

Ctrl + B编译通过后(软件默认设置是自动编译,即修改了源代码保存后就自动编译)

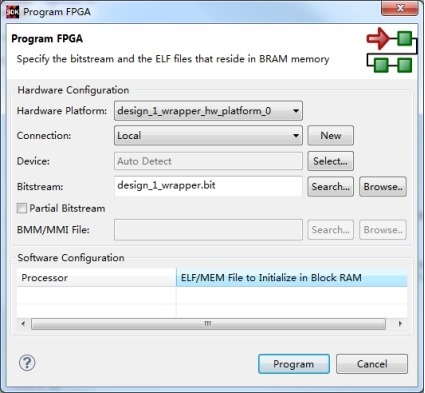

7.11 SDK环境下载bit文件

连接下载器,通过SDK先下载bit文件到开发板:

7.12 SDK下启动调试

然后,直接调试,就能看到你的EMIO控制的LED开始闪烁了。

7.13 实验效果

可以看到LD0一闪一闪

7.14 本章小结

通过本章的学习,我们掌握了在MIO不够使用的情况下,通过PL部分扩展EMIO增加IO的使用量。并且通过一个简单的例子演示了如果添加EMIO IP 并且启动SDK 通过JTAG下载调试的方法。

浙公网安备 33010602011771号

浙公网安备 33010602011771号