第一章 MIZ701 VIVADO 搭建SOC最小系统HelloWorld

本章内容是MIZ701中的第五章,本来也是要过渡一下FPGA部分的,但是由于MIZ701没有单独提供PL部分的晶振时钟,时钟必须通过PS产生,所以本章内容作为Miz701的第一章内容。本章的目的是搭建一个最小的SOC系统,并且测试串口输出,千兆以太网回路测试。本章先让PS部分搭建最小系统,这样可以从PS部分获取到时钟,然后为后面章节中PL部分提供时钟源。

1.0本章难度系数★★☆☆☆☆☆

1.1最小系统分析

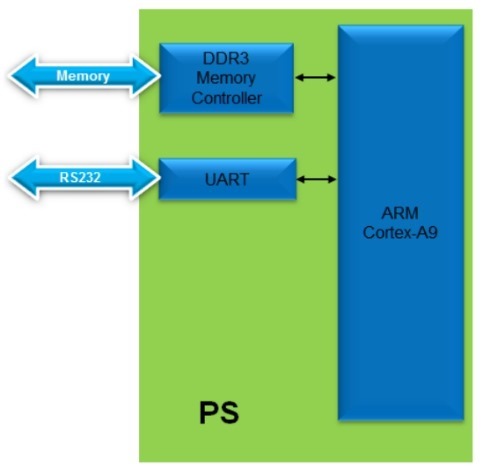

这张图展示了我们需要构建的最小系统。并且下面的嵌入式实验会基于这个最小系统进行添加外设。

本实验中将会只使用到PS部分资源包括了ARM Cotrex-A9、 DDR3内存、一个UART串口。这就是我们的最小系统。首先我们程序会加载到DDR内存中,然后CPU一条一条执行,那么执行的情况我们可以通过串口打印观察。

1.2板子使用的硬件

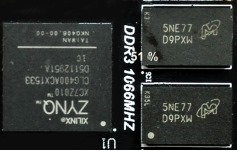

红色线框内就是本次实验需要用到的资源,分别为CPU XC7Z010、2片512MB内存、一个Micro接口的USB 转 UART,内存型号实际焊机MT41K256M16RE-125 M

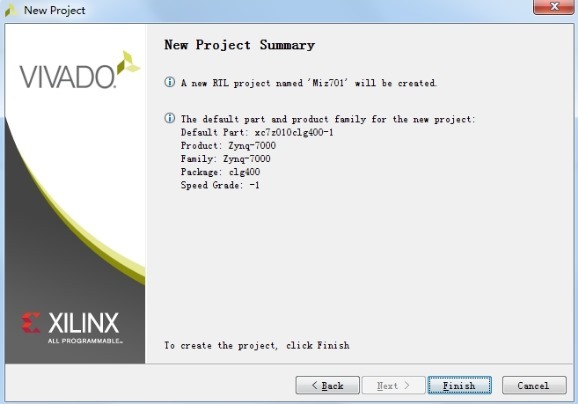

1.3新建一个VIVADO工程

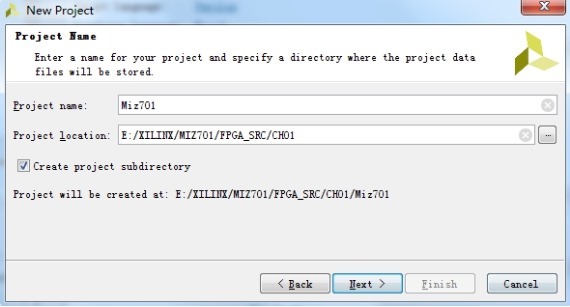

Step1:新建一个名为为Miz701的工程

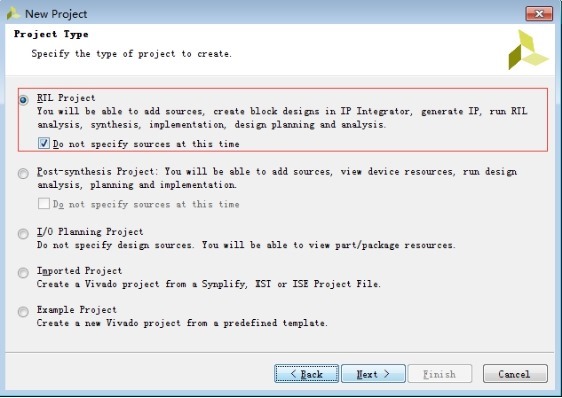

Step2:

Step3:

Step4:

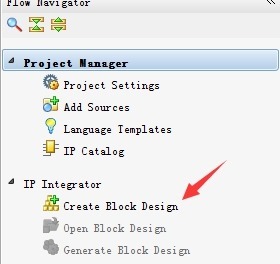

1.4使用IP Integrator创建硬件系统

Step1:单击Create Block Design

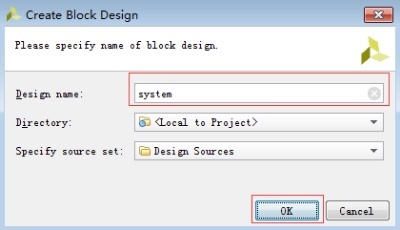

Step2:输入system

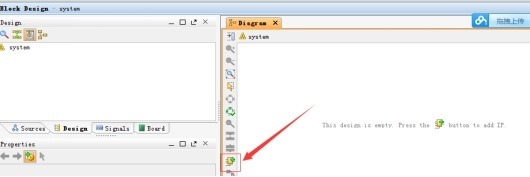

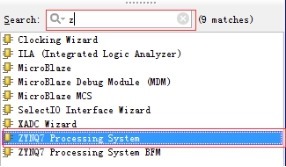

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

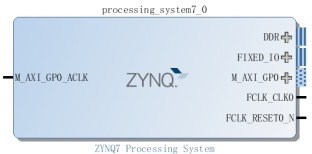

Step5:添加进来了ZYNQ CPU IP,然后双击下图

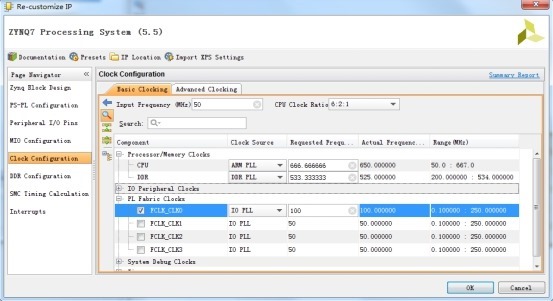

Step6:修改时钟输入为50MHZ,可以看到ARM时钟为650MHZ DDR为525MHZ(1050MHZ),并且修改FCLK_CLK0 为100MHZ

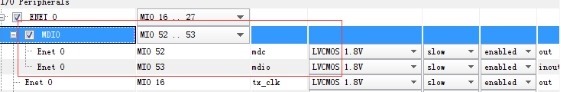

Step7:修改MIO的配置 修改IO电压,增加ENT0 和UART1接口,下面会测试这2个接口,之后单机OK.

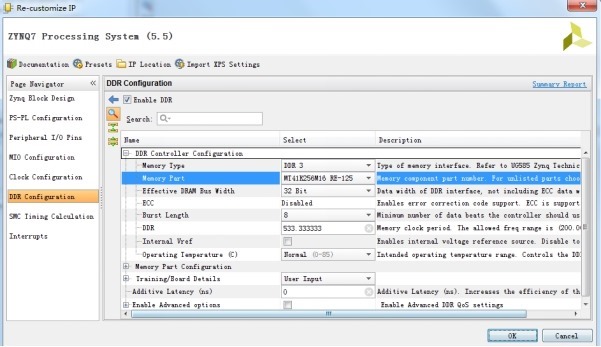

Step8:修改内存型号为MT41K256M16RE-125 M

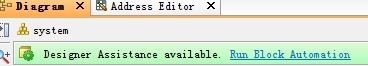

Step9:单机Run Block Automation 进行自动连线,VIVADO软件会根据信号的命名规则智能连线。

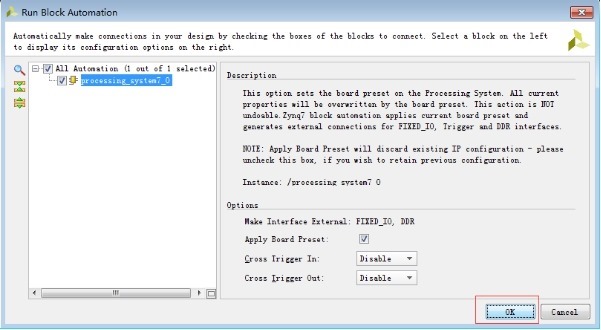

Step10:勾选如下,直接单机OK

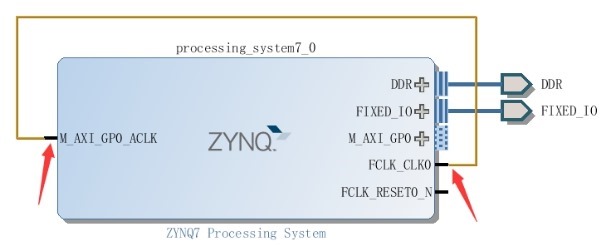

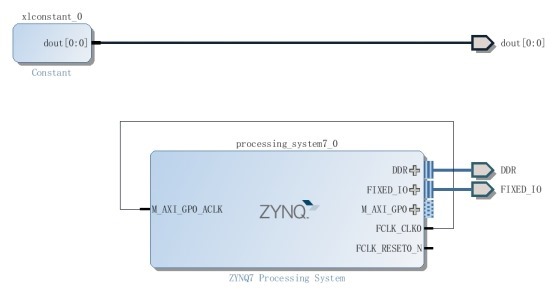

Step11:在你点击了OK后,你会发现DDR以及FICED_IO自劢的延伸出来,然后把时钟FCLK_CLK0和M_AXI_GPI0_ACLK连接。方法:当把鼠标靠近的时候会自动连接。

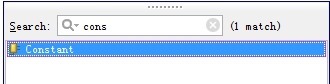

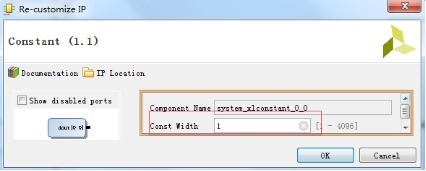

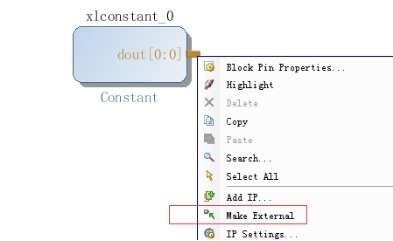

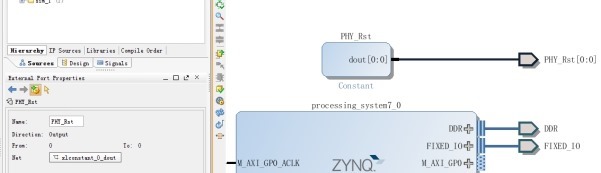

Step12:为了让以太网PHY RTL8211E-VL可以工作,必须让其复位PIN脚设置为1,只要简单添加一个常量IP并且映射到PL部分的PIN脚(复位脚在FPGA 部分(PL)),和添加CPU方法一样

Step13:双击设置常量为1

Step14:右击PIN脚选择Make External

Step15:取个有意义的名字如下图,只要单击相应的模块就可以在右手边修改

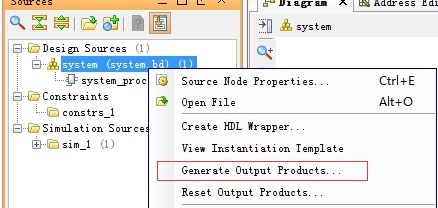

Step16: 右击 system.bd, 单击Generate Output Products

Step17:支部操作会产生执行、仿真、综合的文件,可以看出来最后的硬件设计步骤还是回到了我们前面的FPGA开发上来了。

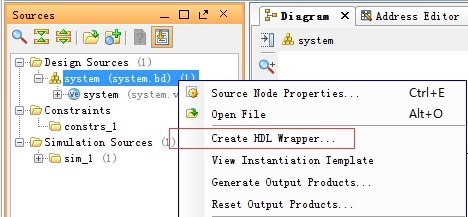

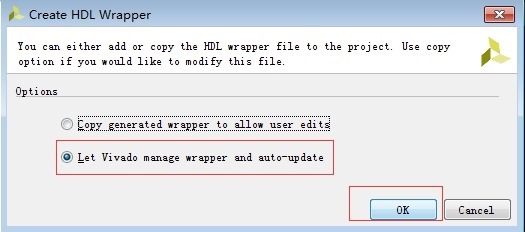

Step18:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step19:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

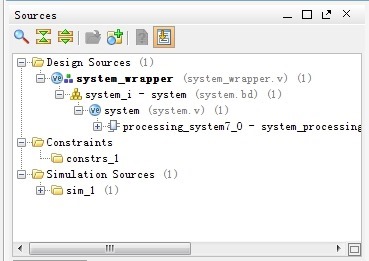

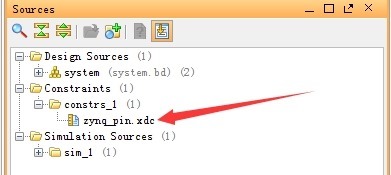

Step20:之后我看下源码的层次结构,可以看到system_wrapper.v就是顶层文件,调用了CPU.

Step21:查看system_wrapper.v源码

| //Copyright 1986-2015 Xilinx, Inc. All Rights Reserved. //-------------------------------------------------------------------------------- //Tool Version: Vivado v.2015.4 (win64) Build 1412921 Wed Nov 18 09:43:45 MST 2015 //Date : Sun Aug 28 12:47:04 2016 //Host : Administrator running 64-bit Service Pack 1 (build 7601) //Command : generate_target system_wrapper.bd //Design : system_wrapper //Purpose : IP block netlist //-------------------------------------------------------------------------------- `timescale 1 ps / 1 ps module system_wrapper (DDR_addr, DDR_ba, DDR_cas_n, DDR_ck_n, DDR_ck_p, DDR_cke, DDR_cs_n, DDR_dm, DDR_dq, DDR_dqs_n, DDR_dqs_p, DDR_odt, DDR_ras_n, DDR_reset_n, DDR_we_n, FIXED_IO_ddr_vrn, FIXED_IO_ddr_vrp, FIXED_IO_mio, FIXED_IO_ps_clk, FIXED_IO_ps_porb, FIXED_IO_ps_srstb, PHY_Rst); inout [14:0]DDR_addr; inout [2:0]DDR_ba; inout DDR_cas_n; inout DDR_ck_n; inout DDR_ck_p; inout DDR_cke; inout DDR_cs_n; inout [3:0]DDR_dm; inout [31:0]DDR_dq; inout [3:0]DDR_dqs_n; inout [3:0]DDR_dqs_p; inout DDR_odt; inout DDR_ras_n; inout DDR_reset_n; inout DDR_we_n; inout FIXED_IO_ddr_vrn; inout FIXED_IO_ddr_vrp; inout [53:0]FIXED_IO_mio; inout FIXED_IO_ps_clk; inout FIXED_IO_ps_porb; inout FIXED_IO_ps_srstb; output [0:0]PHY_Rst; wire [14:0]DDR_addr; wire [2:0]DDR_ba; wire DDR_cas_n; wire DDR_ck_n; wire DDR_ck_p; wire DDR_cke; wire DDR_cs_n; wire [3:0]DDR_dm; wire [31:0]DDR_dq; wire [3:0]DDR_dqs_n; wire [3:0]DDR_dqs_p; wire DDR_odt; wire DDR_ras_n; wire DDR_reset_n; wire DDR_we_n; wire FIXED_IO_ddr_vrn; wire FIXED_IO_ddr_vrp; wire [53:0]FIXED_IO_mio; wire FIXED_IO_ps_clk; wire FIXED_IO_ps_porb; wire FIXED_IO_ps_srstb; wire [0:0]PHY_Rst; system system_i (.DDR_addr(DDR_addr), .DDR_ba(DDR_ba), .DDR_cas_n(DDR_cas_n), .DDR_ck_n(DDR_ck_n), .DDR_ck_p(DDR_ck_p), .DDR_cke(DDR_cke), .DDR_cs_n(DDR_cs_n), .DDR_dm(DDR_dm), .DDR_dq(DDR_dq), .DDR_dqs_n(DDR_dqs_n), .DDR_dqs_p(DDR_dqs_p), .DDR_odt(DDR_odt), .DDR_ras_n(DDR_ras_n), .DDR_reset_n(DDR_reset_n), .DDR_we_n(DDR_we_n), .FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn), .FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp), .FIXED_IO_mio(FIXED_IO_mio), .FIXED_IO_ps_clk(FIXED_IO_ps_clk), .FIXED_IO_ps_porb(FIXED_IO_ps_porb), .FIXED_IO_ps_srstb(FIXED_IO_ps_srstb), .PHY_Rst(PHY_Rst)); endmodule |

可以看到顶层文件的源码调用了CPU接口,所有外设的接口也都是通过顶层文件引出来的。

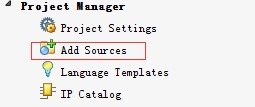

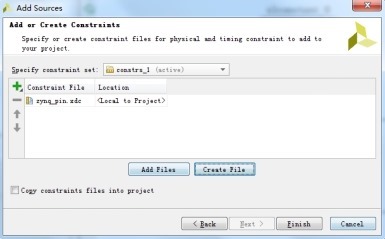

Step22:单机Add Sources

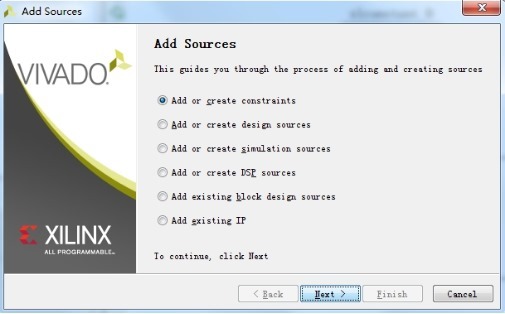

Step23:选择Add or create constraints

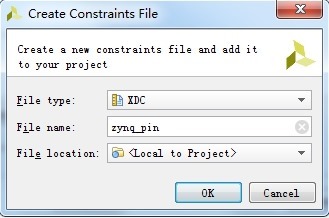

Step24:选择Create File

Step25:输入zynq_pin

Step26:如图,单击Finish

Step27:双击打开zynq_pin.xdc文件,添加PIN脚约束

Step28:双击打开zynq_pin.xdc文件,添加PIN脚约束

| set_property PACKAGE_PIN E17 [get_ports PHY_Rst[0]] set_property IOSTANDARD LVCMOS33 [get_ports PHY_Rst[0]] |

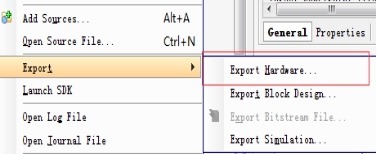

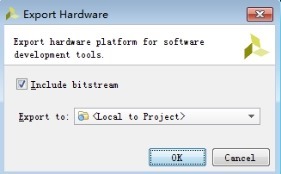

1.6导出SOC硬件到SDK

Step1:File->Export->Export Hardware

Step2:勾选Include bitstream 直接单击OK

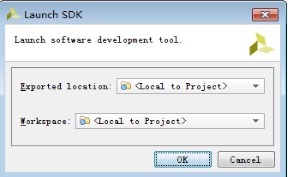

Step3:File->Launch SDK加载到SDK

Step4:单击OK

1.6 HelloWorld程序

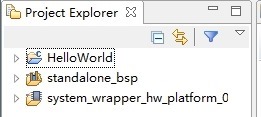

Step1:导出完成后如下图

1、硬件部分,这部分就是从VIVADO定制好的SOC硬件

2、这部分是硬件的地址空间分配

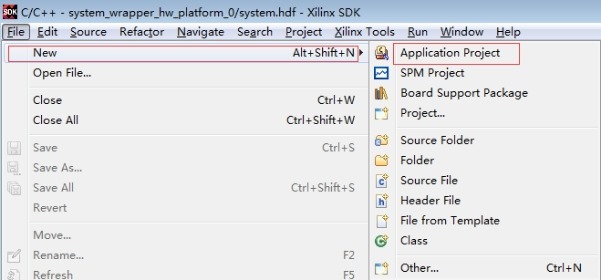

Step2:选择File->New->Application Project

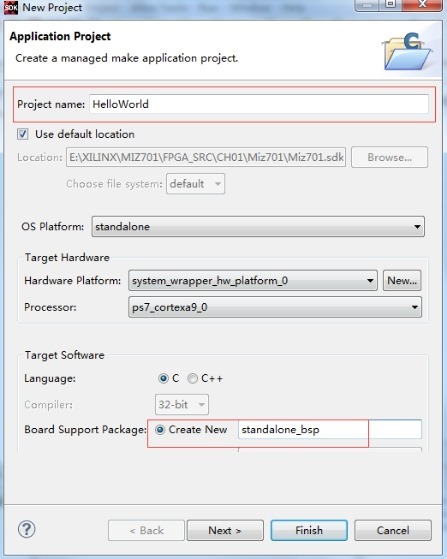

Step3:工程命名为HelloWorld,创建的bsp包取名为Miz702_bsp,然后单击NEXT

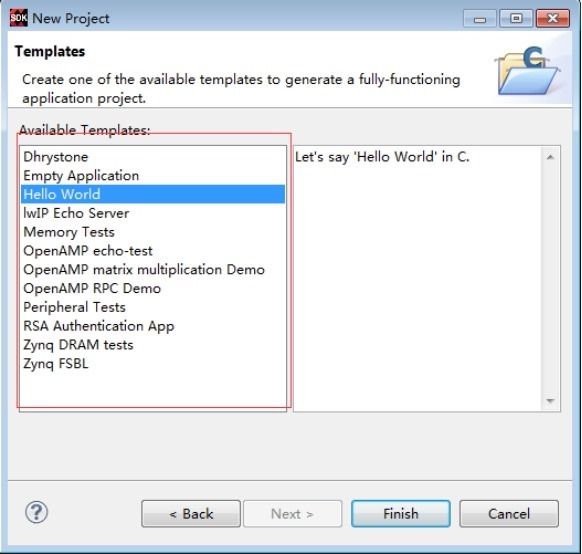

Step4:系统里面有很多自带的测试程序,本次就用自带的Helloworld程序做测试,单击Finish

Step5:完成后

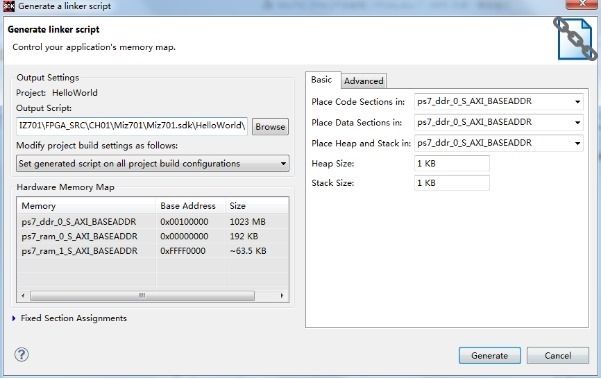

Step6:右击HelloWorld->Generate linker Script

Step7:可以看到所有可用内存的情况,代码、数据、堆栈运行所在内存的情况。不做人后改动,关闭。

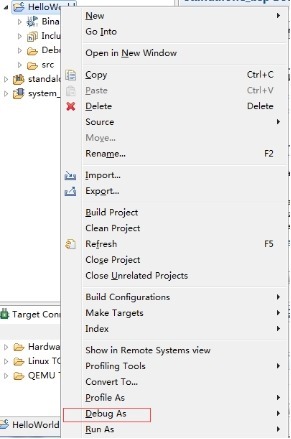

Step8:右击HelloWorld->

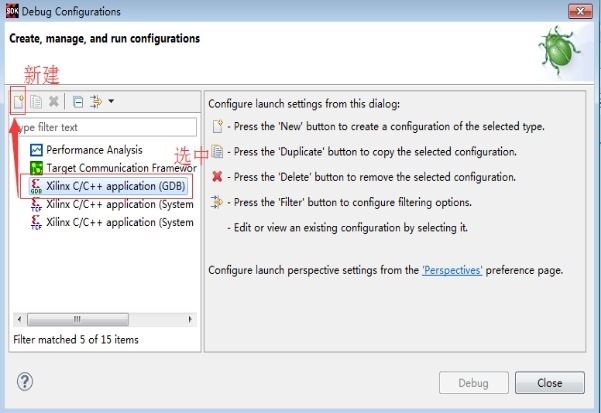

Step9:单击这个位置新建

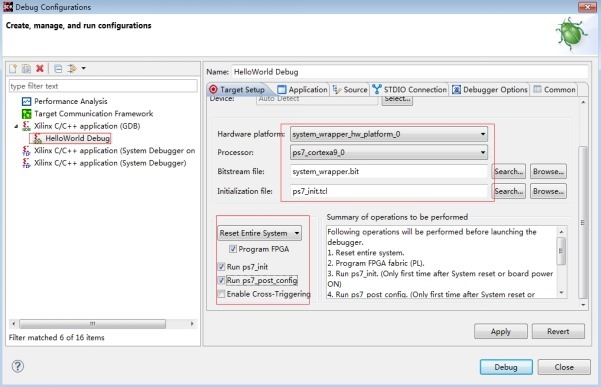

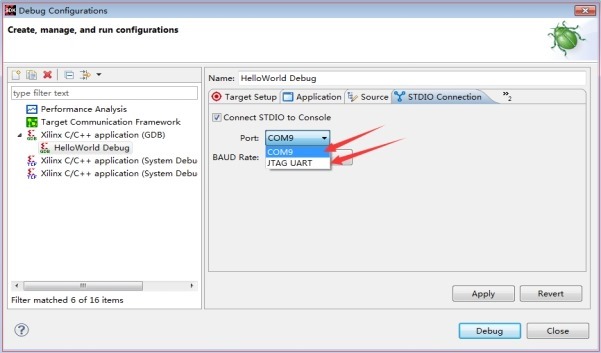

Step11:设置调试信息输出的端口可以到支持串口和JTAG方式,如果使用串口先确保串口已经接通到电脑,并且开发板已经通电。这里选择串口,这样可以测试我们的串口是否正常工作了。如果以后调试可以直接使用JTAG调试更加方便并且波特率设置到115200之后单击Apply。之后单击Debug(注意开发板必须通电,另外TF卡确保拔掉)

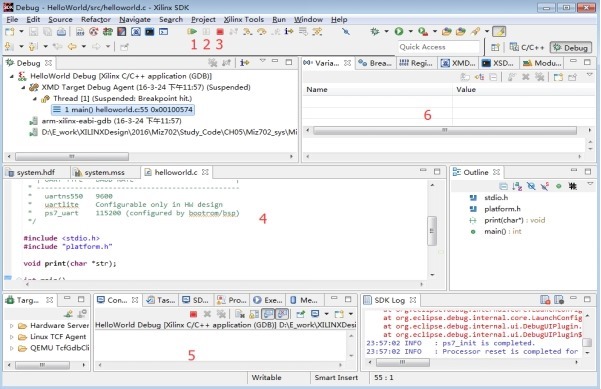

Step12:进入SDK调试界面

1、启动2、暂停3、停止4、代码5、信息控制台6、调试变量

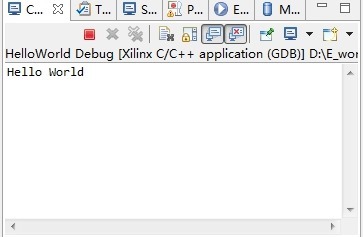

Step13:单击运行输出结果

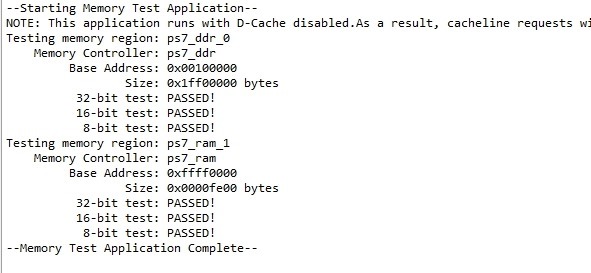

1.7 MemTest内存测试程序

Step1:新建一个名为MemTest的工程

Step2:任然采用自带的测试函数测试

Step3:测试结果

1.8 DRAMTest内存测试程序

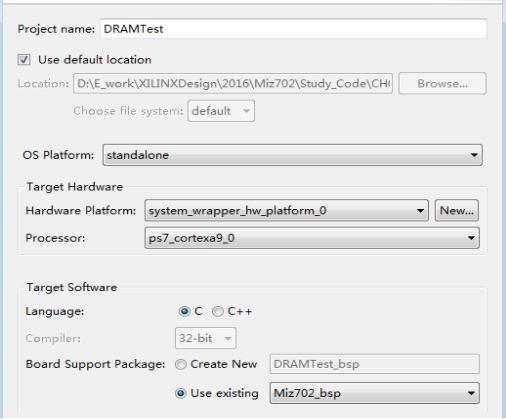

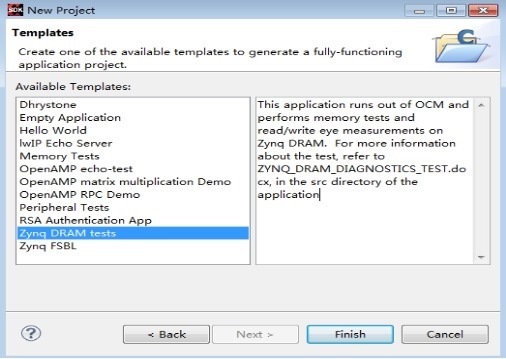

Step1:新建一个名为DRAMTest的工程

Step3:新建一个名为MemTest的工程

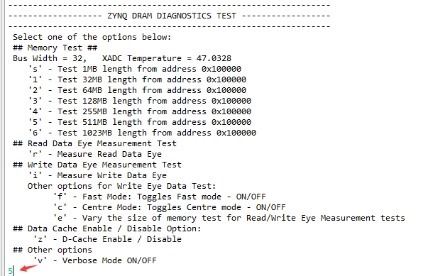

Step4:测试结果

根据提示可以在控制台中输入相关序号按回车进行(r,i测试会有一部分错误,还以和程序空间有关系)

1.9 LWIP协议对千兆网口测试

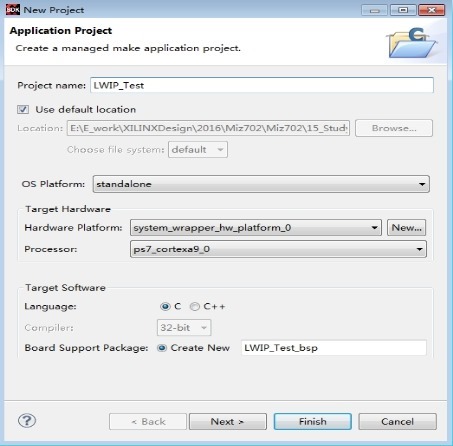

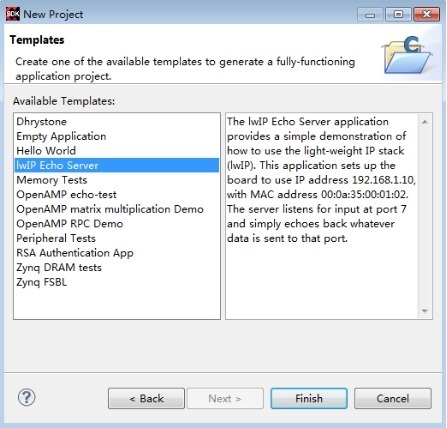

Step1:新建一个名为LWIP_Test的工程

Step2:选择LWIP Echo Server 之后单击Finish

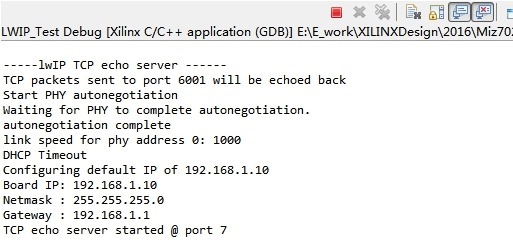

Step3:运行之后的串口打印信息

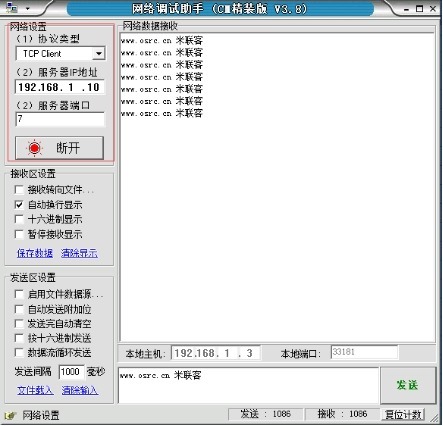

Step4:用网络助手实现回传测试

1.10使用快捷按钮调试

使用这两个图标,一个是debug一个是运行模式可以方便调试。

1.11 本章小结

本章详细讲解了定制一个SOC最小系统,并且运行了自带的HelloWorld工程、MemTest内存测试工程、DRAMTest内存测试工程、LWIP网络协议工程对千兆网口测试。本章让初学者可以搭建一个最小的SOC系统,并且教会读者利用软件自动的工程对SOC的基本外设进行测试。

浙公网安备 33010602011771号

浙公网安备 33010602011771号