01PLL_TEST_仿真入门实验

软件版本:Fuxi2022.1

操作系统:WIN10 64bit

硬件平台:适用京微齐力FPGA

登录"米联客"FPGA社区-www.uisrc.com视频课程、答疑解惑!

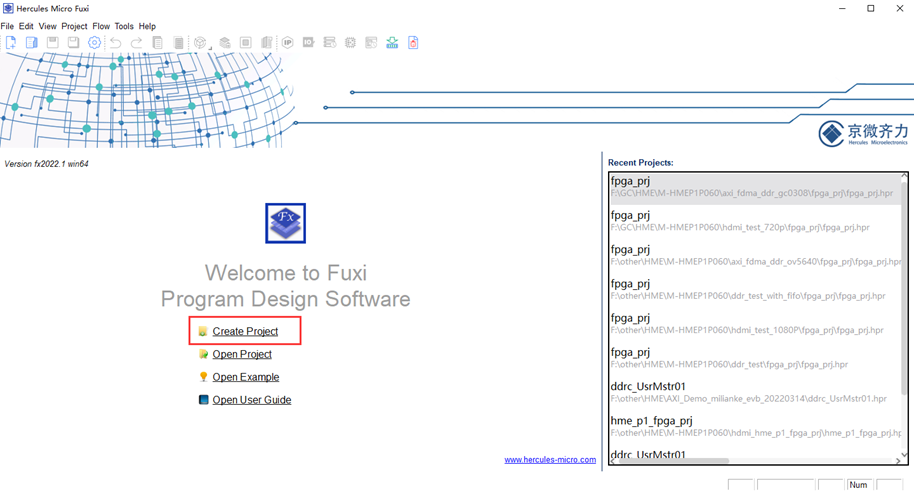

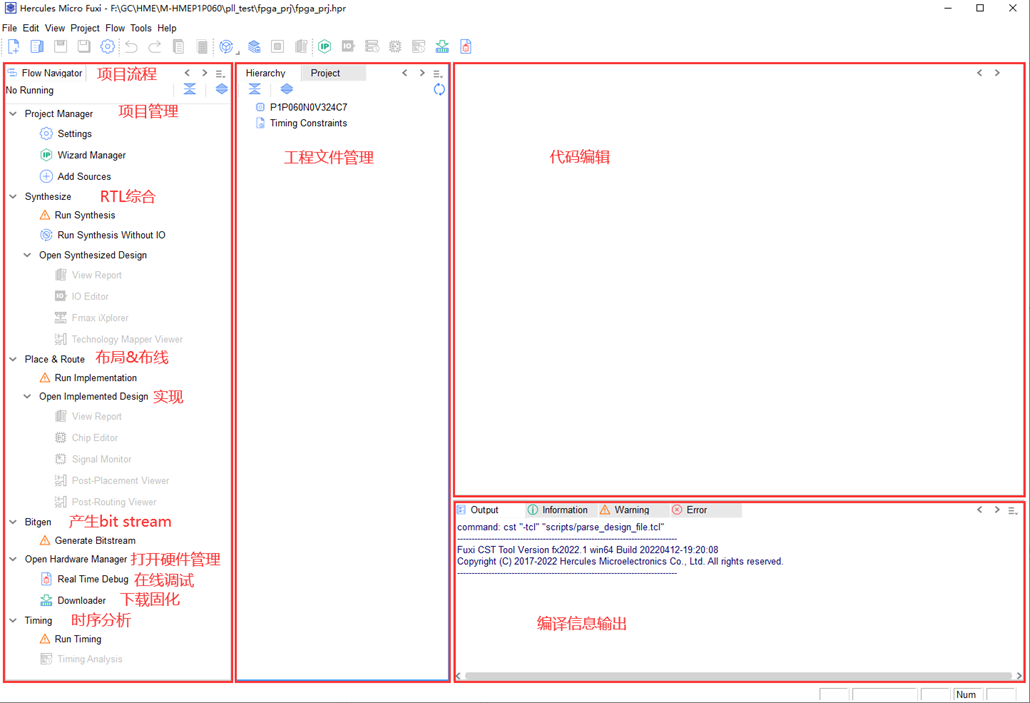

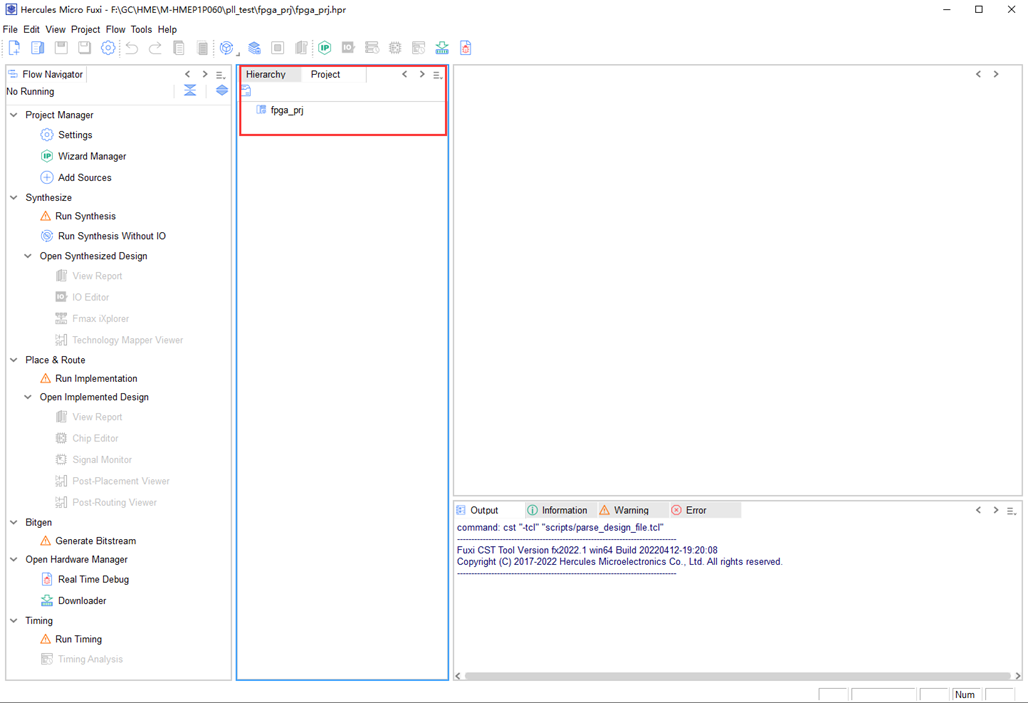

1创建FPGA工程

1.1创建1个新的工程

启动Fuxi2022.1

创建一个新的工程

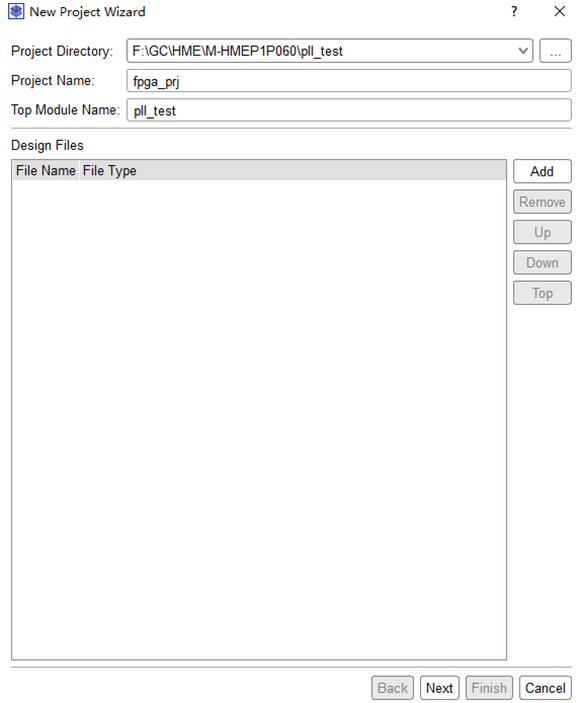

Project Directory设置工程路径

Project Name 设置fpga工程名称,米联客的教学内容fpga工程一般命名为fpga_prj

TopModule Name设置顶层模块的名称

Design Files如果有,可以单击Add添加,也可以工程创建完成后新建或者添加,这里我们还没有创建FPGA代码文件,所有先不添加。

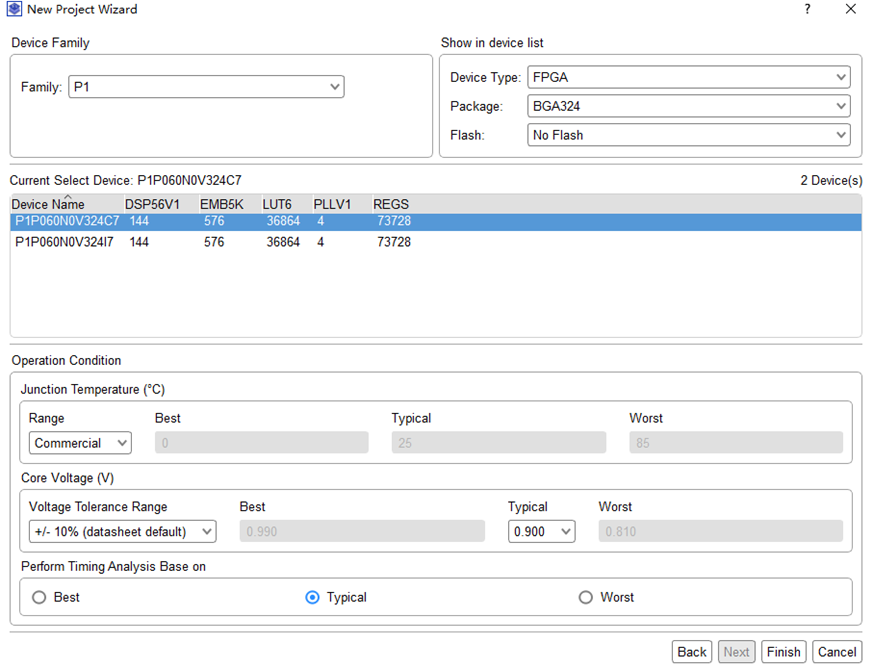

Device Family设置向导:

Family:FPGA的系列家族,这里选择P1

Device Type:选择FPGA

Package:封装选择BGA324

Flash:P1默认没有内置FLASH所以是NO Flash

Current Select Device选型向导:

选择具体的FPGA型号,这里选择P1P060N0V324C7

Operation Condition:芯片操作设置向导

Junction Temperature:何止工作温度范围

Core Tolerance Range:设置核心工作电压范围,一般选择默认设置

Perform Timing Analysis Base on:设置时序分析策略,一般设置为Typical

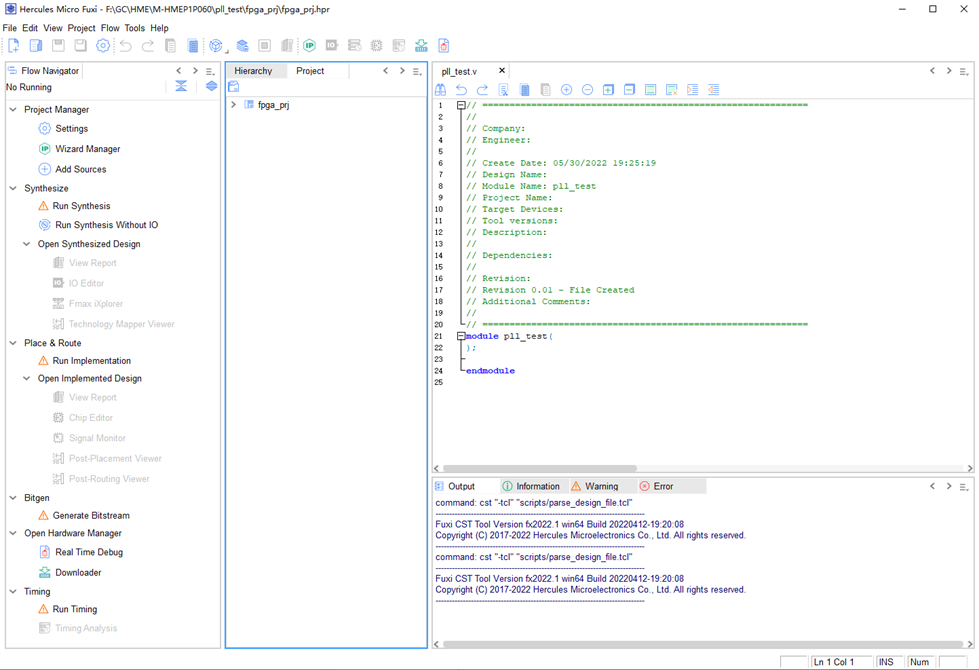

1.2创建FPGA程序文件

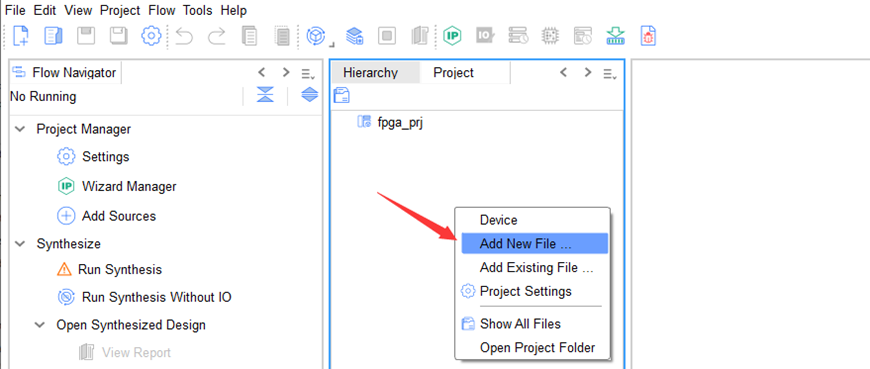

右击创建或者添加文件,把工程文件管理标签切换到Project可以看到fpga_prj工程名。

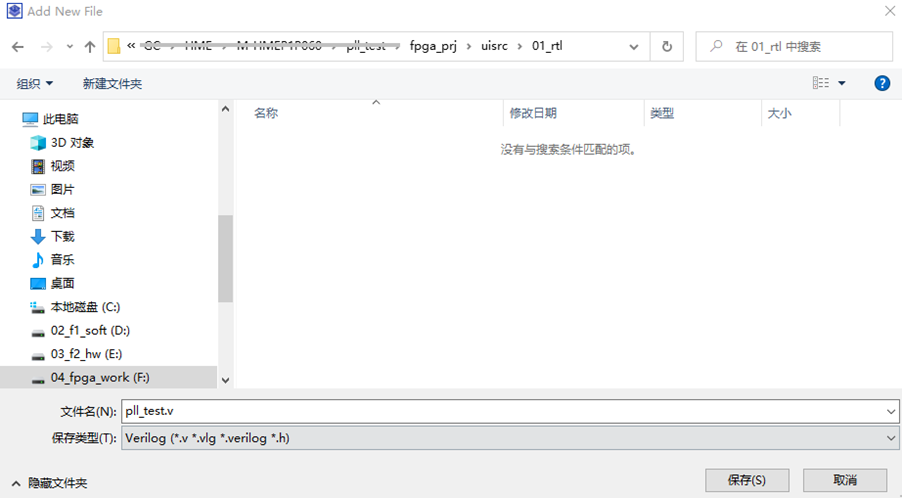

我们这里创建一个新的pll_test文件,并且编写相应的代码

右击下图空白处,单击Add New File

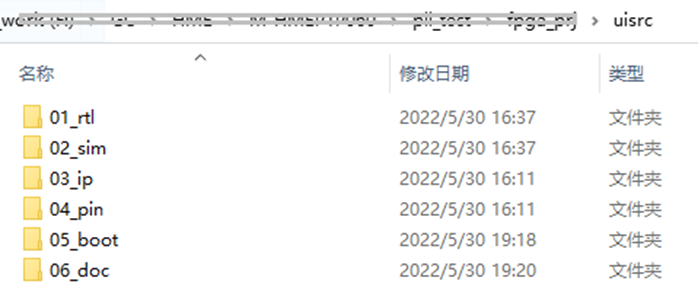

米联客习惯把一些IP路径根据自己的习惯放到自定义的路径下

创建pll_test.v测试程序文件,并且保持到uisrc/01_rtl路径下

编写测试代码

module pll_test( input sysclk, output up_led ); wire [3:0] up_led;

wire clk0; wire pll_lock; reg [25:0] cnt;

assign up_led = {cnt[25:24],cnt[22:21]};

mypll mypll_u( .clkin0 (sysclk), .clkout0(clk0),//single output up to 200MHz .locked (pll_lock) );

always @ (posedge clk0)begin cnt <= cnt + 1'b1; //cnt power on initial value is all 1 end

endmodule |

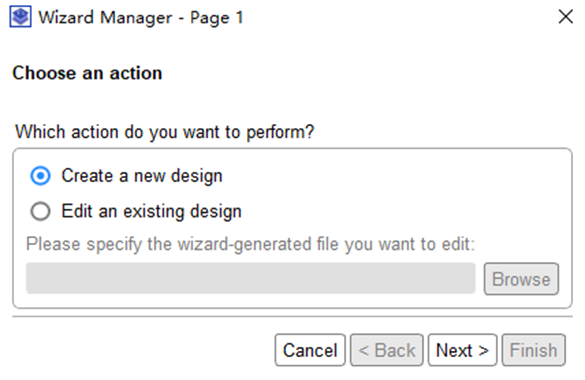

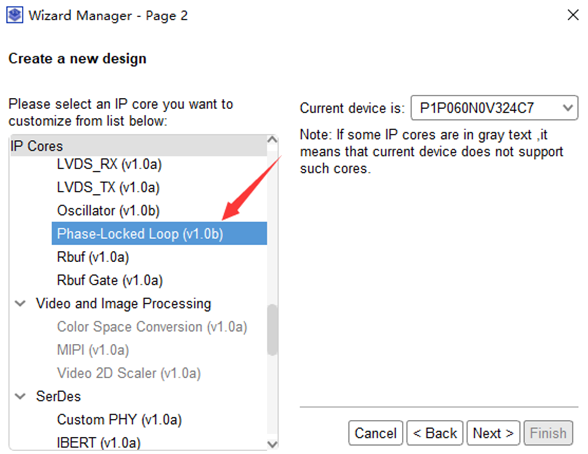

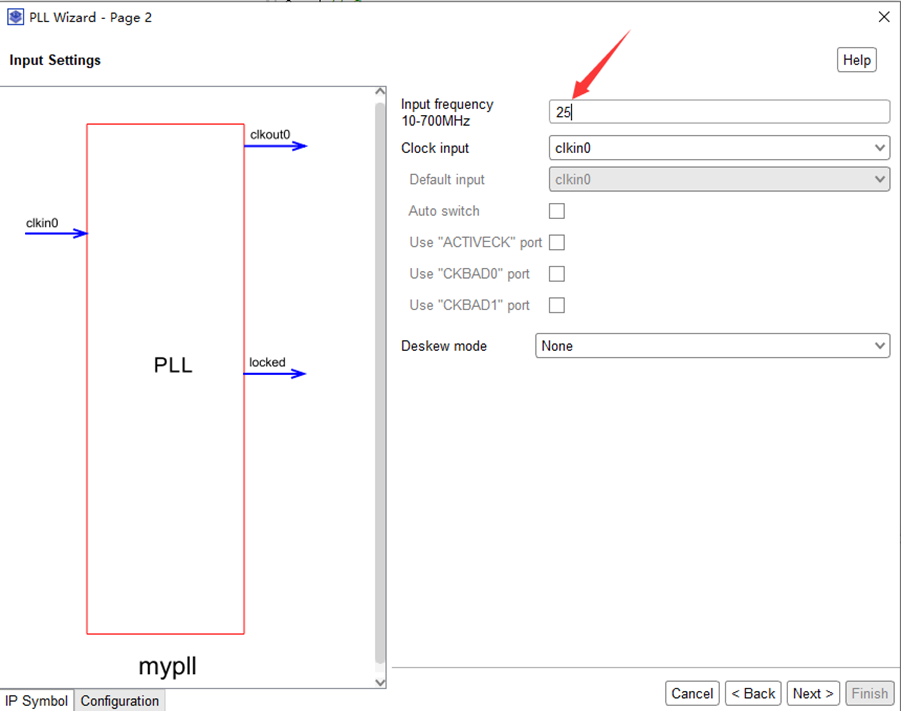

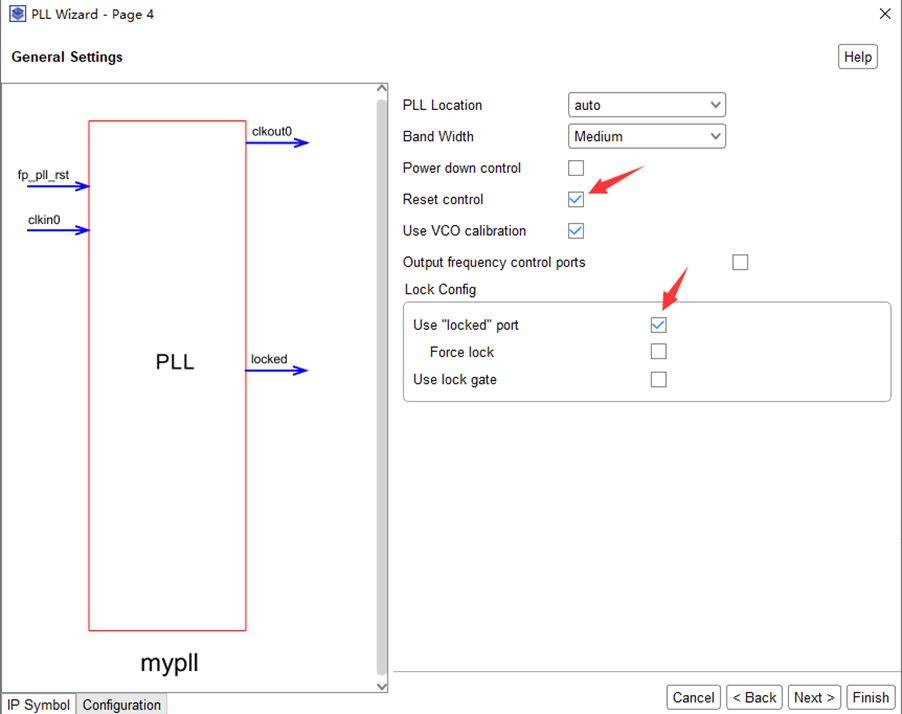

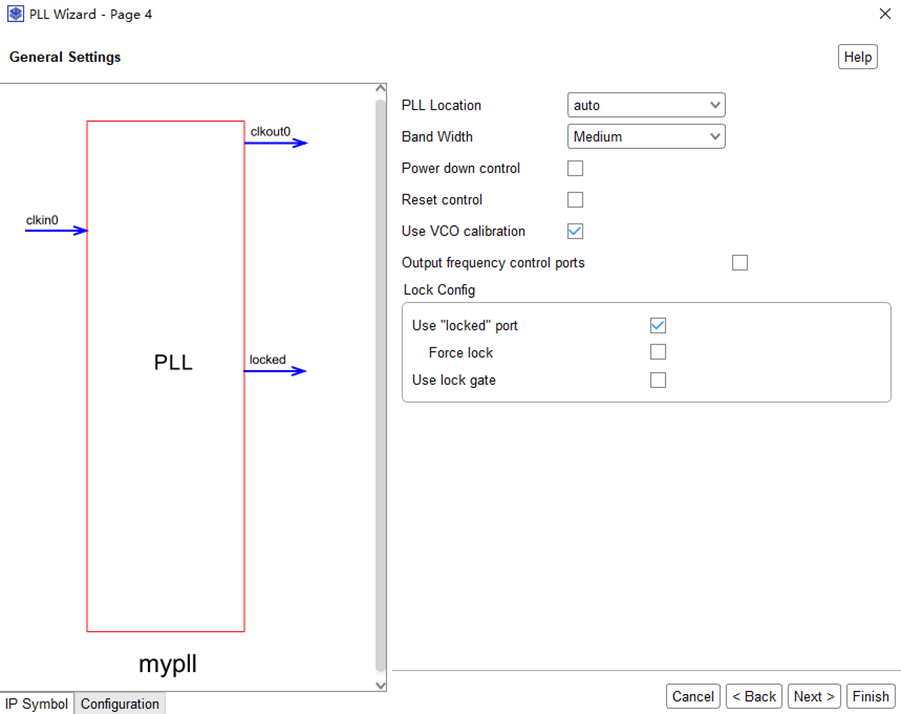

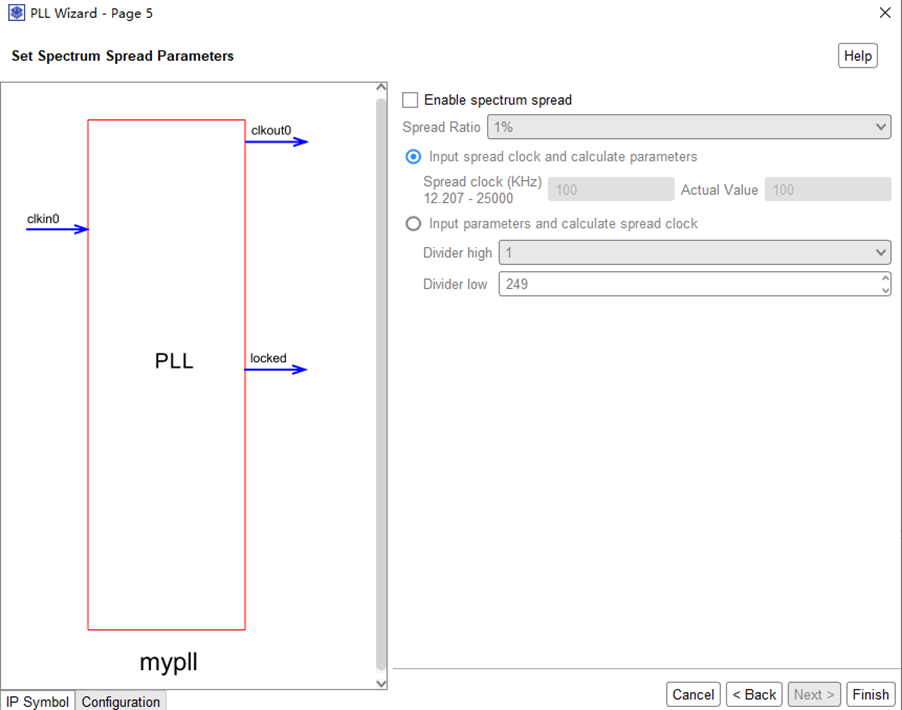

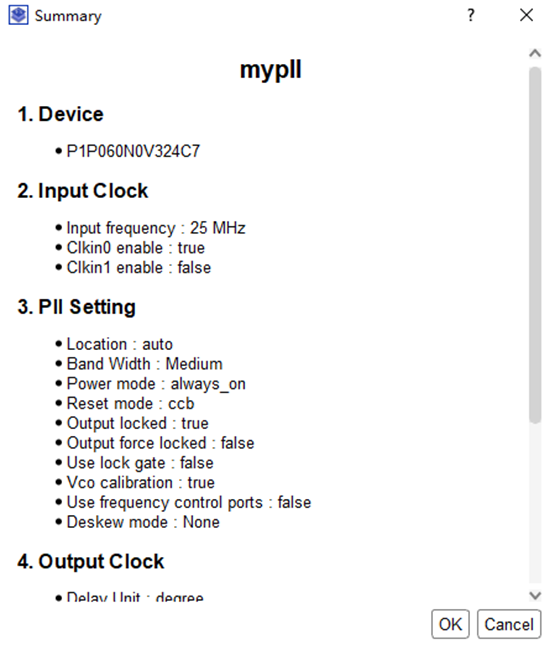

1.3添加PLL IP

以上代码中用到了PLL,PLL IP的添加过程如下:

添加IP

选择Phase-Locked Loop 这个IP

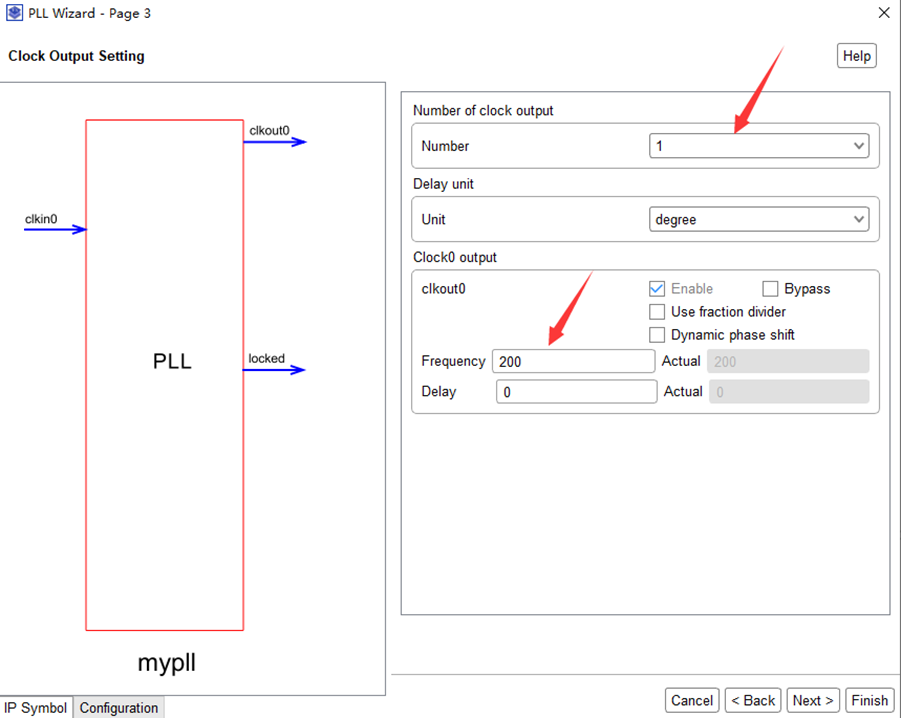

Number of clock output:输出的时钟数量选择1,最大可以设置6

Delay unity 设置时钟相位偏移的方式,默认是设置角度

Clock0 output:

Frequency设置倍频输出的频率

Delay设置相位

其他的Use fraction divider和Dynamic phase shift以及Bypass模式都没用到

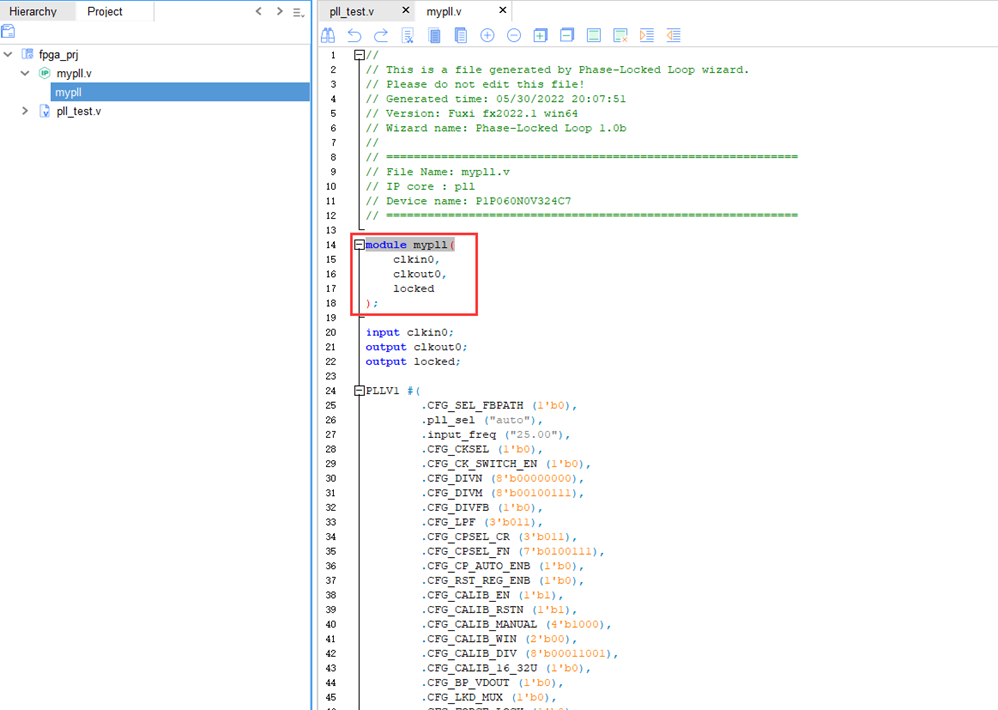

可以看到右边mypll ip里面调用 PLLV1 源语

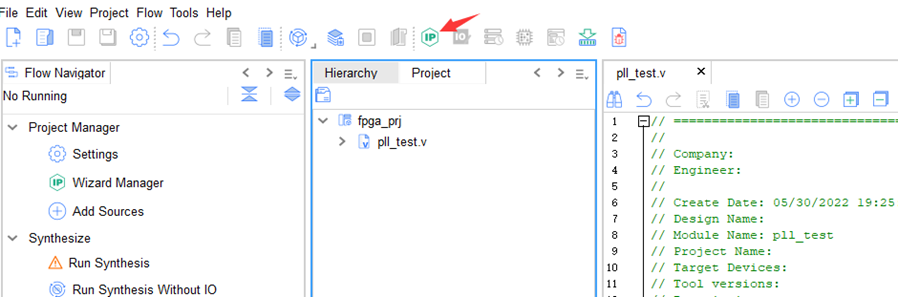

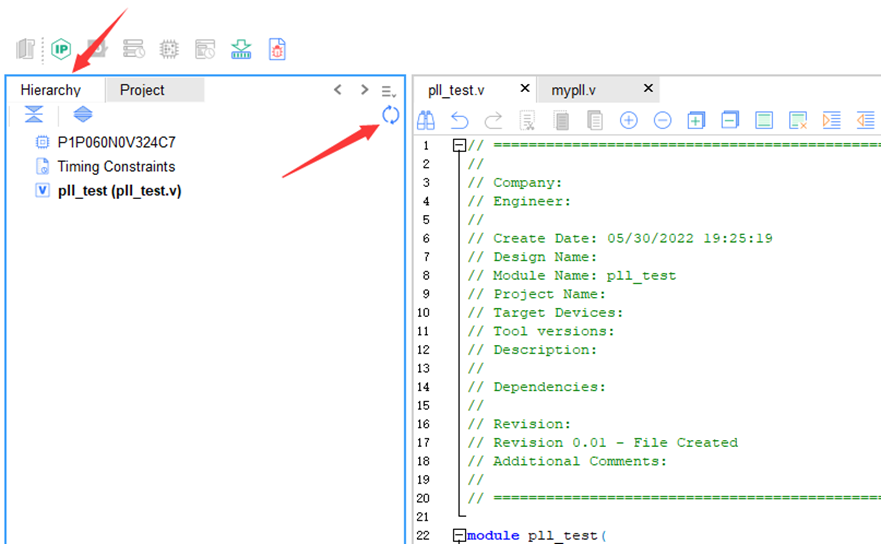

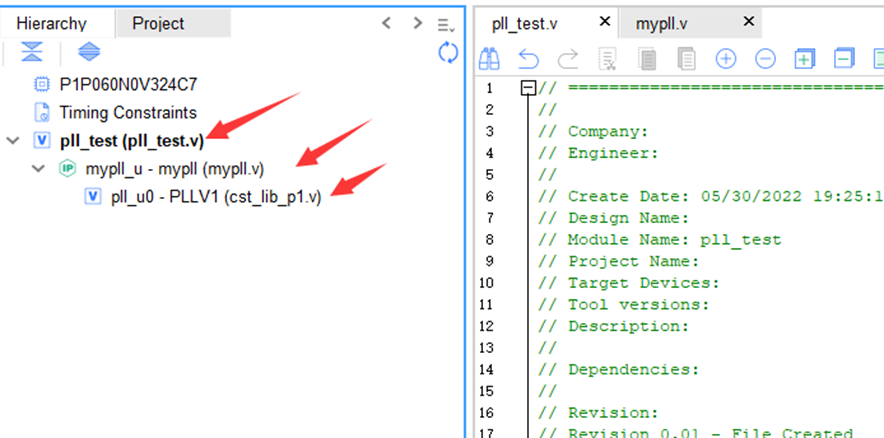

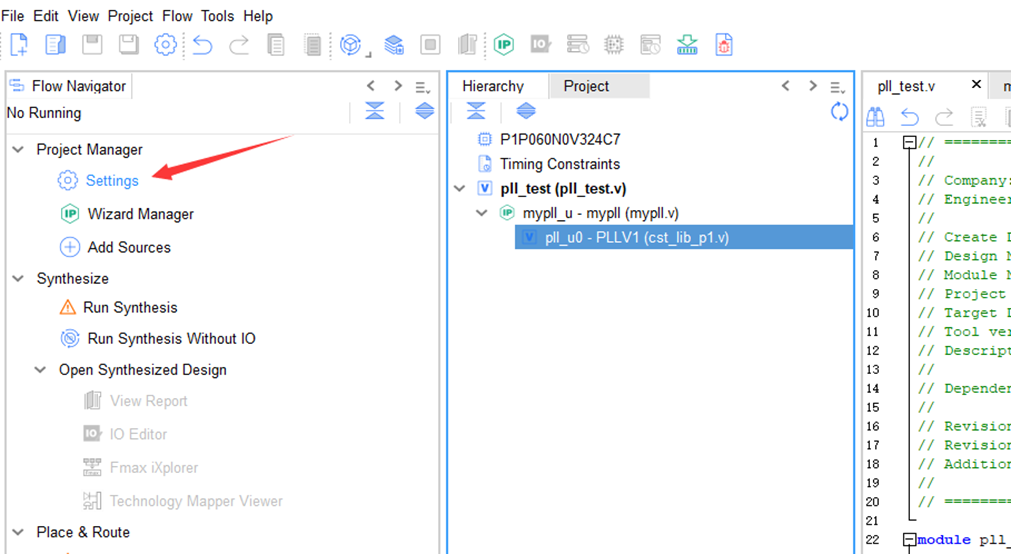

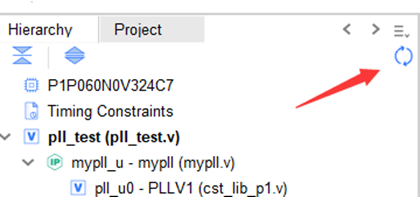

1.4手动更新层次化

目前fuxi软件默认需要手动刷新(手动刷新可以防止自动刷新导致某些时候卡顿)后才能看到FPGA的层次结构,切换到Hierarchy,并且单击下右边的箭头位置如图,更新下层次设计

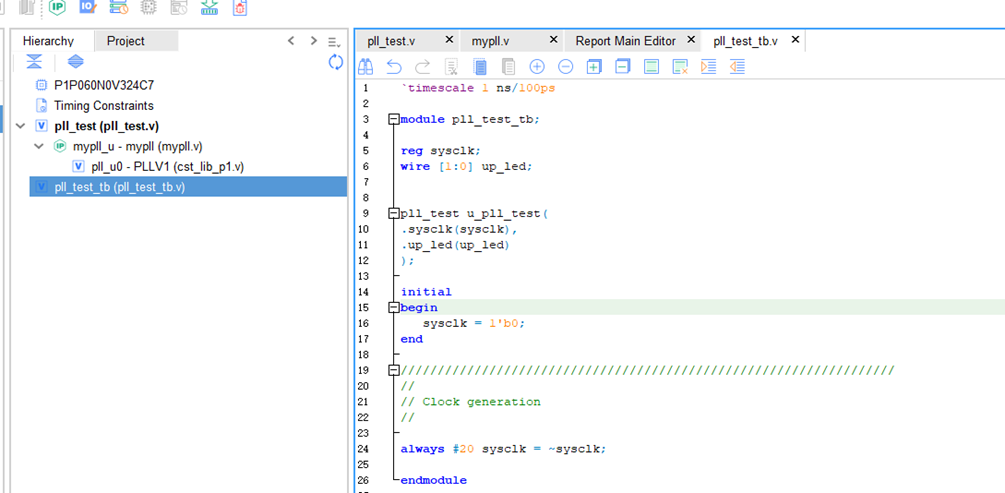

1.5编写仿真文件

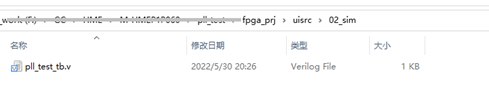

以相同的方式编写一个仿真测试激励文件,并且放到uisrc/02_sim路径

源码如下:

`timescale 1 ns/100ps

module pll_test_tb;

reg sysclk; wire [1:0] up_led;

pll_test u_pll_test( .sysclk(sysclk), .up_led(up_led) );

initial begin sysclk = 1'b0; end

/////////////////////////////////////////////////////////////////// // // Clock generation //

always #20 sysclk = ~sysclk;

endmodule

|

2RTL仿真

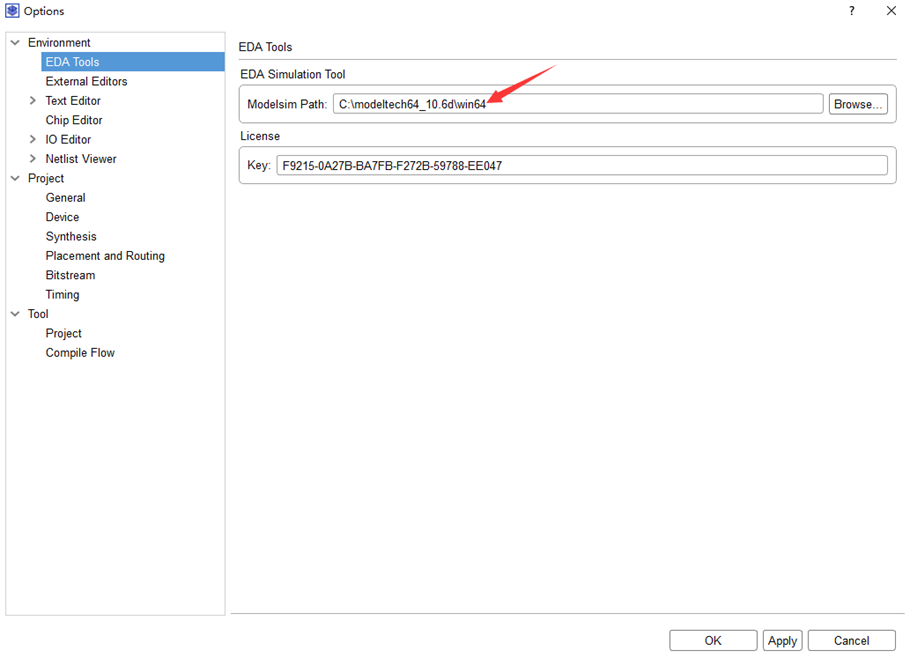

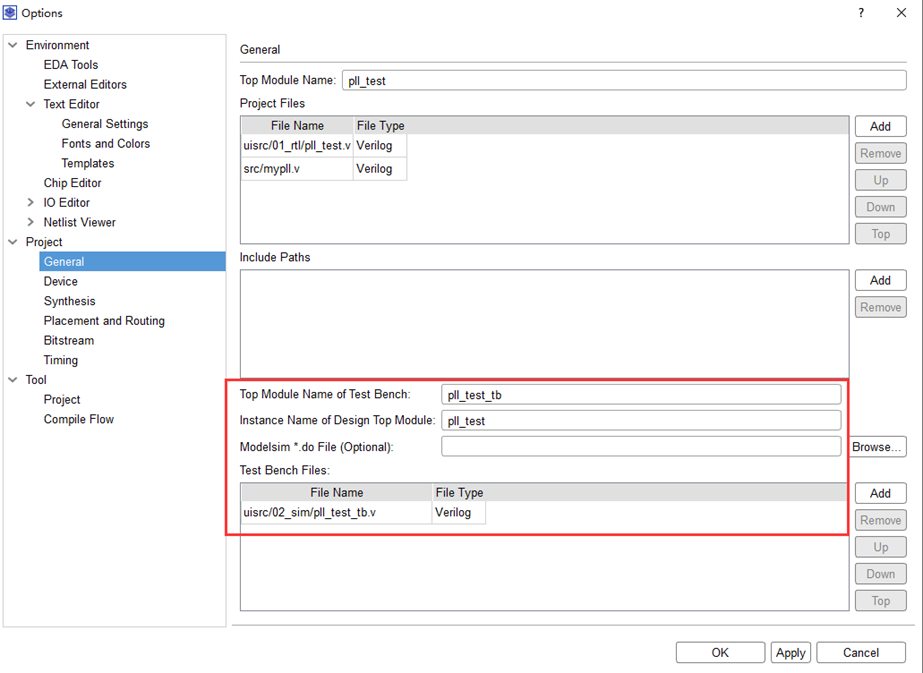

2.1仿真设置

双击Settings

设置modelsim的安装路径

设置仿真文件

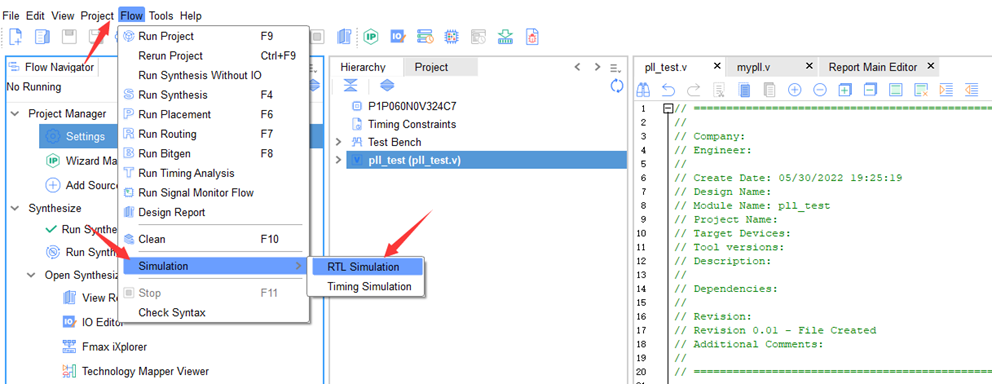

2.2启动仿真

在菜单Flow->Simulation->RTL Simulation启动仿真(注意第一次仿真可以这样启动,后面修改了文件后也可以直接在modelsim中执行.do文件直接仿真)

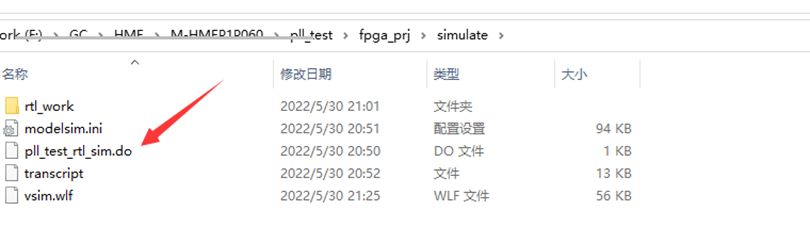

执行完成后,可以看到在对应工程的simulate路径下多了pll_test_rtl_sim.do文件

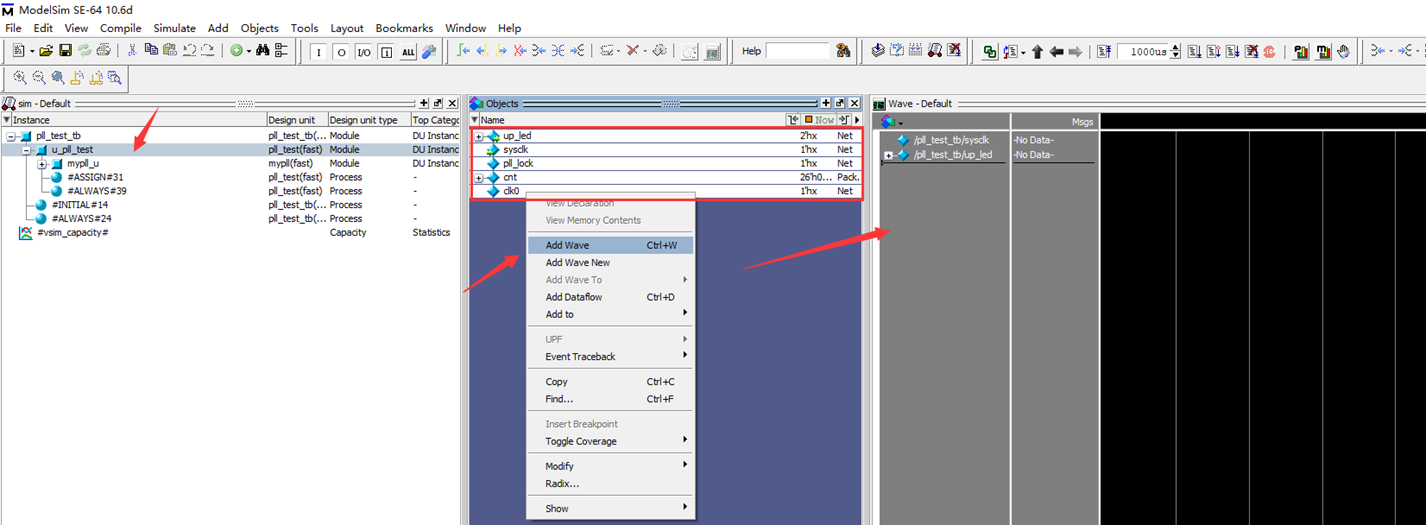

右击u_pll_test 添加需要观察的计数器等波形信号

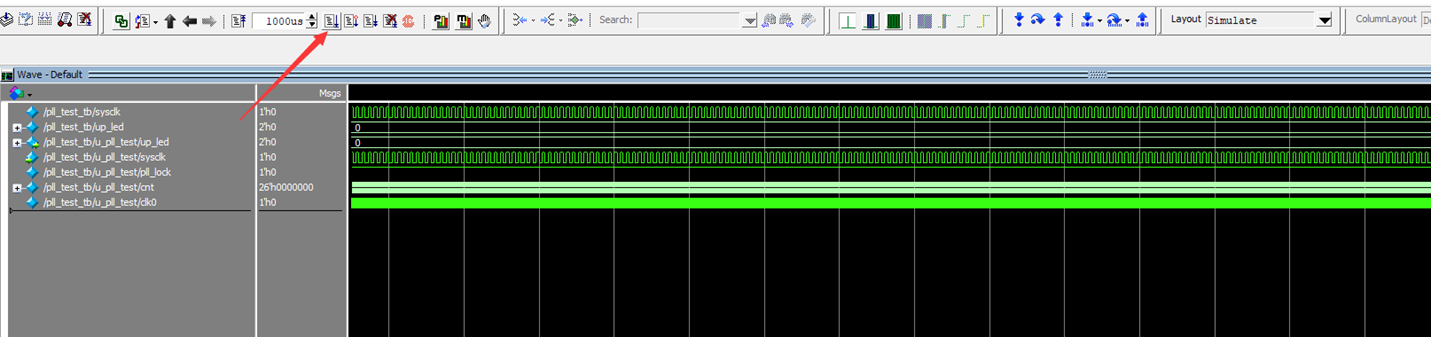

然后单击run就能仿真了

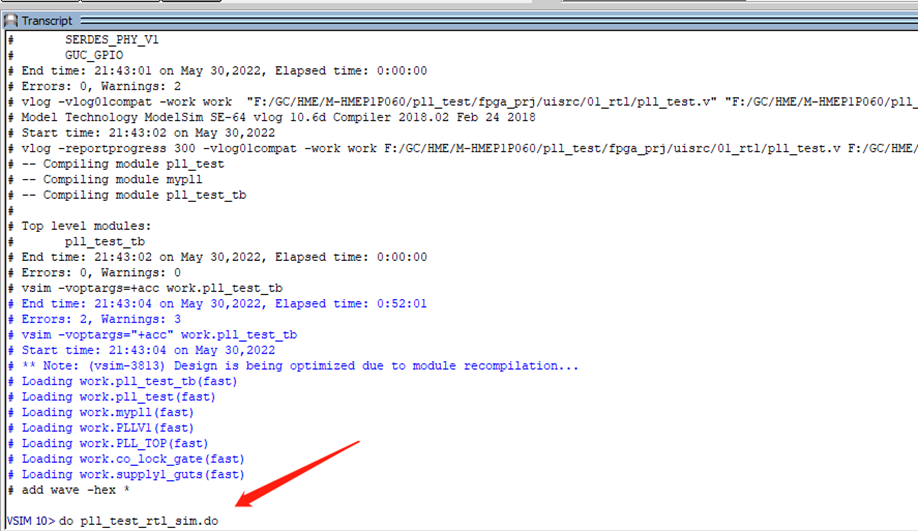

注意:当我们更新程序后,可以不需要从fuxi软件重新启动modelsim,可以在控制台输入do pll_test_rtl_sim.do然后回车直接执行。

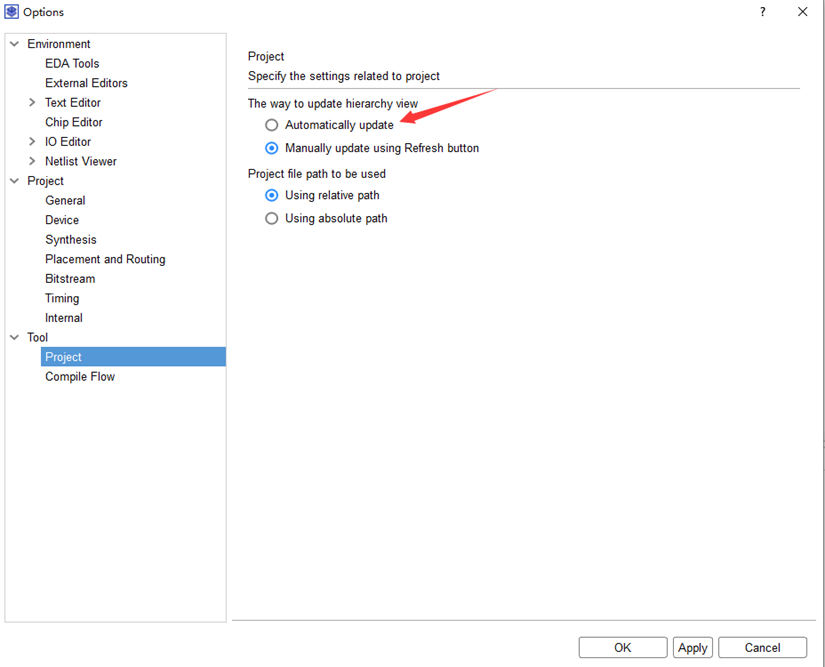

3Fuxi代码添加删除后注意事项

Fuxi默认会关闭自动刷新Hierarchy显示的功能,因此每次删除或者添加代码后,或者改版了代码的调用层次,可以手动刷新下就正常了(手动刷新可以防止自动刷新导致某些时候卡顿)。

如果要开启自动刷新可以设置如下:

下一个实验中我们增加PIN脚约束,以及添加在线逻辑分析仪在开发板上验证结果。

本文来米联客(milianke),作者:米联客(milianke),转载请注明原文链接:https://www.cnblogs.com/milianke/p/16330671.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 全程不用写代码,我用AI程序员写了一个飞机大战

· DeepSeek 开源周回顾「GitHub 热点速览」

· 记一次.NET内存居高不下排查解决与启示

· MongoDB 8.0这个新功能碉堡了,比商业数据库还牛

· .NET10 - 预览版1新功能体验(一)