XILINX FPGA CFGBVS硬件注意事项

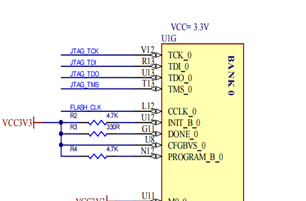

配置组电压选择(CFGBVS)引脚必须设置为高电平或低电平,以确定I/O电压支持的引脚在bank0,以及多功能引脚在bank14和15在配置时使用。CFGBVS是一个逻辑输入,VCCO_0和GND之间的引脚引用。当CFGBVS引脚为高(例如,连接VCCO_0提供3.3V或2.5V),在bank0上的配置和JTAG I/O支持在配置期间和配置后,在3.3V或2.5V下运行。

当CFGBVS引脚为Low时(例如,连接到GND),bank0的I/O支持1.8V或1.5V运行。

在1.2V时不支持配置。

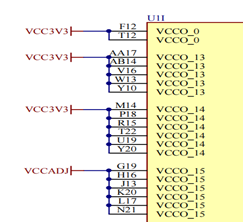

CFGBVS引脚设置决定I/O电压支持bank0在任何时候,和配置中的bank14和bank15。VCCO为每个配置组提供,如果在配置过程中使用CFGBVS,必须匹配CFGBVS的选择,如果CFGBVS与VCCO_0绑定,电压选择为2.5V或3.3V,若CFGBVS与GND绑定,则为1.8V或1.5V。

关于FPGA的配置模式。

注意:无论如何,在VCCO_0电压级别的bank0中始终支持JTAG接口配置模式。

设置CFGBVS引脚支持所需的配置I/O电压。(仅支持Spartan-7、Artix-7和Kintex-7 FPGA配置模式)见下表:

配置模式 | Bank使用 | 配置I/O电压 | Bank0 Vcco_0 | Bank14 Vcco_14 | Bank15 Vcco_15 | CFGBVS |

JTAG(only) | 0 | 3.3V | 3.3V | Any | ||

2.5V | 2.5V | Any | Any | VCCO-0 | ||

1.8V | 1.8V | Any | Any | |||

1.5V | 1.5V | Any | Any | GND | ||

Serial, SPI, or SelectMAP | 0,14 | 3.3V | 3.3V | 3.3V | Any | VCCO-0 |

2.5V | 2.5V | 2.5V | Any | VCCO-0 | ||

1.8V | 1.8V | 1.8V | Any | GND | ||

1.5V | 1.5V | 1.5V | Any | GND | ||

BPI | 0,14,15 | 3.3V | 3.3V | 3.3V | 3.3V | VCCO-0 |

2.5V | 2.5V | 2.5V | 2.5V | VCCO-0 | ||

1.8V | 1.8V | 1.8V | 1.8V | GND | ||

1.5V | 1.5V | 1.5V | 1.5V | GND |

下图所演示的为CFGBVS接入3.3V后bank0和bank14、15可接入的电压。

本文来米联客(milianke),作者:米联客(milianke),转载请注明原文链接:https://www.cnblogs.com/milianke/p/16122583.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号