cache verilog实现

cache原理: https://www.cnblogs.com/mikewolf2002/p/10984976.html

cache的verilog实现

实现的cache是16k, 4way组相连cache,每个set是256 个cacheline,每个cacheline是16 byte,所以总的size是256*4*16=16k byte。

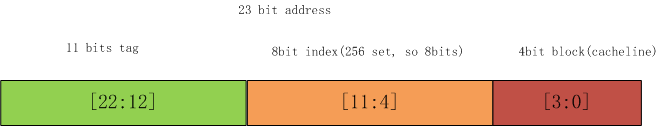

我们用23bit物理地址,如下图所示,低4位位cacheline内部的字节地址,因为cacheline size是16byte,所以用4位表示,因为每个set是256个cacheline,所以index用8位表示,其余的12-22位为tag位。

因为

浙公网安备 33010602011771号

浙公网安备 33010602011771号