vcs+Makefile实现简单的testbench

网络上找的文章,实现了一遍。

步骤如下:

1. 创建verilog代码, 包括8位加法器代码和testbench代码。

adder8.v

module adder8 ( input clk, input [7:0] a_i, input [7:0] b_i, output reg [8:0] c_o ); always @ (posedge clk) begin c_o <= a_i + b_i; end endmodule

adder8_tb.v

// TB_SEED is random seed

`ifndef TB_SEED

`define TB_SEED 0

`endif

module adder8_tb();

wire [8:0] result;

reg [7:0] input_0;

reg [7:0] input_1;

reg clk;

// clk2 is delay of clk, is used to verify result

wire #5 clk2;

assign clk2 = clk;

initial begin

$fsdbDumpfile("adder8.fsdb");

$fsdbDumpvars();

$display("TB_SEED is %d", `TB_SEED);

clk = 0;

input_0 = 8'd0;

input_1 = 8'd0;

#10000

$display("All test PASS!");

$finish;

end

// system clk is 50MHz

always begin

#10 clk = ~clk;

end

//generate random input

always @ (negedge clk) begin

input_0 = $random() % 256;

input_1 = $random() % 256;

end

//get verified output

always @ (posedge clk2) begin

if ((input_0 + input_1) != result) begin

$display("Test failed for %x + %x = %x", input_0, input_1, result);

$finish;

end else begin

$display("%x + %x = %x", input_0, input_1, result);end

end

//instantiate adder8

adder8 dut(

.clk(clk),

.a_i(input_0),

.b_i(input_1),

.c_o(result)

);

endmodule

2.编写Makefile文件,

VCS= vcs -sverilog -timescale=1ns/1ns +vpi -l build.log -debug_access+all SIMV = ./simv -l simv.log ifndef TB_SEED TB_SEED = 1024 endif all: comp run comp: $(VCS) +define+TB_SEED=$(TB_SEED) +incdir+. \ adder8.v \ adder8_tb.v run: $(SIMV) +fsdbfile+top.fsdb dbg: verdi -f file.f -ssf top.fsdb & clean: rm -rf core csrc simv* vc_hdrs.h ucli.key urg* *.log *.fsdb novas.* verdiLog

注意:Makefile里面的空格排版位tab键。

file.f里面内容为:

adder8_tb.v

adder8.v

3.

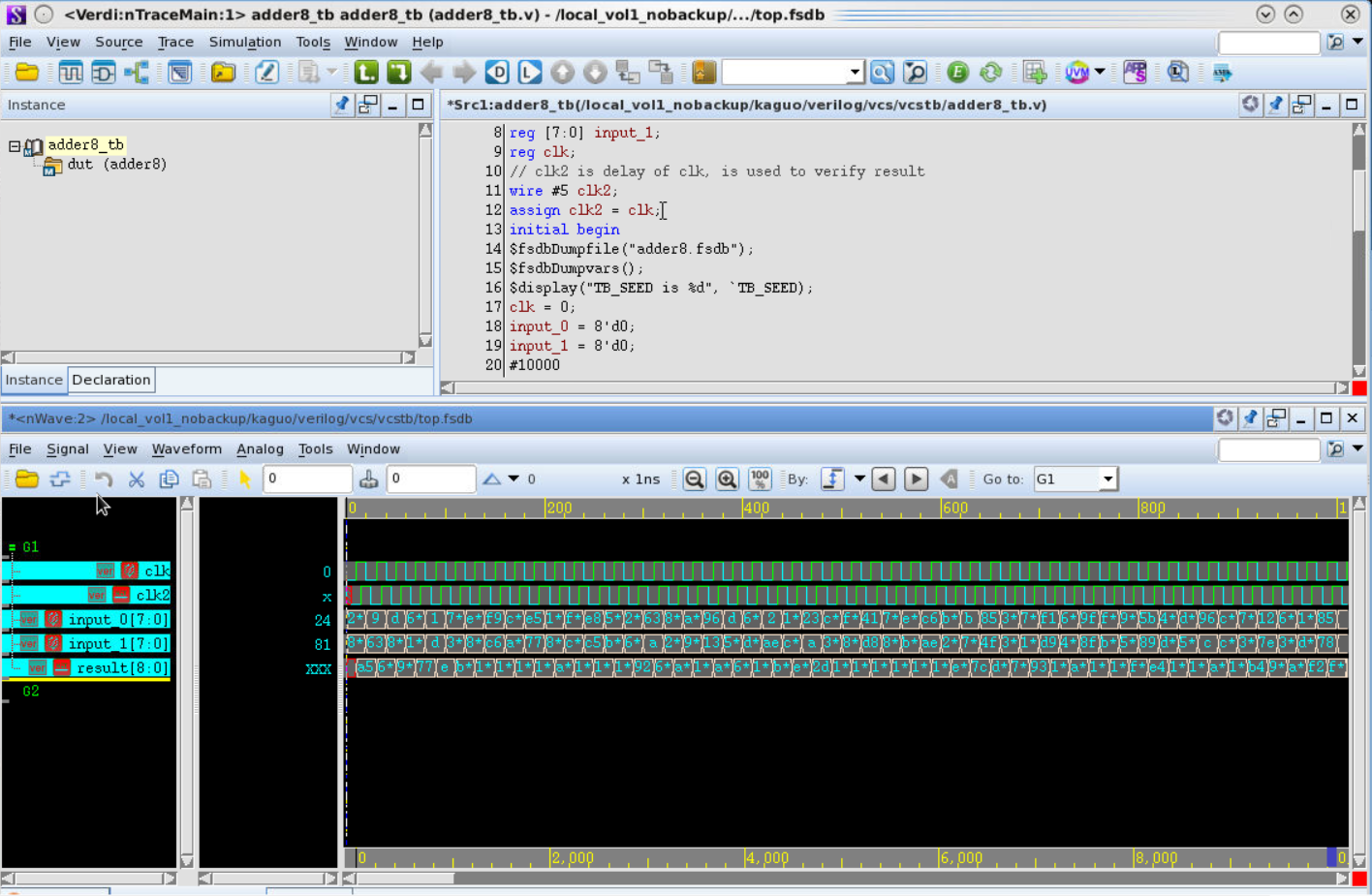

编译项目: Make

清除项目: Make clean

查看波形:Make dbg

编译日志文件为:build .log

仿真日志文件为:simv.log

仿真结果为:

浙公网安备 33010602011771号

浙公网安备 33010602011771号