quartus II输入原理图及仿真步骤

在Quartus II中输入原理图以及实现仿真是学习基本数字电路的好方法。下面以一个基本的D锁存器为例,在quartus II 13.0中一步一步来实现原理图输入以及仿真过程。

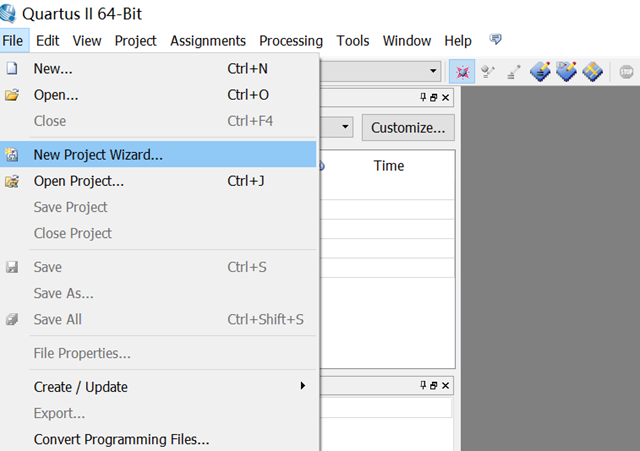

1,创建工程

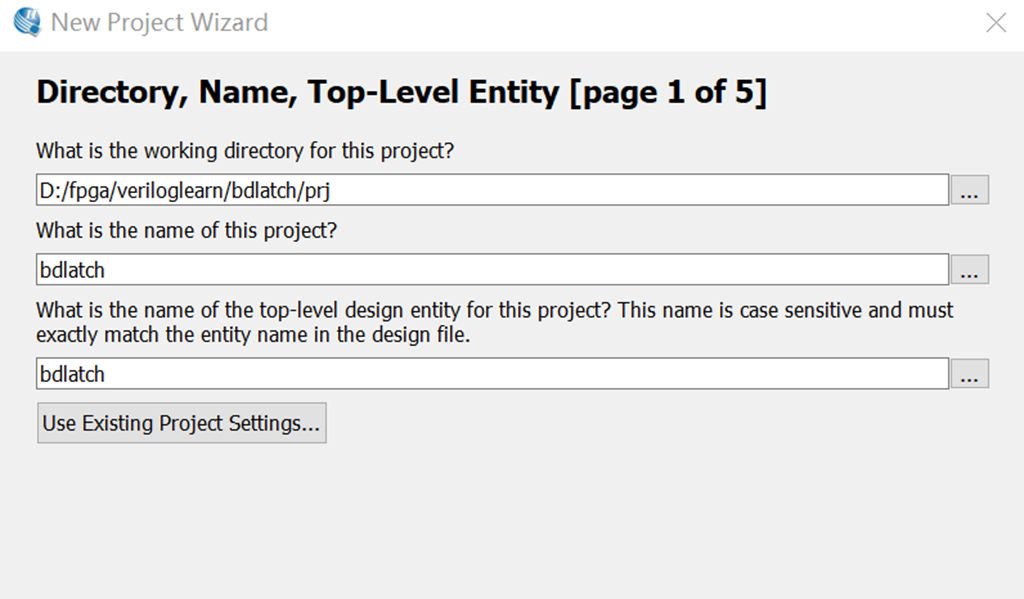

指定工程名字以及顶层文件名

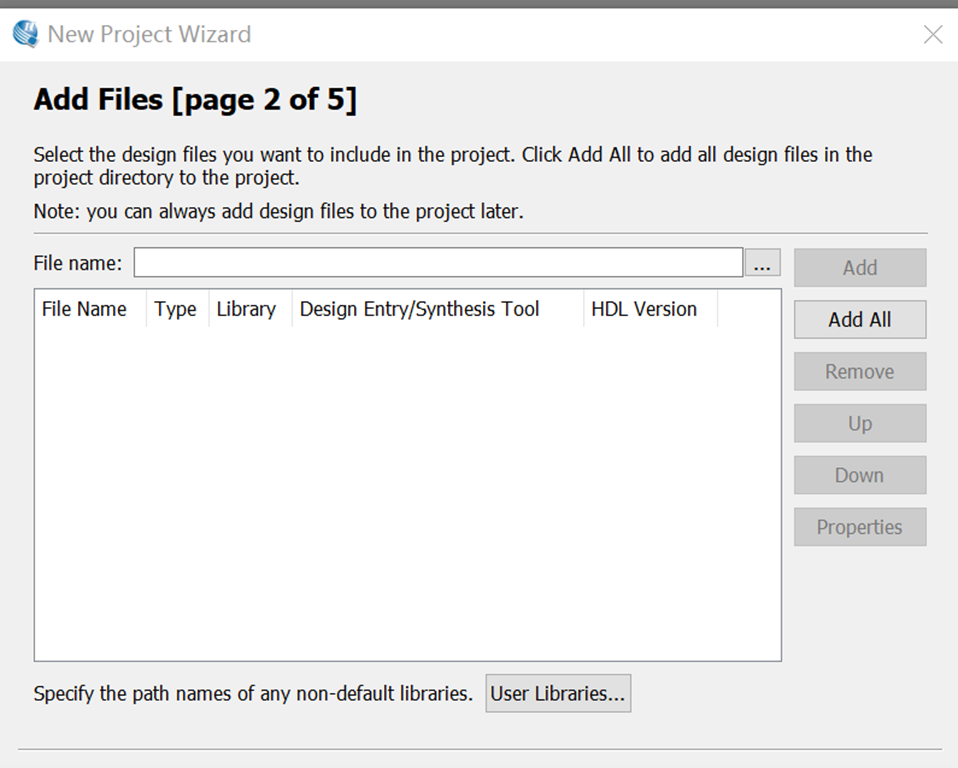

跳过。。。。

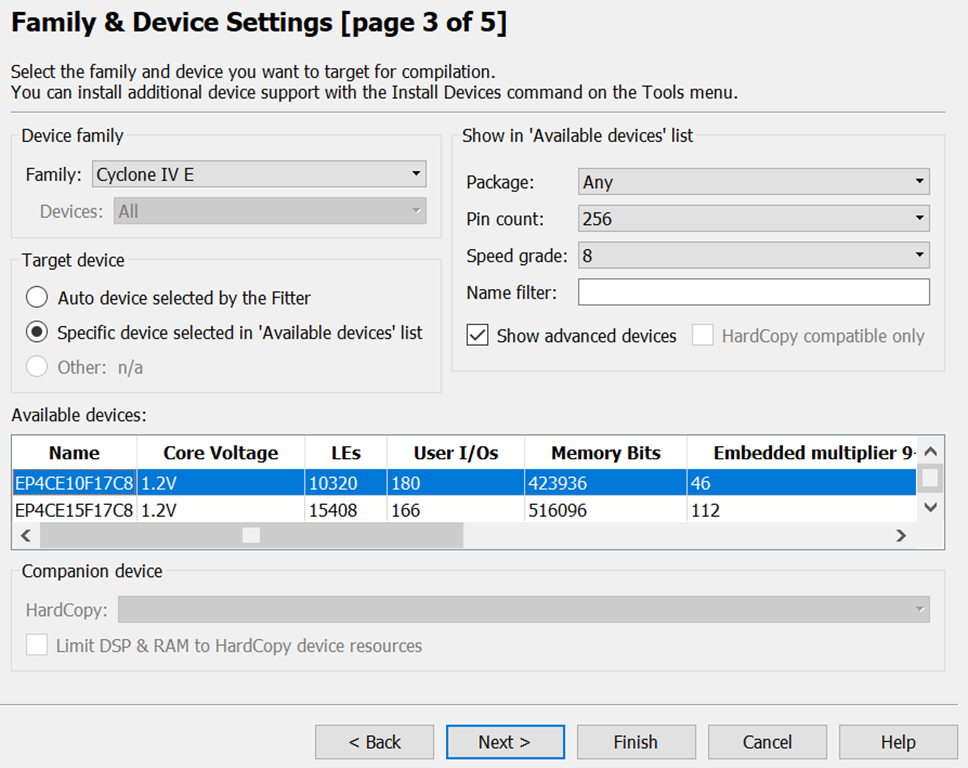

我用的是小梅哥的AC620开发板,按下面的图进行选择:

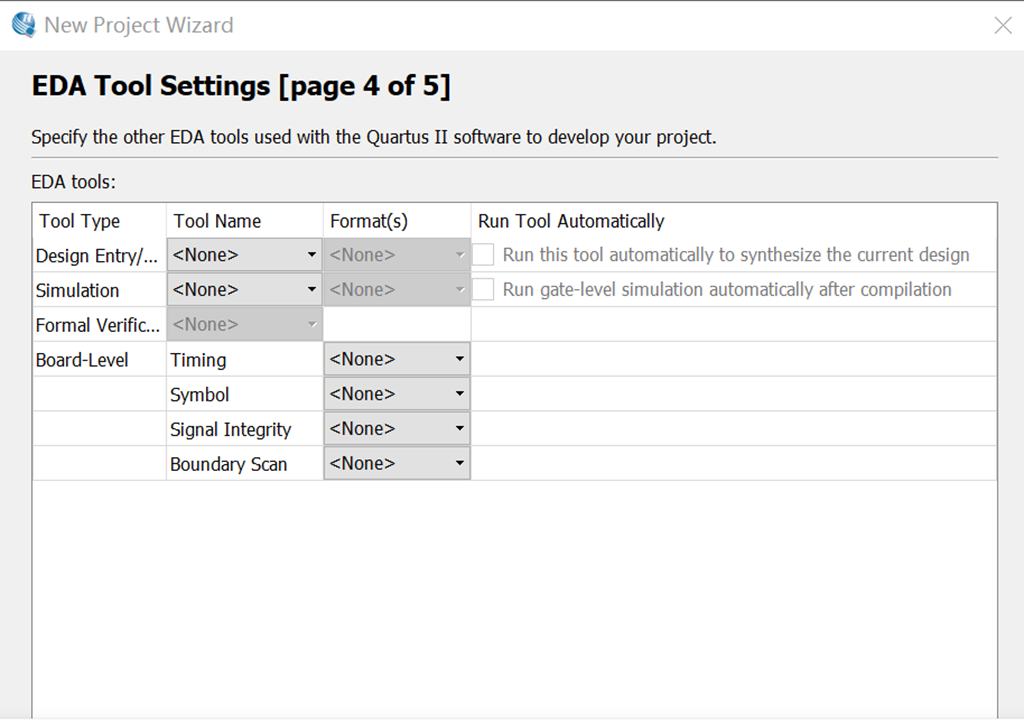

因为输入原理图以及用波形文件来仿真,所以EDA工具-simulation中选None

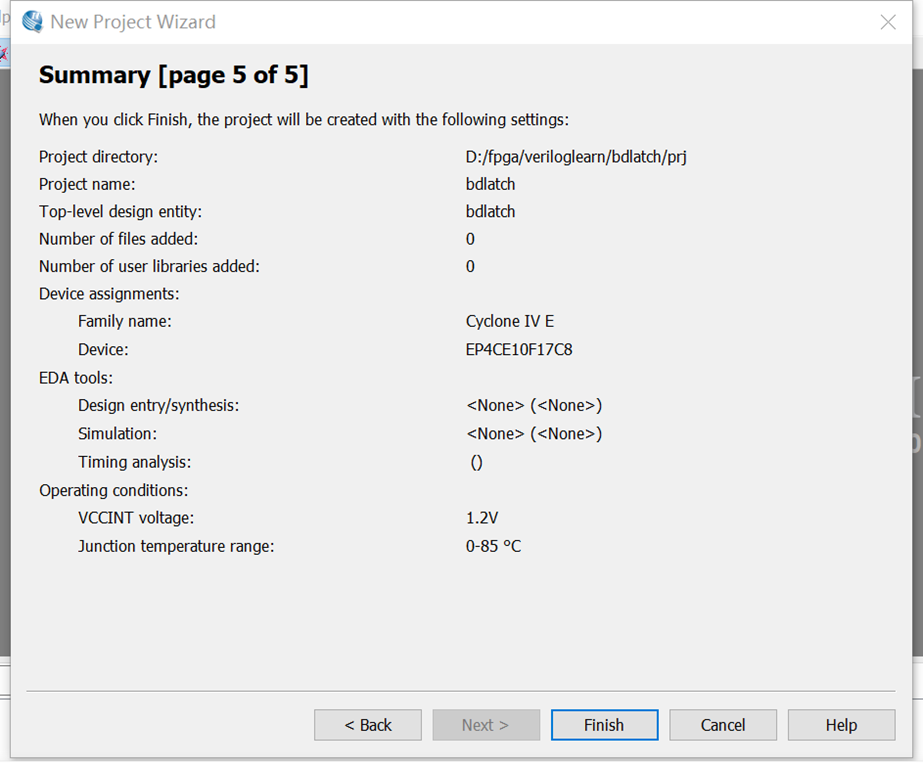

点finish,完成工程创建。

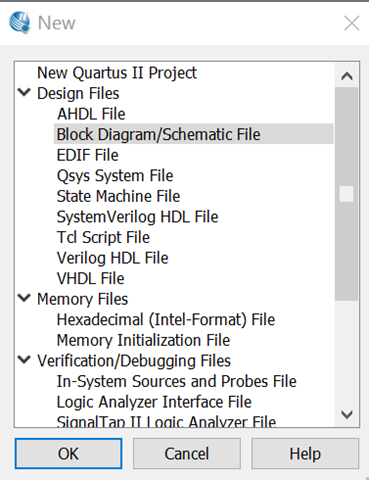

随后,创建一个波形文件。

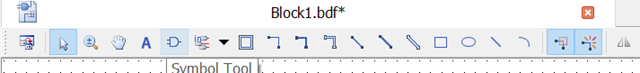

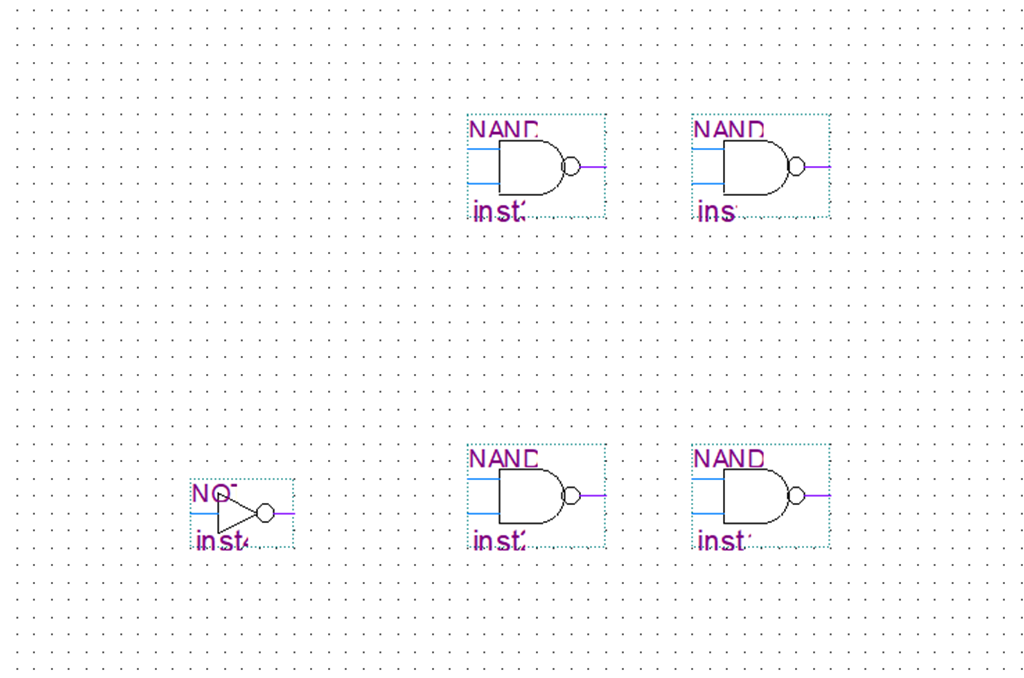

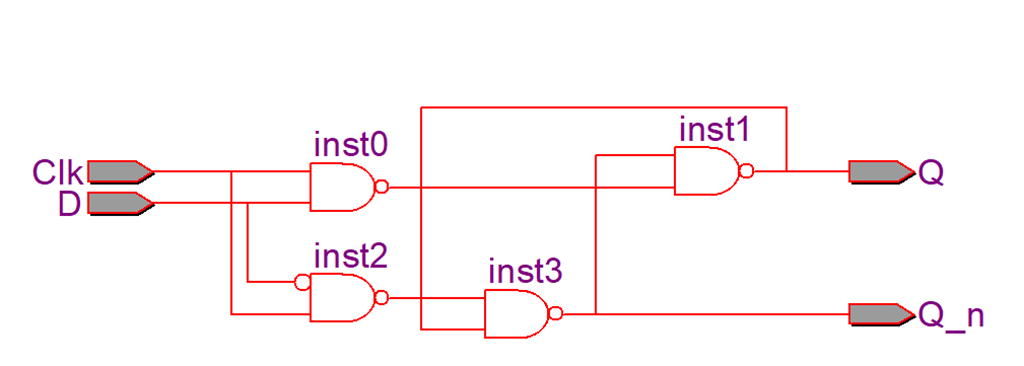

选择nand2,二个输入的与非门,依次添加四个and2和一个非门not

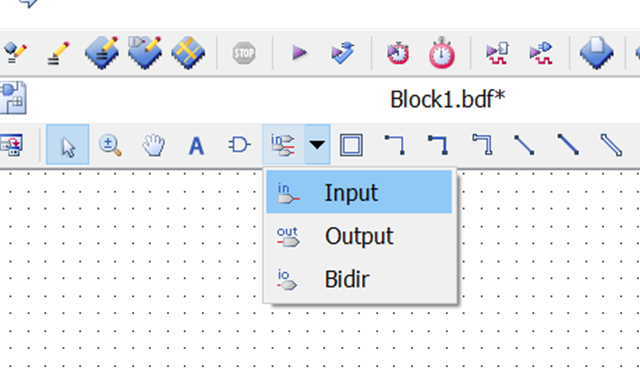

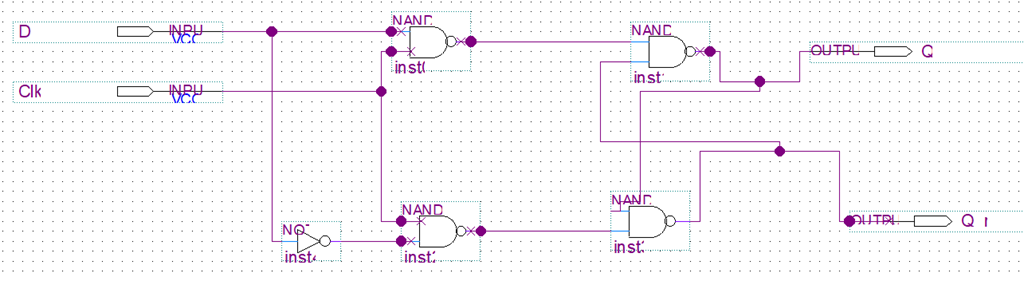

通过工具栏上面输入输出工具,以及连线工具,设计出以下的电路图。

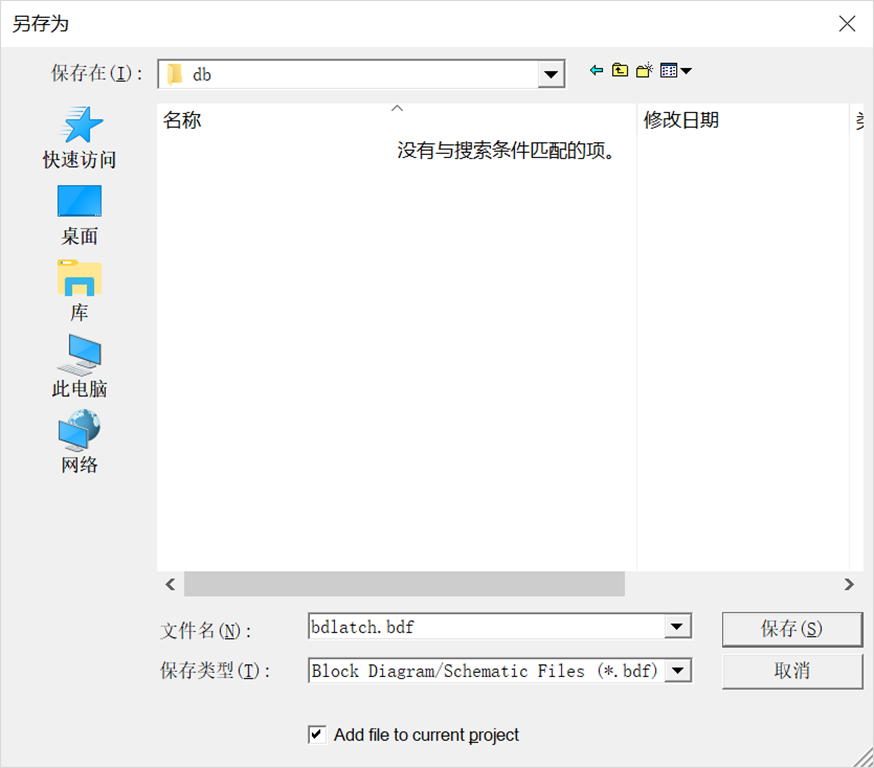

保存电路图为:

启动分析与综合,编译原理图文件。如果有编译错误,修改原理图,直到没有错误。也要检查警告信息,看是否连线连接正确。

编译后,用rtl viewer,可以看到下面硬件电路图。

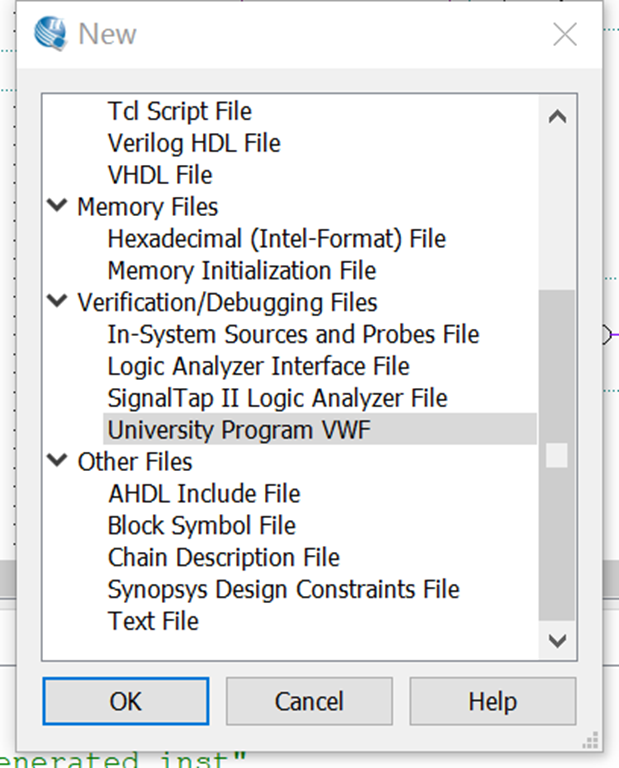

创建vwm格式波形文件,输入激励源。

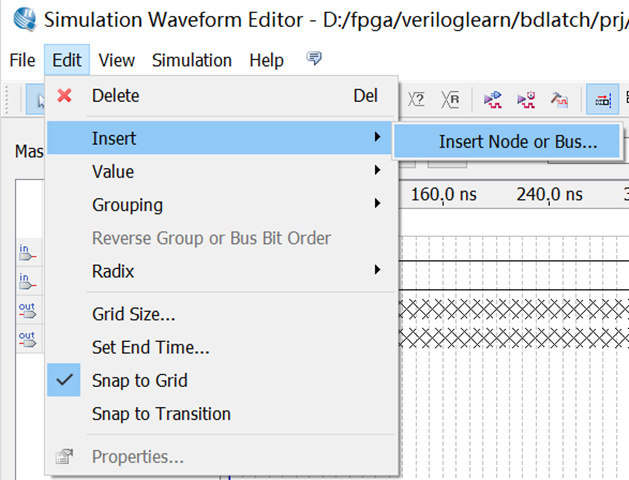

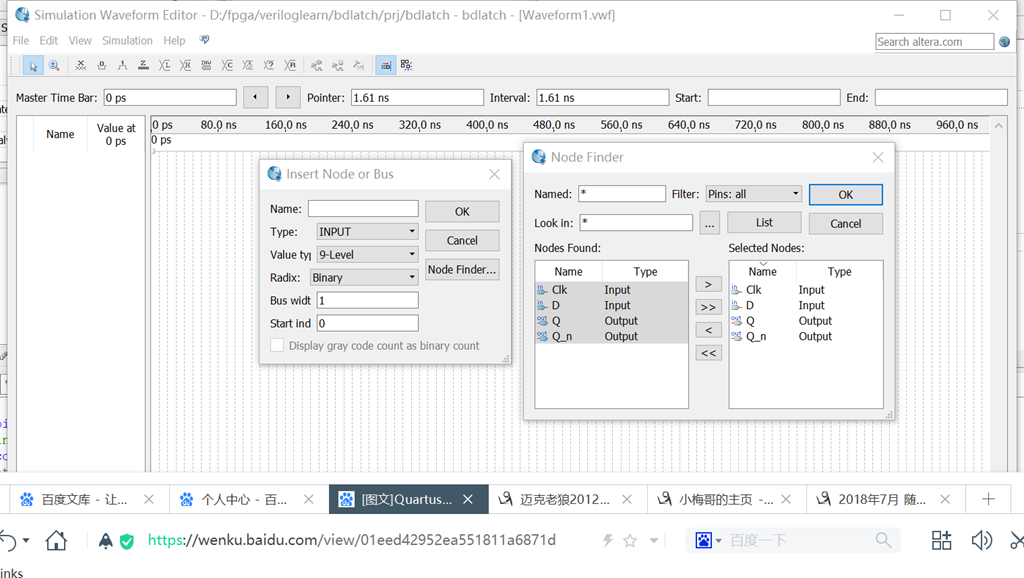

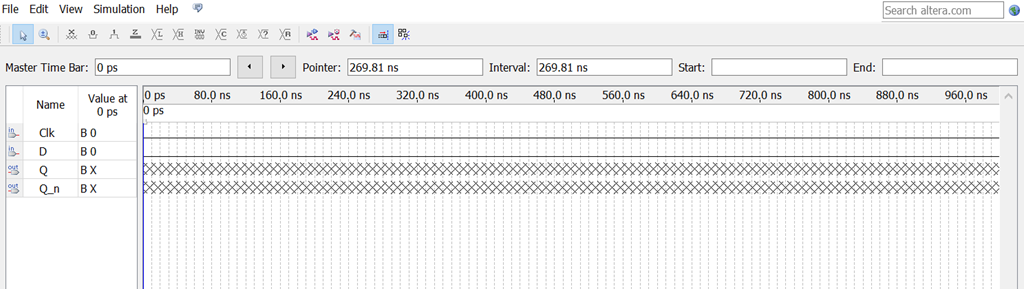

插入Node和bus后,得到下面的波形

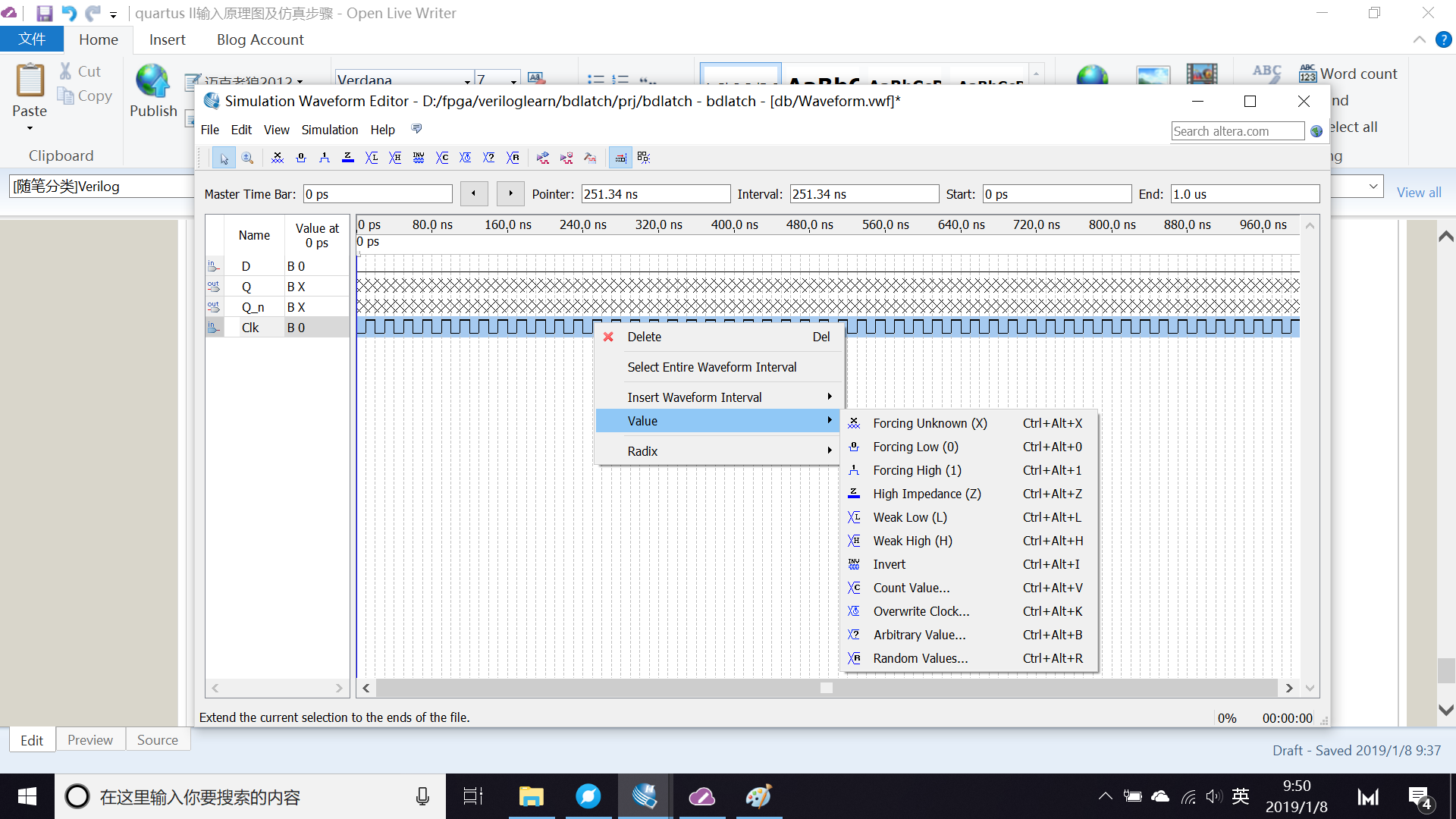

通过工具栏上面工具按钮,编辑输入Clk和D信号。

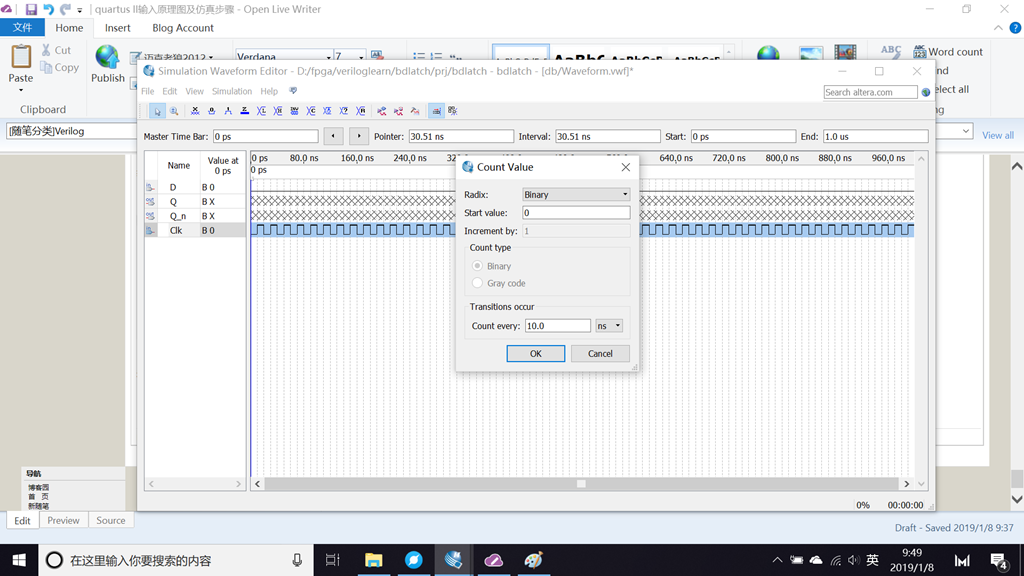

产生时钟信号:

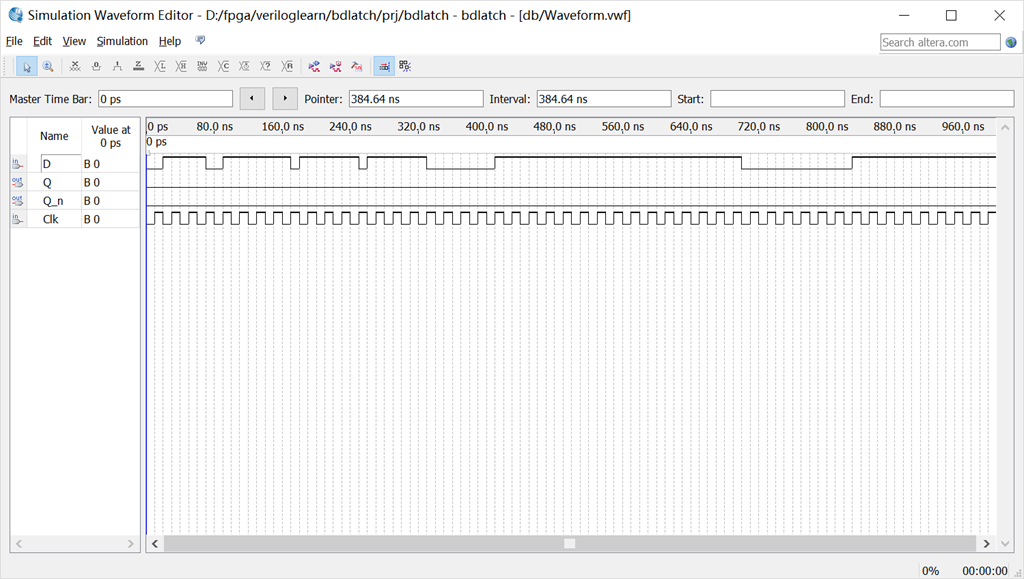

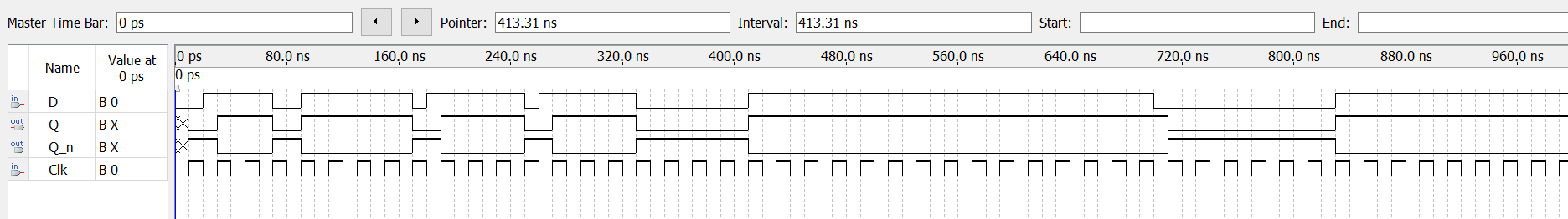

用鼠标选择D,Q信号Q_n,,进行编辑,编辑好后,运行功能仿真。

功能仿真后的波形,满足D latch的时序,全编译后,也可以运行时序仿真。

浙公网安备 33010602011771号

浙公网安备 33010602011771号