s3c2440系统时钟

本文转载自mr_raptor的专栏,感谢mr_raptor大神。

http://blog.csdn.net/mr_raptor/article/details/6555734

系统时钟

MINI2440开发板在没有开启时钟之前,整个开发板全靠一个12MHz的晶振提供频率来运行,也就是说CPU,内存,UART等需要用到时钟频率的硬件全工作在12MHz下,而s3c2440A可以正常工作在400MHz下,两者速度相差可想而知,就好比牛车和动车。

如果CPU工作在12MHz频率下,开发板的使用效率非常低,所有依赖系统时钟工作的硬件,其工作效率也很低,比如,我们电脑里经常提到的超频,超频就是让CPU工作在更高的频率下,让电脑运算速度更快,虽然频率是越高越好,但是由于硬件特性决定了任何一个设备都不可能无止境地超频,电脑超频要考虑到CPU或主板发热过大,烧坏的危险,同样开发板的主板上的外设和CPU也有一个频率限度,ARM920T内核的s3c2440的最高正常工作频率如下:

FCLK:400MHz

HCLK:100MHz

PCLK:50MHz

系统工作时钟频率

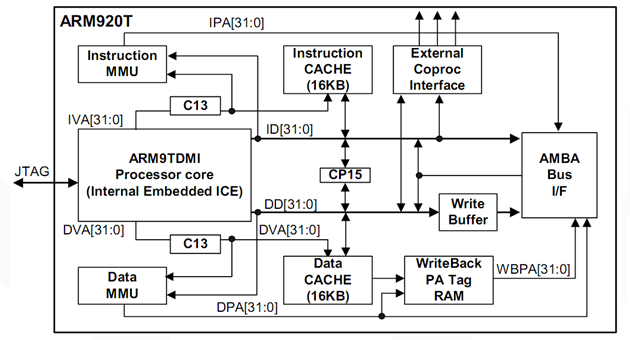

图1 ARM920T内核结构

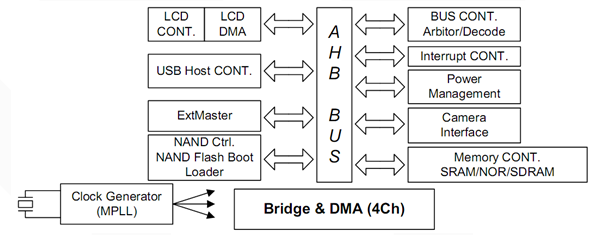

图2 s3c2440 AHB总线上挂接硬件

HCLK主要为s3c2440 AHB总线(Advanced High performance Bus)上挂接硬件提供工作频率,AHB总线主要挂接有内存,NAND,LCD控制器等硬件,如图2所示。

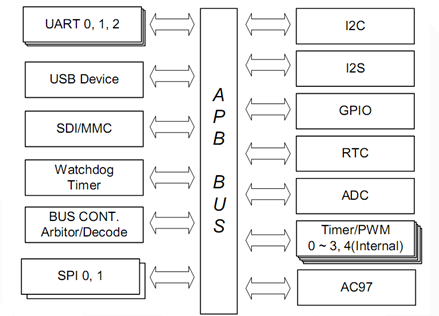

图3 s3c2440 APB总线上挂接硬件

PCLK主要为APB总线提供工作频率,如图3所示,APB总线主要挂接UART串口,Watchdog等硬件控制器。

也就是说,对于一些需要时钟工作的硬件,如果切断其时钟源,就不会再工作,从而达到降低功耗的目的,这也是便携嵌入式设备里的一个特点。

时钟源:为了减少外界环境对开发板电磁干扰,降低制作成本,通常开发板的外部晶振时钟频率都很低,MINI2440开发板由12MHz的晶振来提供时钟源,要想让CPU运行在更高的频率就要通过时钟控制逻辑单元PLL(锁相环)来提高主频。

s3c2440里有两个PLL:MPLL和UPLL,MPLL用来产生FCLK,HCLK,PCLK的高频工作时钟,UPLL用来为USB提供工作频率。

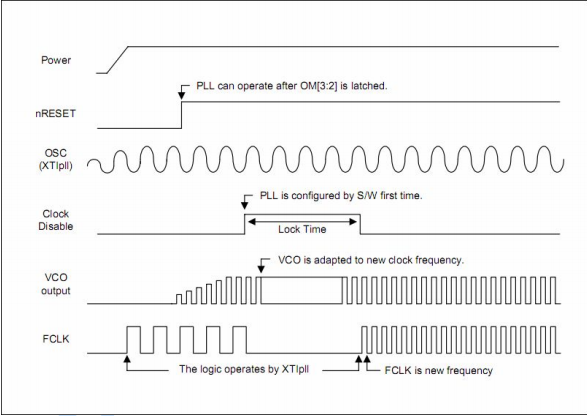

图4 系统时钟初始化时序

开发板上电后,晶振OSC开始提供晶振时钟,由于系统刚刚上电,电压信号等还不稳定,这时复位信号(nRESET)拉低,这时MPLL虽然默认启动,但是如果不向MPLLCON中写入值,那么外部晶振则直接作为系统时钟FCLK,经过几毫秒后,复位信号上拉,CPU开始取指运行,这时可以通过代码设置启动MPLL,MPLL启动需要一定锁定时间(LockTime),这是因为MPLL输出频率还没稳定,在这期间FCLK都停止输出,CPU停止工作,过了LockTime后时钟稳定输出,CPU工作在新设置的频率下,这时可以通过设置FCLK,HCLK和PCLK三者的频率比例来产生不同总线上需要的不同频率,下面详细介绍开启MPLL的过程:

1、设置LockTime变频锁定时间

2、设置FCLK与晶振输入频率(Fin)的倍数

3、设置FCLK,HCLK,PCLK三者之间的比例

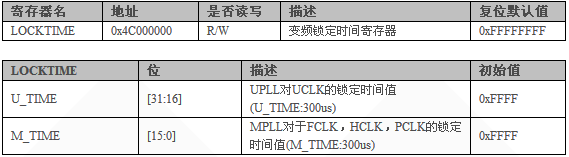

LockTime变频锁定时间由LOCKTIME寄存器(见下表1.1)来设置,由于变频后开发板所有依赖时钟工作的硬件都需要一小段时间调整,该时间计数通过设置LOCKTIME寄存器[31:16]来设置UPLL(USB时钟锁相环)调整时间,通过设置LOCKTIME寄存器[15:0]设置MPLL调整时间,这两个调整时间数值一般用其默认值即可。

表1.1 变频锁定时间寄存器(LOCKTIME)

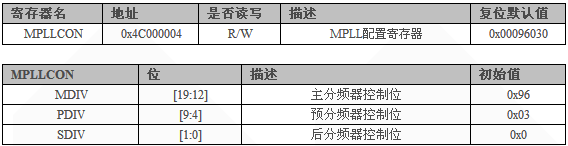

FCLK与Fin的倍数通过MPLLCON寄存器(见下表1.2)设置,三者之间的关系为:

MPLL(FCLK) = (2*m*Fin) / (p*2^s)

其中:m = MDIV + 8 , p = PDIV + 2 ,s = SDIV

当设置完MPLL之后,就会自动进入LockTime变频锁定时间,LockTime之后,MPLL输出稳定时钟频率。

表1.2 MPLL配置寄存器(MPLLCON)

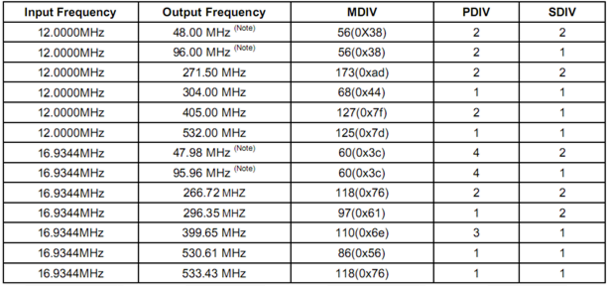

通过上述算法比较难以找到合适的PLL值,下表1.3给出了官方推荐的一些MPLL参考设置:

表1.3 官方推荐MPLL参考设置

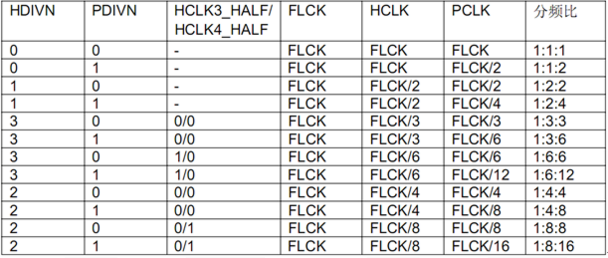

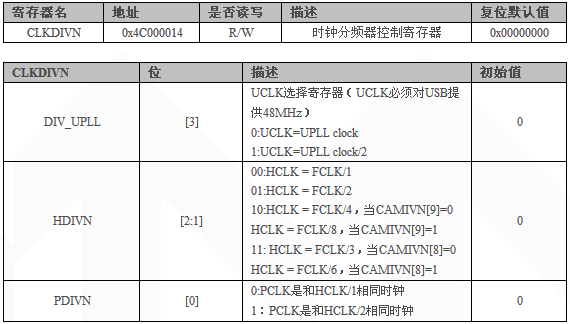

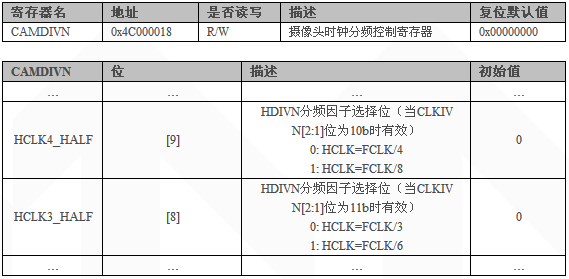

FCLK,HCLK,PCLK三者之间的比例通过CLKDIVN寄存器进行设置,s3c2440时钟设置时,还要额外设置CAMDIVN寄存器,如下表1.4,HCLK4_HALF,HCLK3_HALF分别与CAMDIVN[9:8]对应,下表列出了各种时钟比例:

表1.4 时钟比例设置

如果HDIV设置为非0,CPU的总线模式要进行改变,默认情况下FCLK = HCLK,CPU工作在fast bus mode快速总线模式下,HDIV设置为非0后,FCLK与HCLK不再相等,要将CPU改为asynchronous bus mode异步总线模式,可以通过下面汇编代码实现:

1 __asm{ 2 mrc p15, 0, r1, c1, c0, 0 /* 读取CP15 C1寄存器 */ 3 orr r1, r1, #0xc0000000 /* 设置CPU总线模式 */ 4 mcr p15, 0, r1, c1, c0, 0 /* 写回CP15 C1寄存器 */ 5 }

表1.5 时钟分频控制寄存器(CLKDIVN)

表1.6 摄像头时钟分频寄存器(CAMDIVN)

浙公网安备 33010602011771号

浙公网安备 33010602011771号