基于FPGA的图像双线性插值算法verilog实现,包括tb测试文件和MATLAB辅助验证

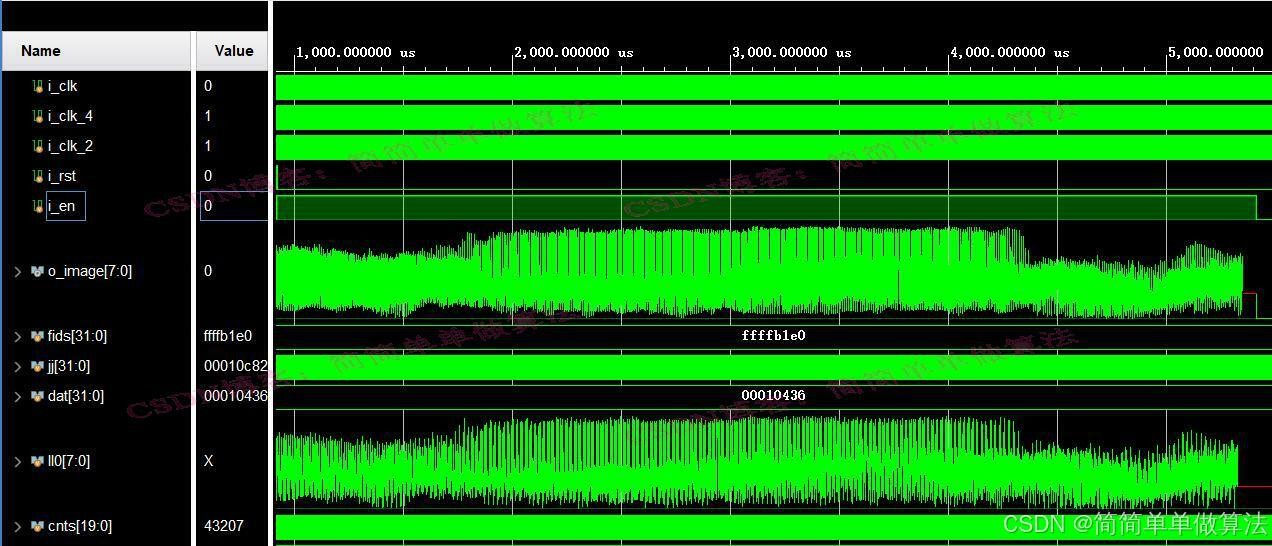

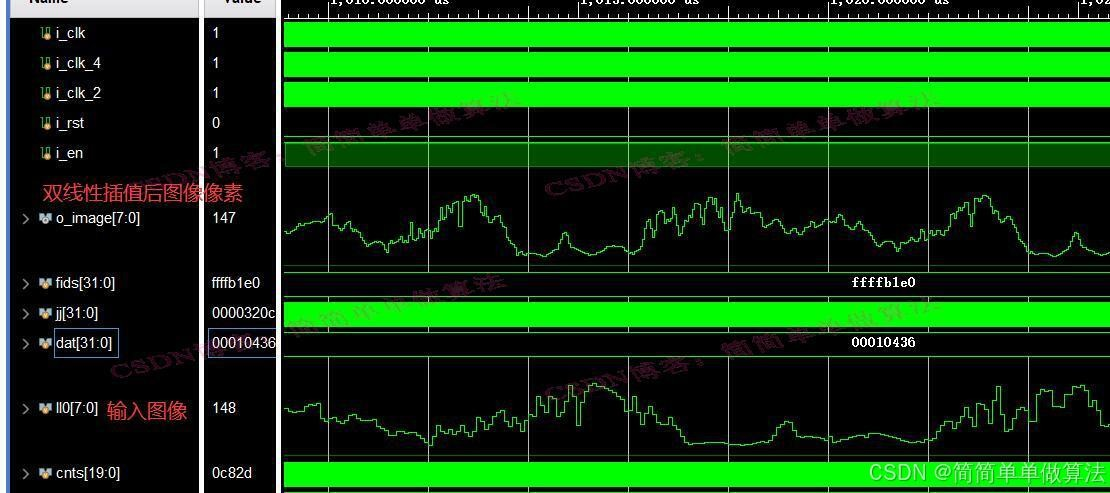

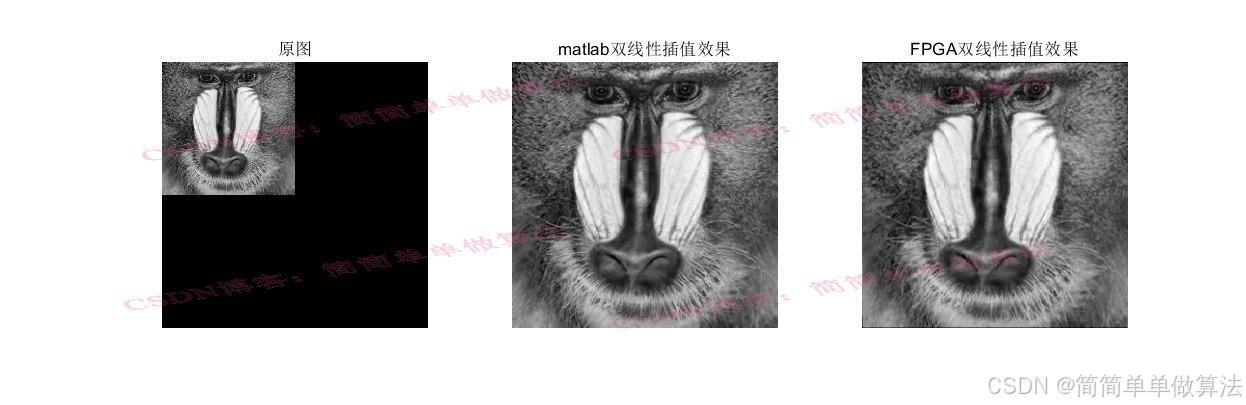

1.算法运行效果图预览

(完整程序运行后无水印)

这里实现的是256*256双线性插值到512*512的系统模块

局部放大:

将数据导入到matlab,得到插值效果图:

2.算法运行软件版本

matlab2022a

vivado2019.2

3.部分核心程序

(完整版代码包含详细中文注释和操作步骤视频)

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/10/04 05:24:01

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

............................................................................

wire [8:0]tmp1 = mat11+mat21;

wire [8:0]tmp2 = mat12+mat22;

reg[7:0]AxB1;

reg[7:0]AxB2;

reg[7:0]AxBxC;

wire [8:0]tmp3 = AxB1+AxB2;

always @(posedge i_clk_2 or posedge i_rst)

begin

if(i_rst)

begin

AxB1 <= 8'd0;

AxB2 <= 8'd0;

AxBxC <= 8'd0;

end

else begin

if(cnt_r8[0] == 1'b0)

begin

AxB1 <= mat11;

AxB2 <= mat12;

end

if(cnt_r8[0] == 1'b1)

begin

AxB1 <= tmp1[8:1];

AxB2 <= tmp2[8:1];

end

if(cnt_c9[0] == 1'b0)

begin

AxBxC <= AxB1;

end

if(cnt_c9[0] == 1'b1)

begin

AxBxC <= tmp3[8:1];

end

end

end

assign o_image=AxBxC;

endmodule

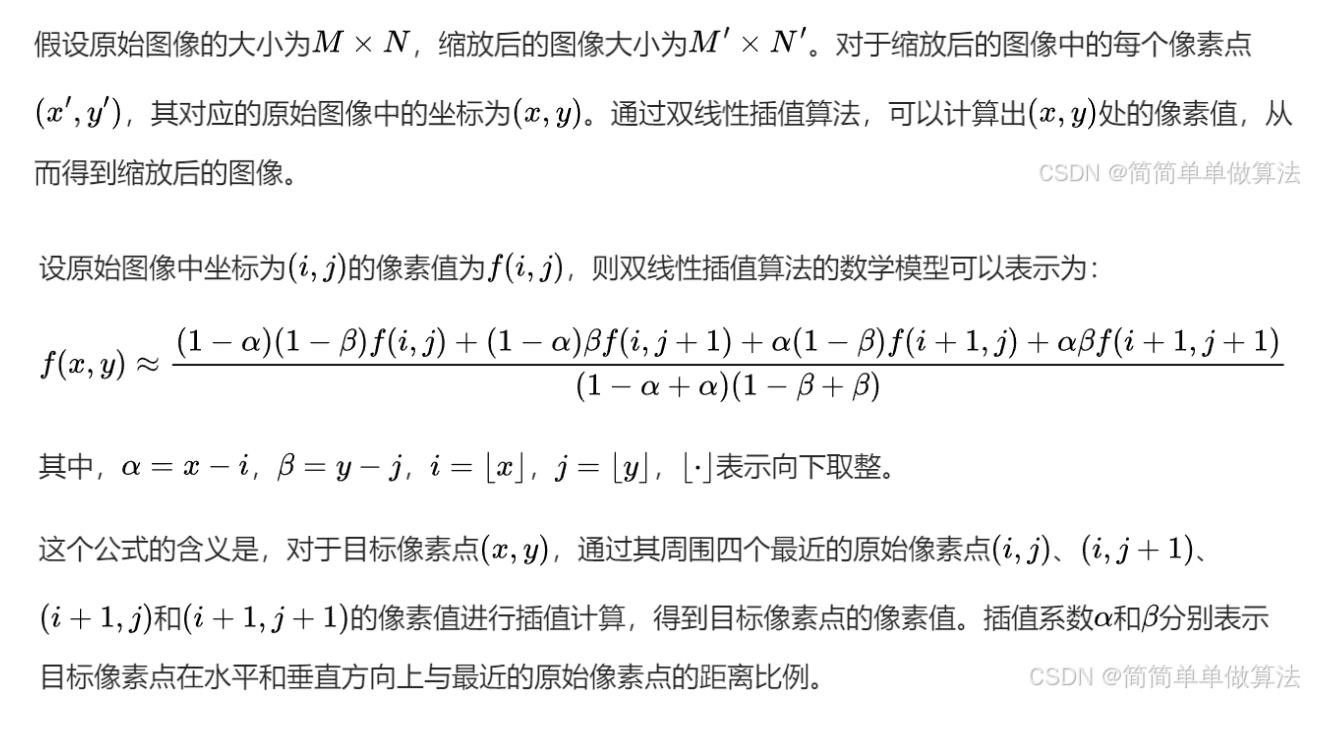

4.算法理论概述

在图像处理领域,图像缩放是一项常见的任务。图像双线性插值算法是一种常用的图像缩放方法,它可以在不损失图像质量的前提下,对图像进行放大或缩小。随着现场可编程门阵列(FPGA)技术的不断发展,基于 FPGA 的图像双线性插值算法成为了一种高效、灵活的图像缩放解决方案。

图像双线性插值算法是一种基于线性插值的图像缩放方法。它通过对图像中的每个像素点进行插值计算,得到缩放后的图像。

浙公网安备 33010602011771号

浙公网安备 33010602011771号