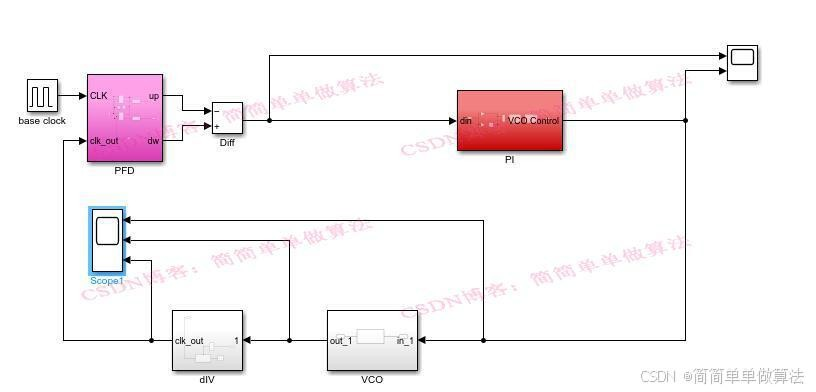

基于pi控制的数字锁相环simulink建模与仿真

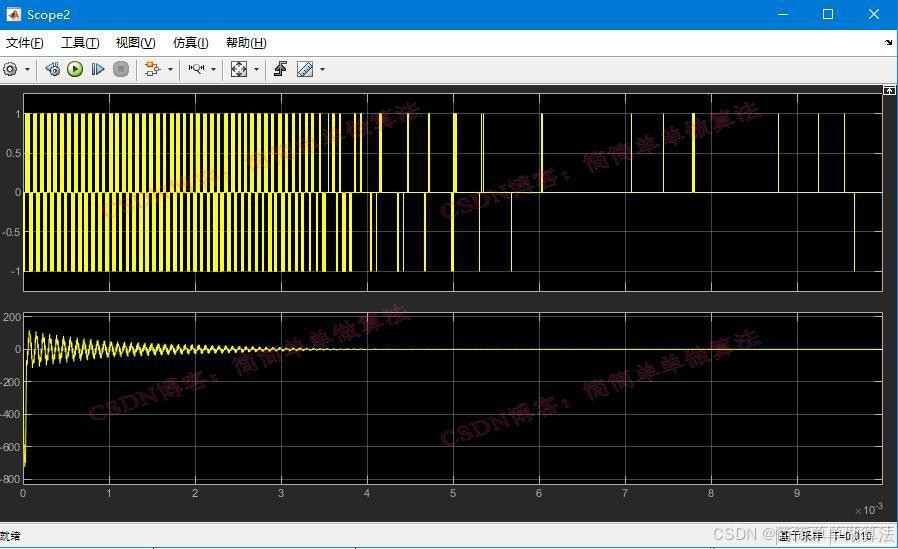

1.算法运行效果图预览

(完整程序运行后无水印)

2.算法运行软件版本

matlab2022a

3.部分核心程序

(完整版代码包含详细中文注释和操作步骤视频)

01_012m

4.算法理论概述

数字锁相环(DPLL, Digital Phase Locked Loop)是一种重要的电路系统,广泛应用于通信、信号处理、频率合成等领域,用于实现频率和相位的自动跟踪与锁定。基于PI控制器的数字锁相环是在传统的模拟锁相环基础上,利用数字信号处理技术实现的,它结合了比例积分控制器(Proportional-Integral Controller, PI)的特性,以提高系统的稳定性、精确度和灵活性。

数字锁相环主要由四个基本部分组成:鉴相器(Phase Detector, PD)、环路滤波器(Loop Filter, LF)、数字频率控制器(Numerically Controlled Oscillator, NCO)和分频器(Divider)。

工作原理

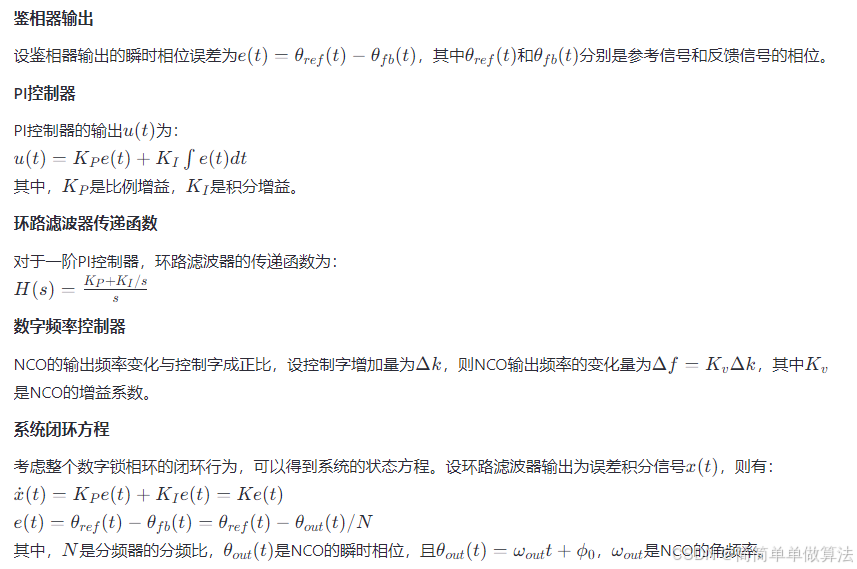

鉴相器(PD): 接收参考信号fref和反馈信号ffb,输出它们之间的相位差信号e(t)。在数字实现中,通常采用数字鉴相器,如绝对相位差鉴相器、正交鉴相器等。

环路滤波器(LF): 接收鉴相器的输出信号,通常设计为低通滤波器,用于滤除高频噪声,同时对相位误差进行积分和放大处理。基于PI控制的环路滤波器,其输出为误差信号的比例项和积分项之和。

数字频率控制器(NCO): 根据环路滤波器的输出调整其内部频率控制字,进而改变输出信号的频率fout,这个信号经过分频后成为反馈信号ffb。

分频器(Divider): 将NCO输出的信号分频,使其与参考信号保持预定的频率比,形成闭环系统。

系统达到锁定状态时,相位误差趋于稳定或为一个固定值,即limt→∞e(t)=ess。系统稳定性取决于环路滤波器的设计,特别是PI控制器参数的选择。通常,要求环路的开环增益在穿越单位圆频率处小于1,以保证系统稳定。基于PI控制的数字锁相环通过数字化的设计,提供了灵活、精确的频率和相位控制手段,广泛应用于各种高精度的信号处理和同步系统中。其核心在于PI控制器的设计与参数调优,以及对整个环路动态特性的深入理解,以确保系统快速响应、稳定锁定并具备良好的噪声抑制能力。

浙公网安备 33010602011771号

浙公网安备 33010602011771号