基于FPGA的图像累积直方图verilog实现,包含tb测试文件和MATLAB辅助验证

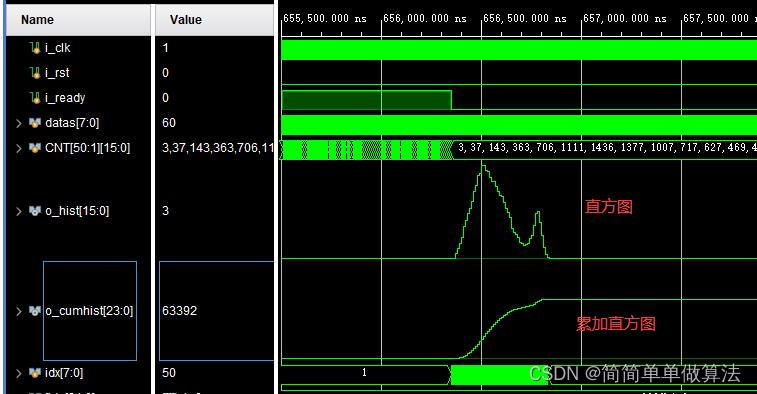

1.算法运行效果图预览

2.算法运行软件版本

Vivado2019.2

matlab2022a

3.算法理论概述

图像累积直方图是一种重要的图像特征表示方法,它统计了图像中像素值累加分布的情况,广泛应用于图像增强、对比度调整、颜色校正、图像分割、目标检测等领域。FPGA作为一种高性能、低功耗的可重构硬件平台,其并行处理能力和可定制化特性使得其在图像处理任务中展现出高效能优势。

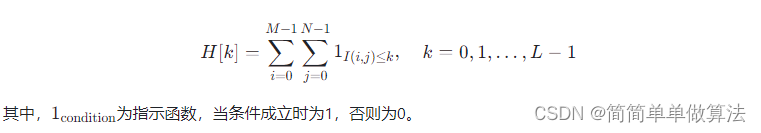

给定一幅灰度图像I(或彩色图像的某一通道),其尺寸为M×N,像素值范围为[0,−1][0,L−1],其中L为量化级别(如8位图像中L=256)。图像累积直方图H是一个长度为L的数组,其第k个元素H[k]表示图像中像素值小于等于k的像素个数之和。数学表达如下:

4.部分核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Design Name:

// Module Name: test_image

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module test_image;

reg i_clk;

reg i_rst;

reg i_ready;

reg [7:0] Tmp[0:100000];

reg [7:0] datas;

wire[15:0]o_hist;

wire[23:0]o_cumhist;

integer fids,jj=0,dat;

//D:\FPGA_Proj\FPGAtest\code2

initial

begin

fids = $fopen("D:\\FPGA_Proj\\FPGAtest\\code\\data.bmp","rb");

dat = $fread(Tmp,fids);

$fclose(fids);

end

initial

begin

i_clk=1;

i_rst=1;

i_ready=0;

#1000;

i_ready=1;

i_rst=0;

#655350;

i_ready=0;

end

always #5 i_clk=~i_clk;

always@(posedge i_clk)

begin

datas<=Tmp[jj];

jj<=jj+1;

end

im_hist im_hist_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_ready (i_ready),

.i_xin (datas),

.o_hist (o_hist),

.o_cumhist (o_cumhist)

);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号