基于FPGA的图像RGB转CMYK实现,包含testbench和MATLAB辅助验证程序

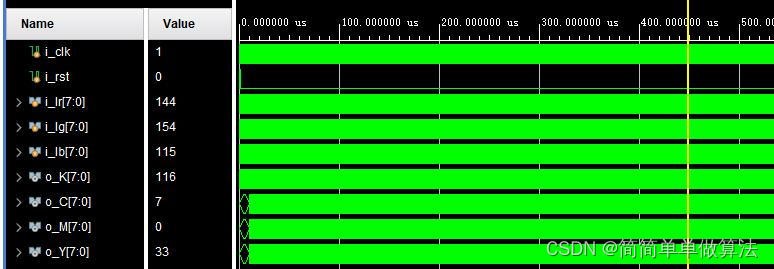

1.算法运行效果图预览

将仿真结果导入到matlab中,得到如下对比结果:

2.算法运行软件版本

matlab2022a,vivado2019.2

3.算法理论概述

基于FPGA的图像RGB转CMYK实现是一种将RGB图像转换为CMYK图像的硬件实现方法。下面将详细介绍其原理和数学公式。

3.1、RGB转CMYK的原理

RGB转CMYK是将RGB颜色空间转换为CMYK颜色空间的过程。RGB颜色空间是一种基于红绿蓝三种基本颜色的颜色空间,而CMYK颜色空间是一种基于青、洋红、黄、黑四种颜色的颜色空间。这两种颜色空间都是常用的颜色空间,但在某些应用中,CMYK颜色空间更为常用。在RGB转CMYK的过程中,首先要知道RGB值如何转换为C、M、Y三种颜色的值,然后再将这三种颜色的值转换为K值。这个过程可以通过以下公式实现:

K = 255-max([R,G,B]);

C = max([R,G,B]) - R;

M = max([R,G,B]) - G;

Y = max([R,G,B]) - B;

其中,R、G、B分别代表RGB颜色空间中的红、绿、蓝三种颜色的值,C、M、Y分别代表CMYK颜色空间中的青、洋红、黄三种颜色的值,K代表CMYK颜色空间中的黑色值。

3.2、基于FPGA的实现方法

基于FPGA的图像RGB转CMYK实现方法主要包括以下几个步骤:

输入RGB图像数据:首先需要将RGB图像数据输入到FPGA中。这个过程可以通过接口电路或者直接在FPGA中实现。

数据预处理:由于RGB图像数据通常是一个8位的整数,每个像素有三个颜色通道,因此需要对输入的数据进行一些预处理。这个过程包括将每个像素的三个颜色通道的数据合并成一个32位的整数,以便于后续的计算。

转换计算:在预处理完成后,需要对每个像素进行RGB转CMYK的转换计算。这个过程可以通过上述公式来实现。对于每个像素的每个颜色通道,都需要计算出C、M、Y三个颜色的值,然后再计算出K的值。这个过程需要在FPGA上实现一个高效的算法,以便于在短时间内处理大量的数据。

数据后处理:在转换计算完成后,需要对数据进行一些后处理。这个过程包括将每个像素的四个颜色通道的数据拆分为三个8位的整数,然后将数据输出到外部存储器或者显示设备中。

系统控制:在整个实现过程中,还需要有一个系统控制模块来控制整个系统的运行。这个模块需要根据外部输入的指令来控制整个系统的工作流程和参数设置。

4.部分核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/08/01

// Design Name:

// Module Name: RGB2gray

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test_image;

reg i_clk;

reg i_rst;

reg [7:0] Rbuff [0:100000];

reg [7:0] Gbuff [0:100000];

reg [7:0] Bbuff [0:100000];

reg [7:0] i_Ir,i_Ig,i_Ib;

wire [7:0] o_K,o_C,o_M,o_Y;

integer fids1,dat1,fids2,dat2,fids3,dat3,jj=0;

//D:\FPGA_Proj\FPGAtest\codepz

initial

begin

fids1 = $fopen("D:\\FPGA_Proj\\FPGAtest\\codepz\\R.bmp","rb");

dat1 = $fread(Rbuff,fids1);

$fclose(fids1);

end

initial

begin

fids2 = $fopen("D:\\FPGA_Proj\\FPGAtest\\codepz\\G.bmp","rb");

dat2 = $fread(Gbuff,fids2);

$fclose(fids2);

end

initial

begin

fids3 = $fopen("D:\\FPGA_Proj\\FPGAtest\\codepz\\b.bmp","rb");

dat3 = $fread(Bbuff,fids3);

$fclose(fids3);

end

initial

begin

i_clk=1;

i_rst=1;

#1200;

i_rst=0;

end

always #5 i_clk=~i_clk;

always@(posedge i_clk)

begin

i_Ir<=Rbuff[jj];

i_Ig<=Gbuff[jj];

i_Ib<=Bbuff[jj];

jj<=jj+1;

end

main_RGB2CMYK main_RGB2CMYK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_image_R (i_Ir),

.i_image_G (i_Ig),

.i_image_B (i_Ib),

.o_K (o_K),// Y

.o_C (o_C),// Y

.o_M (o_M),// Y

.o_Y (o_Y)

);

integer fout1;

initial begin

fout1 = $fopen("K.txt","w");

end

always @ (posedge i_clk)

begin

if(jj<=66616)

$fwrite(fout1,"%d\n",o_K);

else

$fwrite(fout1,"%d\n",0);

end

integer fout2;

initial begin

fout2 = $fopen("C.txt","w");

end

always @ (posedge i_clk)

begin

if(jj<=66616)

$fwrite(fout2,"%d\n",o_C);

else

$fwrite(fout2,"%d\n",0);

end

integer fout3;

initial begin

fout3 = $fopen("M.txt","w");

end

always @ (posedge i_clk)

begin

if(jj<=66616)

$fwrite(fout3,"%d\n",o_M);

else

$fwrite(fout3,"%d\n",0);

end

integer fout4;

initial begin

fout4 = $fopen("Y.txt","w");

end

always @ (posedge i_clk)

begin

if(jj<=66616)

$fwrite(fout4,"%d\n",o_Y);

else

$fwrite(fout4,"%d\n",0);

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号