基于FPGA的RGB图像转化为灰度图实现,通过MATLAB进行辅助验证

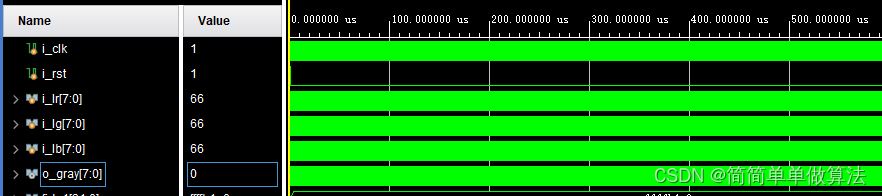

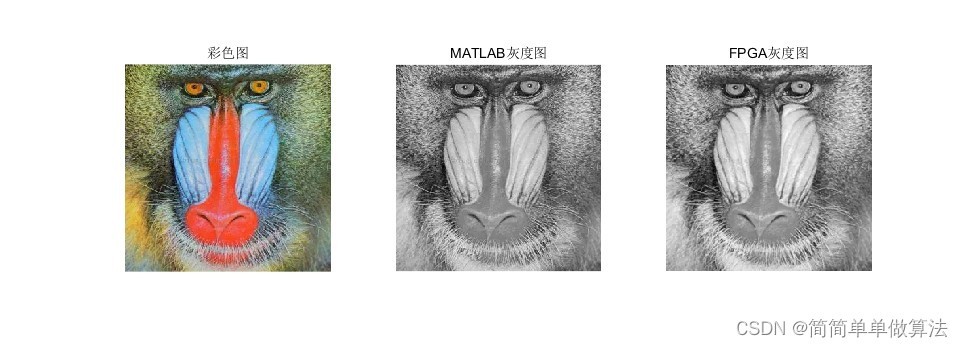

1.算法运行效果图预览

2.算法运行软件版本

vivado2019.2

matlab2022a

3.算法理论概述

基于FPGA的RGB图像转换为灰度图实现是一种在图像处理领域常见的操作。这种操作通过将彩色图像的RGB三个通道转换为单一的灰度值,使得图像处理变得更加简单和高效。

RGB图像是一种最常见的彩色图像表示方式,它由三个通道组成:红色(R)、绿色(G)和蓝色(B)。每个通道的强度范围是0到255,它们共同决定了像素的颜色。

灰度图像是一种只包含亮度信息而不包含颜色信息的图像形式。灰度图像的每个像素值都在0到255的范围内,表示像素的亮度。

将RGB图像转换为灰度图的基本原理是,通过加权平均的方法,将RGB三个通道的强度值组合成一个单一的灰度值。这样,每个像素的颜色信息就被简化为一个亮度信息,从而可以进行更简单的图像处理和分析。

将RGB图像转换为灰度的标准公式如下:

Gray = 0.2989 * R + 0.5870 * G + 0.1140 * B

这个公式的含义是,灰度值由R、G、B三个通道的加权平均值决定,每个通道的权值分别为0.2989、0.5870和0.1140。这些权值是根据人眼对不同颜色的敏感度进行设置的。

在基于FPGA的实现中,这个公式通常被转换为固定点运算的形式,以便在硬件上高效地实现。例如,可以使用如下公式:

Gray = (37 * R + 77 * G + 13 * B) / 255

这个公式的权值与前面的公式相同,但进行了整数化处理,以便在FPGA上更高效地实现。

在基于FPGA的实现中,通常使用硬件描述语言(如VHDL或Verilog)来描述和实现图像转换逻辑。具体实现步骤如下:

从外部存储器中读取RGB图像数据。

将RGB数据转换为并行的8位整数(或16位整数,取决于FPGA的位数)。

使用上述公式计算每个像素的灰度值。

将计算出的灰度值写入外部存储器中。

在实现过程中,需要注意以下几点:

由于FPGA的资源有限,因此需要优化算法和代码,以减少资源使用。

需要考虑图像的宽度和高度,以确定使用何种数据结构和算法。

需要考虑图像数据的格式和颜色空间,以正确地处理RGB数据。

需要进行测试和验证,以确保转换结果的正确性和稳定性。

基于FPGA的RGB图像转换为灰度图实现是一种常见的图像处理操作。通过使用硬件描述语言和优化算法,可以实现高效的转换过程,并且可以广泛应用于图像处理、计算机视觉和机器学习等领域。

4.部分核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/08/01

// Design Name:

// Module Name: RGB2gray

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test_image;

reg i_clk;

reg i_rst;

reg [7:0] Rbuff [0:100000];

reg [7:0] Gbuff [0:100000];

reg [7:0] Bbuff [0:100000];

reg [7:0] i_Ir,i_Ig,i_Ib;

wire [7:0] o_gray;

integer fids1,dat1,fids2,dat2,fids3,dat3,jj=0;

//D:\FPGA_Proj\FPGAtest\code

initial

begin

fids1 = $fopen("D:\\FPGA_Proj\\FPGAtest\\code\\R.bmp","rb");

dat1 = $fread(Rbuff,fids1);

$fclose(fids1);

end

initial

begin

fids2 = $fopen("D:\\FPGA_Proj\\FPGAtest\\code\\G.bmp","rb");

dat2 = $fread(Gbuff,fids2);

$fclose(fids2);

end

initial

begin

fids3 = $fopen("D:\\FPGA_Proj\\FPGAtest\\code\\b.bmp","rb");

dat3 = $fread(Bbuff,fids3);

$fclose(fids3);

end

initial

begin

i_clk=1;

i_rst=1;

#1200;

i_rst=0;

end

always #5 i_clk=~i_clk;

always@(posedge i_clk)

begin

i_Ir<=Rbuff[jj];

i_Ig<=Gbuff[jj];

i_Ib<=Bbuff[jj];

jj<=jj+1;

end

main_gray main_gray_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_image_R (i_Ir),

.i_image_G (i_Ig),

.i_image_B (i_Ib),

.o_gray (o_gray)

);

integer fout1;

initial begin

fout1 = $fopen("rgb2gray.txt","w");

end

always @ (posedge i_clk)

begin

if(jj<=66616)

$fwrite(fout1,"%d\n",o_gray);

else

$fwrite(fout1,"%d\n",0);

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号